Fターム[5J056DD28]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | P型FETとN型FETの組合せ (1,723)

Fターム[5J056DD28]の下位に属するFターム

相補動作するもの、CMOS (940)

Fターム[5J056DD28]に分類される特許

201 - 220 / 783

ドライバ装置

【課題】UVLO機能を内蔵したドライバ装置を提供する。

【解決手段】電源に接続された第1のスイッチ素子と、前記第1のスイッチ素子と直列接続された第2と、第3と、前記第3のスイッチ素子と並列接続された第4のスイッチ素子と、一端が前記第3及び第4のスイッチ素子に接続され、他端が前記第1のスイッチ素子の制御電極に接続された第1の抵抗と、前記第1の抵抗を介して前記第3のスイッチ素子の負荷となるカレントミラーと、前記カレントミラーに電流を流す放電回路と、外部から入力信号を受けて、前記第2と第3のスイッチ素子を介して前記第1のスイッチ素子と、を交互にオン、オフするように制御し、かつ、前記放電回路及び前記第4のスイッチ素子を、前記電源が立ち上がるときにオンさせて前記カレントミラーに電流を流すことにより、電源が立ち上がった後は前記第4のスイッチ素子をオフする制御回路を備える。

(もっと読む)

スイッチング出力回路およびスイッチング電源

【課題】貫通電流を防止する。

【解決手段】ハイサイドトランジスタ16およびローサイドトランジスタ18それぞれのゲート電極30、40は、異なる位置に設けられた駆動用コンタクト32(42)と検出用コンタクト34(44)を介して信号を入出力可能に構成される。ハイサイドドライバ22は、制御信号S1が第1レベルであり、かつローサイドトランジスタ18側の検出用コンタクト44の信号SLがローレベルのとき、ハイサイドトランジスタ16側の駆動用コンタクト32にローレベルを印加する。ローサイドドライバ24は、制御信号S1が第2レベルであり、かつハイサイドトランジスタ16側の検出用コンタクト34の信号SHがハイレベルのとき、ローサイドトランジスタ18側の駆動用コンタクト32にハイレベルを印加する。

(もっと読む)

CMOSバイアス回路

【課題】電源電圧の変動の影響を低減することが可能なCMOSバイアス回路を提供する。

【解決手段】CMOSバイアス回路は、起動回路と、被起動回路部と、を備え、起動電流供給部は、第1の端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され第1の電流を出力する第1の電流供給回路と、を含み、起動電流停止制御部は、内部電流をカレントミラーした停止制御電流を第1のMOSトランジスタの他端に供給し、被起動回路部は、内部電流が第1の電流値以上のときは内部電流を第2の電流値まで増加させ、起動電流が零ならば内部電流を第2の電流値で安定させ、零より大きい起動電流に応じて内部電流を第1の電流値以上に増加させる。

(もっと読む)

LVDSドライバ、LVDS回路、LVDS回路の抵抗値調整方法および電流値調整方法

【課題】基板上での回路部品のレイアウトが相違しても差動信号の適正な伝達が可能なLVDSドライバ、LVDS回路、LVDS回路の抵抗値調整方法およびLVDS回路の電流値調整方法を得ること。

【解決手段】LVDSドライバ21とLVDSレシーバ22を接続する第1の信号線21eと、第2の信号線21fの間に送信側抵抗値設定手段21gを配置して、この抵抗値をスイッチ手段のオン・オフによって適正な値に設定し、レイアウトの相違に対処できる。電流源21aの流す電流値を同様に抵抗で調整することで電流消費の低減も可能になる。

(もっと読む)

半導体集積回路

【課題】差動アンプ回路の出力信号の出力をより正確に制御することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第4のMOSトランジスタと第5のMOSトランジスタとの間の接点の第1の電圧に応じた信号とイネーブル信号とが入力され、イネーブル信号が第1のレベルであり且つ第1の電圧が規定電圧以上の場合に差動アンプ回路の出力信号を出力端子に出力するための第1の信号を出力し、イネーブル信号が第2のレベルまたは第1の電圧が規定電圧未満の場合に第2の信号を出力する演算回路と、差動アンプ回路の出力信号と演算回路が出力した信号とが入力され、第1の信号が入力された場合には、出力信号を出力端子に出力し、第2の信号が入力された場合には、出力端子へ或る論理に固定した信号を出力する出力バッファ回路と、を備える。

(もっと読む)

コンパレータ回路及びそのコンパレータ回路を備えたLVDSレシーバ

【課題】高速動作しつつ、良好な信号を出力することができるコンパレータ回路及びLVDSレシーバを提供する。

【解決手段】コンパレータ回路20を構成する増幅部52は、カスケード接続された複数のインバータ回路を有する。複数のインバータ回路53〜55のうち初段のインバータ回路53に帰還抵抗R1を設けると共に、この初段のインバータ回路53の入力ノードt1と出力ノードt2に双方向ダイオードとして機能させたトランジスタQ33,Q34を接続する。

(もっと読む)

ラッチ回路、フリップフロップ回路および半導体装置

【課題】ラッチ回路およびフリップフロップ回路のソフトエラー耐性の向上。

【解決手段】複数の回路ユニットIV1-IV4を有し、複数の回路ユニットの出力が他の反転回路の入力にフィードバックされ、2以上の入力端子1,2を有するデータ保持回路11と、2以上のクロックCK01,XCK01;CK02,XCK02にそれぞれ同期して、データ保持回路の2以上の入力端子に入力信号を入力する2以上の入力回路TG1,TG2と、を備え、データ保持回路は、2以上の入力端子に同時に入力信号Dinが入力されかつ2以上のクロックが同時に変化した時のみ、2以上の入力端子に正帰還がかかる。

(もっと読む)

コンパレータ回路

【課題】出力電圧信号の振幅を十分にとれない場合があった。

【解決手段】本発明は、参照電圧を入力する第1、第2の端子と、基準電圧を入力する第3の端子と、検出すべき電圧を入力する第4の端子と、参照電圧の電位差に応じた電流をそれぞれ流す第1、第2のトランジスタ(以下、Tr)と、第1のTrと直列接続される第3のTrと、第2のTrと直列接続される第4のTrと、第3のTrの流す電流に応じたミラー電流を流す第5のTrと、第4のTrの流す電流に応じたミラー電流を流す第6のTrと、第6のTrと第4の端子との間に接続される第7のTrと、第5のTrと第3の端子との間に接続され、第7のTrの流す電流に応じたミラー電流を流す第8のTrと、を有し、第5、第8のTrの中間ノードの電圧に応じた電圧を出力信号として出力するコンパレータ回路である。

(もっと読む)

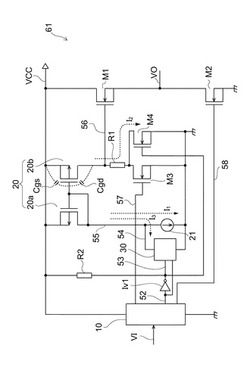

出力回路およびモータ駆動装置

【課題】パワートランジスタの誤動作を防止する。

【解決手段】パワートランジスタM1は、出力端子POUTと電源端子PVCCの間に設けられる。プリドライバ10は、電源端子PVDDと第2端子P2の間に直列に接続され、制御信号S1に応じて相補的にオン、オフが制御されるハイサイドトランジスタM2およびローサイドトランジスタM3を含み、2つのトランジスタの接続点の電位を、パワートランジスタM1の制御端子に出力する。定電圧回路20は、第2端子P2を所定の電圧VL(=Vref)に安定化させる。定電圧回路20の出力トランジスタM4は、第2端子P2と接地端子PGNDの間に設けられる。差動アンプ24は、第2端子P2の電位VLが所定の目標値Vrefに近づくように、出力トランジスタM4の制御端子の電圧Vg4を調節する。フィードバックキャパシタC1は、第2端子P2と出力トランジスタM4の制御端子の間に設けられる。

(もっと読む)

差動ドライバー回路の高速コモンモードフィードバック制御装置

出力バッファを迅速に安定化するシステム及び方法。差動駆動回路は、差動入力信号を受け取り、該入力信号に基づいて差動出力を生成する増幅段を備える。差動出力は、通常は電源の2分の1の値に基づいた対応するコモンモード(CM)電圧レベルを有する。コモンモード・フィードバックバッファ(CMFB)段は、CM電圧レベルの変化を検出し、当該CM電圧レベルを、超高速バス周波数に基づく超高速整定時間内の所望の値に回復させる。CMFB段は、単一のデバイスだけを備えたトポロジーを利用する。1つの実施形態において、この単一デバイスは、トランスインピーダンス段として利用されるNMOSトランジスタである。回路バイアス段及びCMFB段内のシャントキャパシタによって安定性が提供される。 (もっと読む)

記憶体制御器及び復号器

【課題】ゲート誘導ドレーン漏れ電流を下げることができる記憶体制御器及び復号器を提供する。

【解決手段】本発明は記憶体制御器及び復号器を提供する。復号器は第一乃至第四トランジスタを含む。第一乃至第四トランジスタのゲートはそれぞれ第一乃至第四制御信号に接続される。第一トランジスタの第一端と第二端はそれぞれ第一電圧と第二トランジスタの第一端に接続される。第三、第四トランジスタの第一端と第二端はそれぞれ第二トランジスタの第二端と第二電圧に接続される。第一、第二トランジスタがオフされるときは、第二制御信号の電圧が第一制御信号の電圧より小さい。これにより、ゲート誘導ドレーン漏れ電流を下げることができる。

(もっと読む)

スタートアップ回路

【課題】必要とするキャパシタの数を削減し、且つ電源電圧が低下しても基準電圧回路から出力する基準電圧の変動を防止できるようにする。

【解決手段】電源投入時に定電流回路10に起動電流を供給するキャパシタC1と、該キャパシタC1に流れる起動電流を入力しそのミラー電流が出力するカレントミラー回路(MN31,MN32)とを設ける。そして、該カレントミラー回路の出力電流を基準電圧回路20に起動電流として供給する。

(もっと読む)

半導体集積装置

【課題】基盤電位をモニターして、確実にラッチアップをリセットできる機能を有する半導体集積装置を提供する。

【解決手段】第1導電型の半導体基板11の第2導電型のウェル層12に形成された第1チャネルMOSトランジスタP1と、半導体基板11に形成され、基準電位GNDに接続された第2導電型の半導体層14と、半導体基板11の基盤電位VEEと基準電位GNDとの電位差をモニターし、不純物拡散層13aと、ウェル層12と、半導体基板11と、半導体層14とにより付随的に形成される寄生サイリスタが導通することにより生じるラッチアップを検出するための検出手段15と、基準電位GNDと基盤電位VEEとの間に接続され、検出手段15の出力信号Voutに応じて基準電位GNDと基盤電位VEEとを同電位にし、寄生サイリスタの導通を阻止してラッチアップを解消するためのスイッチ手段16と、を具備する。

(もっと読む)

半導体集積装置

【課題】I2Cバスインターフェイスを介して高電源電圧の半導体集積装置からのデータ

を確実に受信できる信号入力回路を備えた低電源電圧の半導体集積装置を提供する。

【解決手段】第1電圧V1または第1電圧V1より高い第2電圧V2の振幅を有する第1

信号S1がやり取りされる信号線11に接続され、第1信号S1を第1電圧V1より低い

第3電圧V3の振幅を有する第2信号S2に変換して出力する電圧変換回路12と、第1

入力端子13aに第2信号S2が入力され、第2入力端子13bに基準電圧Vrefが入

力され、第2信号S2を基準電圧Vrefと比較して、出力電圧Voutを出力するコン

パレータ13と、第1基準電圧Vref1および第2基準電圧Vref2を生成し、出力

電圧Voutに応じて第1基準電圧Vref1または第2基準電圧Vref2を選択し、

基準電圧Vrefとして出力する基準電圧発生回路14と、を具備する。

(もっと読む)

集積回路装置、及び電子機器

【課題】 グランド端子がオープン状態となった場合であっても、グランド端子以外の端子の電位に応じて、内部回路の動作/非動作が決定されてしまうような不都合が生じないようにする。

【解決手段】 集積回路装置は、内部回路200と、グランド端子TGと、内部回路が動作している期間の少なくとも一部の期間においてグランドレベルとなる第1信号SG1が供給される第1端子T1と、第1端子T1の電圧と、グランド端子TGの電圧とを比較することによって、グランド端子TGのオープン状態を検出する検出回路20と、検出回路20によってグランド端子TGのオープン状態が検出されると、内部回路200をリセットまたはディスエーブル状態に設定する設定回路30と、を含む。

(もっと読む)

プリドライバ及びこれを用いた出力ドライバ回路

【課題】出力ドライバ回路の提供

【解決手段】プルアップコード信号、プルダウンコード信号、プリドライバ選択信号及びリード制御信号を受信してプルアップ制御信号及びプルダウン制御信号を生成するプリドライバ制御信号生成部と、前記プルアップ制御信号及び前記プルダウン制御信号に応答して駆動され、内部データを受信してプルアップ駆動信号及びプルダウン駆動信号を駆動するプリドライバと、前記プルアップ駆動信号及び前記プルダウン駆動信号を受信して、DQパッドに出力される出力データを駆動するドライバと、を含んでなり、前記プルアップ制御信号及び前記プルダウン制御信号は、リード動作区間で前記プリドライバが選択され、既設定された前記コード信号の組合せが入力される場合にイネーブルされる構成とした。

(もっと読む)

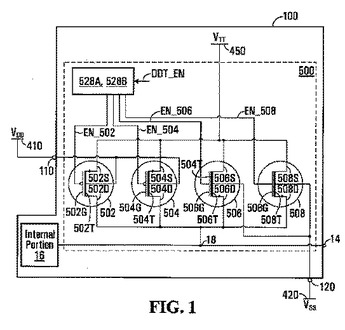

オンダイ終端のための終端回路

内部部分に接続されている端子を有する半導体デバイスにおいて、そのデバイスの端子用のオンダイ終端を提供するための終端回路。この終端回路は、端子と電源の間に接続された、少なくとも1つのNMOSトランジスタおよび少なくとも1つのPMOSトランジスタを含む複数のトランジスタと、NMOSトランジスタのそれぞれのゲートを対応するNMOSゲート電圧でドライブし、PMOSトランジスタのそれぞれのゲートを対応するPMOSゲート電圧でドライブするための制御回路であって、オンダイ終端が有効である場合にトランジスタを動作のオーム領域におくようにNMOSゲート電圧およびPMOSゲート電圧を制御するように構成されている、制御回路とを含む。電源は、上記NMOSゲート電圧のそれぞれより小さく、上記PMOSゲート電圧のそれぞれより大きい電圧を供給する。  (もっと読む)

(もっと読む)

半導体装置

【課題】出力バッファのインピーダンス調整を行う半導体装置を提供する。

【解決手段】制御回路1は、外部からの読み出しまたは書き込みコマンドに応じてDQイネーブル信号を発生する。コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を始める。ZQ調整回路3は、DQイネーブル信号が入力される期間中は、インピーダンス調整結果であるドライバコードのDQ回路4への出力を禁止する。

(もっと読む)

半導体装置及びそのスルーレート制御方法

【課題】インピーダンス不整合を生じさせることなく、シンボル間干渉によるデータウィンドウの悪化を防止し、安定した高速動作を実現する。

【解決手段】半導体装置は、シリアルデータのデータ間論理比較を行って比較結果を生成する比較手段と、前記シリアルデータに基づいて生成される出力信号のスルーレートを、前記比較結果に基づいて制御するスルーレート制御手段と、を有している。

(もっと読む)

レベルコンバータ回路

【課題】高速で省電力のレベルコンバータ回路を提供する。

【解決手段】基準電圧にそれぞれのソースが接続され入力信号とその反転信号である反転入力信号とがそれぞれのゲートに供給される第1及び第2の第1導電型トランジスタを有し,基準電圧と前記高電源電圧とを有する第1の信号とその反転信号である第1の反転信号とを生成する論理反転部と,低電源電圧にそれぞれのソースが接続され第1の信号と第1の反転信号とがそれぞれのゲートに供給される第3及び第4の第2導電型トランジスタを有し,第3または第4の第2導電型トランジスタが導通して出力端子に出力信号の前記高電源電圧を生成する信号出力部と,第1及び第2の第1導電型トランジスタと第3及び第4の第2導電型トランジスタとの間にそれぞれ設けられた第5及び第6のトランジスタを有するスイッチ部とを有する。

(もっと読む)

201 - 220 / 783

[ Back to top ]