Fターム[5J056DD53]の内容

Fターム[5J056DD53]の下位に属するFターム

配線のインダクタンス (12)

Fターム[5J056DD53]に分類される特許

1 - 20 / 57

集積回路装置

【課題】断熱動作を行う回路への電源電圧の供給を最適化することで好適な動作特性を実現する。

【解決手段】集積回路装置が、CPU10と電源生成回路40とを具備している。当該集積回路装置が高速モードに設定されると、電源生成回路40が直流の電源電圧をCPU10に供給する。この場合、CPU10は、通常のCMOS動作を行う。一方、当該集積回路装置が小電力モードに設定されると、電源生成回路40が交流の電源電圧をCPU10に供給する。CPU10は、複数の交流の電源電圧が供給されることで断熱動作を行う。該交流の電源電圧の少なくとも2つの電源電圧は、互いに、プルアップ及び/又はプルダウンのタイミングと、デューティ比とが異なっている。

(もっと読む)

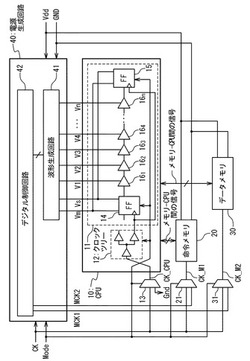

デジタルアイソレータおよびフィールド機器

【課題】低消費電力化を図る。

【解決手段】入力側電源3と1次側回路1との間にスイッチ部6を設け、従来は1次側回路1の入力信号端子TINに与えるようにしていた入力信号DINをスイッチ部6へ与えるようにし、入力信号DINのレベルに応じてスイッチ部6のオン/オフを行わせるようにする。また、入力信号端子TINには入力信号DINに代えて、1次側回路1への電源電圧VDD1の供給遮断時に強制的に固定される2次側回路2からの出力信号DOUTのレベルとは逆のレベルの信号(出力信号「H」強制固定の場合は「L」レベルの信号、出力信号「L」強制固定の場合は「H」レベルの信号)を与えるようにする。

(もっと読む)

小振幅差動パルス送信回路

【課題】最適の時期に出力電流を流して、それ以外の時期には出力電流を止めることによって省エネ性能に優れた小振幅差動パルス送信回路を提供すること。

【解決手段】定電流を送信データに応じて差動的に出力する定電流差動出力回路101と、前記定電流差動出力回路101の出力を、送信データの値の変化による該出力の過渡現象が収束した後であって次のデータが出力される前における所定期間通過させるスイッチ回路102と、前記スイッチ回路102の出力を所定電位にバイアスするバイアス回路103とを備える小振幅差動パルス送信回路。

(もっと読む)

電子回路、および実装基板

【課題】出力信号の電圧レベルの遷移の方向に応じて、電源線や接地線を通らず寄生インダクタンス成分の影響を受けない電流を加算して信号の電圧レベルの遷移をアシストすることにより、SSOノイズを抑制することが可能な電子回路および実装基板の制御方法を提供すること。

【解決手段】出力回路1は、出力バッファ4と、出力バッファ4から出力される出力信号が伝搬する出力線と、出力バッファ4に電源を供給する電源線VdeLあるいは接地線VgLの少なくとも何れか一方と、出力線と電源線VdeLあるいは接地線VgLとにより囲まれる磁心50と、磁心50に巻回される制御コイル51と、出力信号の遷移を前もって検出し検出結果に応じて制御コイル51への電流供給を制御するコイル電流制御回路3とを備え、出力信号の遷移方向に応じて、制御コイル51からの電磁誘導により出力線の信号遷移をアシストするアシスト電流を流す。

(もっと読む)

電源回路、回路装置及び電子機器

【課題】安定な断熱的回路動作を実現し、消費電力を抑制することができる電源回路、回路装置及び電子機器等を提供すること。

【解決手段】電源回路200は、第1の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第1の電源電圧VPと、第2の基準電圧を基準として電圧が周期的に変化する、断熱的回路動作用の第2の電源電圧VMとを出力する電圧出力回路100と、制御信号SCに基づいて電圧出力回路100を制御する制御回路210と、第1の電源電圧VP及び第2の電源電圧VMに基づいて制御信号SCを生成して制御回路210に出力する制御信号生成回路240とを含み、制御回路210は、制御信号SCに基づいて、電圧出力回路100から出力される第1の電源電圧VP及び第2の電源電圧VMの振幅を可変に制御する。

(もっと読む)

インターフェース回路

【課題】ノイズを低減することができるインターフェース回路を提供することを課題とする。

【解決手段】インターフェース回路は、電源電圧端子が第1の電源電圧ノードに接続され、入力信号を増幅する第1のバッファ(111)と、第2の電源電圧ノード及び前記第1のバッファの電源電圧端子間に接続されるスイッチ(124)と、前記第1のバッファの入力信号がローレベルからハイレベルに立ち上がると、遅延時間経過後に前記スイッチをオフからオンに切り換える第1の制御回路(127)とを有する。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

クロックバッファ回路及びこれを用いたクロック分配回路

【課題】小さな回路規模により広帯域のクロック信号に対応できるクロックバッファ回路を提供すること。

【解決手段】本発明の一態様であるクロックバッファ回路100は、ドライバ部11及びLCタンク部21を有する。ドライバ部11は、クロック入力IN及びINBからの入力クロック信号の少なくとも正転出力を、それぞれクロック出力OUT及びOUTBへ出力する。LCタンク部は、ドライバ部11とクロック出力OUT及びOUTBとの間に配置される。ドライバ部11は、入力クロック信号の周波数に対応した制御信号に応じて、ドライバ部11の入力と出力とを短絡させるスイッチSW1及びSW2を有する。

(もっと読む)

通信モジュール、リーダライタ

【課題】部品を内蔵できる配線板を有する通信モジュールであって、アンテナの特性に応じて整合の調整が可能な通信モジュールおよびこれを用いたリーダライタを提供すること。

【解決手段】配線板と、配線板に備えられた通信処理用ICと、通信処理用ICに電気的に接続されて配線板に備えられた、外部に設けられるアンテナとの整合をとる整合回路と、を具備し、整合回路が、キャパシタまたはインダクタを少なくとも含む受動素子回路網の回路であり、該受動素子回路網を構成する回路エレメントのうちの少なくともひとつが、配線板に内蔵された第1の受動素子部品と、配線板の面上に実装された、該第1の受動素子部品と同じ種の受動素子部品である第2の受動素子部品との並列接続または直列接続でできた回路エレメントである。

(もっと読む)

半導体集積回路及び半導体集積回路の電源制御方法

【課題】製造プロセス条件の変動に関わらず短い電源立ち上げ時間を確保することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の電源線と第2の電源線との間に並列に配置された複数の電源スイッチと、複数の電源スイッチを設定時間間隔で順次導通させる駆動回路と、第2の電源線と第3の電源線との間に配置される内部回路と、第2の電源線と第3の電源線との間の電圧が上昇して所定値に到達すると検知信号をアサートする昇圧検知回路と、検知信号のアサート時において導通状態にある複数の電源スイッチの数に応じて設定時間間隔を変化させる制御回路とを含む。

(もっと読む)

レベルシフト回路及びそれを用いたスイッチングレギュレータ

【課題】電源電圧を高くしてもトランジスタのゲート耐圧を上げる必要がなく、低電源電圧から高電源電圧まで広範囲に使用できるレベルシフト回路を提供する。

【解決手段】レベルシフトトランジスタ105は、入力トランジスタ101と負荷トランジスタ103との間に、レベルシフトトランジスタ106は、入力トランジスタ102と負荷トランジスタ104との間にそれぞれ接続される。レベルシフトトランジスタ105,106の各ゲートGは共通接続され、その共通接続点にはレベルシフト電圧生成回路120で生成されたレベルシフト電圧Vscが電圧源V1の大きさに応動して印加される。負荷トランジスタ103,104のソース−ゲート間に印加される電圧VSGは、レベルシフト電圧Vscによって、電圧源V1が増減してもほぼ一定になるように設定される。これにより、負荷トランジスタ103,104を低耐圧のトランジスタで構成することができる。

(もっと読む)

回路装置、電子機器及び電源回路

【課題】実装面積を削減できる回路装置、電子機器及び電源回路等を提供すること。

【解決手段】回路装置は、共振回路を有する電源回路と、論理回路と、を含む。共振回路は、第1のコイルL1と、第1のコイルL1とコア部を共有する第2のコイルL2と、を有する。論理回路は、共振回路により生成された電源電圧VP、VMが供給されることで断熱的回路動作を行う。

(もっと読む)

圧電アクチュエータ用のドライバ

【課題】複数の半導体デバイスを使用する電池駆動のドライバと同程度に効率的な圧電アクチュエータ用のシングルチップドライバを提供する。

【解決手段】圧電アクチュエータ用のドライバは、単一の半導体デバイスとしてパッケージされる、好ましくは単一の半導体ダイの上に形成されるパルス幅変調器33および出力増幅器34を含む。ドライバは、好ましくはプログラム可能な利得を有する出力増幅器34に電力を供給する第1の昇圧コンバータを含む。第1の昇圧コンバータのスイッチングトランジスタのゲートを駆動するための第2の増幅器は、第2の昇圧コンバータによって電力が供給される。圧電アクチュエータ22は、電池駆動の電子デバイスのキーボードまたはディスプレイに対して触覚フィードバックを提供する。

(もっと読む)

RFID用リーダ装置及びその制御方法

【課題】直流遮断コンデンサを用いるリーダ装置の送受信の切り替え待機時間を短縮する。

【解決手段】リーダ装置2は、RFID3に対し、高周波搬送波信号を送信する送信回路4と、送信回路5により送信された高周波搬送波信号から、RFID3の応答データを抽出する受信回路5とを備え、受信回路5は、高周波搬送波信号を検波する検波回路14と、検波回路14による検波後の高周波搬送波信号の信号処理を行い、RFID3の応答データを取得する信号処理回路18と、検波回路14と信号処理回路18とを接続する配線に間挿された直流遮断コンデンサ15と、直流遮断コンデンサ15と直列に接続され、オフのときに直流遮断コンデンサ15の少なくとも一方の端子をオープンとするスイッチ素子16とを有することを特徴とする。

(もっと読む)

送信ドライバ回路

【課題】フリーホイールダイオードを用いることなく、より低い電圧のアンダーシュートでも低減できる送信ドライバ回路を提供する。

【解決手段】PチャネルMOSFET22のドレインをグランドに接続して、NチャネルMOSFET21,PチャネルMOSFET22のソースをそれぞれ信号線3H,3Lに接続する。第1データ電圧設定部41は、信号出力部がハイレベル信号を出力すると、ゲート21G,22G間の電位差を(2・R1・Iref)にする電圧信号を設定し、第2データ電圧設定部42は、信号出力部がロウレベル信号を出力すると、ゲート21G,22G間の電位差をゼロにする電圧信号を設定する。これらの作用により、伝送線路3を構成する信号線3H,3L間の電圧を変化させて差動信号を伝送する。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】断熱的回路動作と非断熱的回路動作を切り替え可能である回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、論理回路200と、電源回路100と、を含む。第1のモードでは、電源回路100は、非直流の電源電圧VPK、VMKを論理回路200に供給し、論理回路200は、その非直流の電源電圧VPK、VMKが供給されることで断熱的回路動作を行う。第2のモードでは、電源回路100は、直流の電源電圧VDD、VSSを論理回路200に供給し、論理回路200は、その直流の電源電圧VDD、VSSが供給されることで非断熱的回路動作を行う。

(もっと読む)

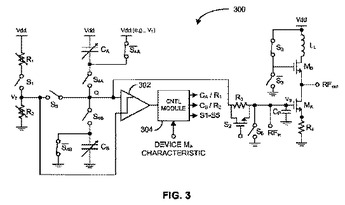

アクティブデバイスをバイアスするシステム及び方法

アクティブデバイスに対するバイアス電圧を発生する装置が開示され、第1の電圧源と、第1の電圧源に応答してチャージを発生するように適応されたキャパシティブエレメントと、アクティブデバイスに対するバイアス電圧を発生するためにチャージを供給するように適応された第1のスイッチングエレメントとを備える。本装置は、アクティブデバイスの1以上の特性に基づいてキャパシティブエレメントをコントロールするように適応されコントローラを備えるかもしれない。コントローラは、リファレンス電圧に基づいて、すなわちアクティブデバイスの1以上の特性に基づいて前記キャパシティブエレメントのキャパシタンスをコントロールかもしれない。  (もっと読む)

(もっと読む)

集積回路

【課題】積層実装されるチップ間で誘導結合による通信を行う集積回路において低電圧・低消費電力で動作し、小面積でレイアウトできる送信回路を備える集積回路を提供すること。

【解決手段】送信コイルL1、L2を2つにして、同心かつ電源VDDに接続される端子から他端への巻き方向が互いに逆になるように配置する。この送信コイルL1、L2にそれぞれ、ソースが接地されるNMOST1、T2のドレインを接続して、送信データTxdata及びその反転信号によって駆動する。

(もっと読む)

送信回路

【課題】プリエンファシスと非プリエンファシスの2状態のデータを出力する送信回路において、データ変化点の波形のエッジに起因する電源変動、及びプリエンファシスと非プリエンファシスに起因する電源変動を抑制する。

【解決手段】図Aに示す第1回路、図Bに示す第2回路からなる。第1回路の第1回路の入力回路601g〜jには第1信号601n,601qと第1プリエンファシス信号601p,601rが入力される。第2回路の入力回路602g〜jには第2信号602n,602qと第2プリエンファシス信号602p,602rが入力される。第2信号は第1信号が変化するときは変化せずに、第1信号が変化しない時は変化する。第1回路の出力回路601a,601bと第2回路の出力回路602a,602bのどちらかがプリエンファシス状態となるので、出力回路全体で流れる電流値は一定となる。

(もっと読む)

複合電子回路アセンブリ

複合電子回路アセンブリは、パッケージ内で重ね合わされた2つのMOS又はCMOS回路ダイ(100、200)を備える。回路アセンブリの異なるモジュールは、前記モジュールのデジタル、アナログ又はハイブリッドの特性に基づいて2つのダイに分散配置される。そのような分散配置により、回路アセンブリのデジタルモジュールを一方のダイに集め且つアナログ又はハイブリッドモジュールを他方のダイに集めることができる。従って、回路アセンブリの生産コスト、開発時間及び消費電気エネルギーが縮小されてもよい。 (もっと読む)

1 - 20 / 57

[ Back to top ]