Fターム[5J079FB05]の内容

電気機械共振器を用いた発振回路 (23,106) | 回路要素 (2,263) | 記号又は抵抗一本の定電流源 (47)

Fターム[5J079FB05]に分類される特許

1 - 20 / 47

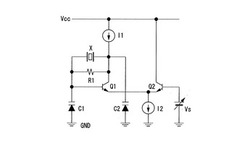

電圧制御発振回路

【課題】従来回路で必要とされてきた直流カット用の固定容量素子を削除し、また可変容量素子も小さくできるようにして、半導体集積回路の面積を削減できるようにする。

【解決手段】トランジスQ1のコレクタ・ベース間に帰還抵抗R1と水晶振動子Xを並列接続し、トランジスQ1のコレクタとVccの電源端子間に電流源I1を接続し、トランジスタQ1のベースと接地間に可変容量素C1を接続し、トランジスタQ1のコレクタと接地間に可変容量素子C2を接続し、トランジスタQ1のエミッタにトランジスタQ2のエミッタを接続し、トランジスタQ1,Q2の共通エミッタと接地間に電流源I2を接続し、トランジスタQ1のベースに制御電圧Vsを印加するようにした。

(もっと読む)

振動子ユニット、発振回路及び受信回路

【課題】共振子を接続して発振回路を完成するように設計された集積回路に、温度補償を得るためにTCXOを接続すると消費電力が大きくなる。

【解決手段】振動子ユニット20は水晶振動子Xtalを含んで一体に構成され、Xtalの両端子を外部回路に接続するための外部接続端子N1,N2を備える。振動子ユニット20は、Xtalに接続された可変容量キャパシタCVと、CVの容量を制御する温度補償部28とを有する。温度補償部28はXtalの近傍における温度を検知する温度センサ回路30を備え、振動子ユニット20の外部からのトリガ信号の入力に応じて、温度センサ回路30の検知出力に基づいてCVの容量を調節する。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

水晶発振回路

【課題】反転電圧VTH、負性抵抗−RL、発振周波数f0が電源VDDの影響を受けることがなく、定電圧回路を追加する必要がなく、しかも、動作電圧も低くなり、水晶振動子に流れる電流も小さくすることができる発振回路を提供する。

【解決手段】NMOSインバータIVnと、帰還抵抗Rfと、水晶振動子Qzと、が互いに並列接続され、NMOSインバータIVnの入力と電源VSSとの間にキャパシタCGが接続され、NMOSインバータIVnの出力と電源VSSとの間にキャパシタCDが接続された水晶発振回路1において、NMOSインバータIVnが、電源VDDに接続された定電流回路Inと、定電流回路Inと電源VSSとの間に接続されたn型のMOSトランジスタTnと、から構成されている。

(もっと読む)

水晶発振装置および半導体装置

【課題】低負荷容量値対応の水晶振動子を十分に適用することが可能な水晶発振装置を提供する。

【解決手段】例えば、配線基板PCB上に、発振入力信号XIN用の配線パターンLN_XINと、発振出力信号XOUT用の配線パターンLN_XOUTを設け、その間の領域に接地電源電圧VSS用の配線パターンLN_VSS1bを配置する。LN_XINとLN_XOUTの間には水晶振動子XTALを接続し、その負荷容量となる容量Cg,Cdの一端をLN_VSS1bに接続する。更に、これらの配線パターンを囲むようにVSS用の配線パターンLN_VSS1aを配置し、加えて、下層にもVSS用の配線パターンLN_VSSnを配置する。これらによって、XINノードとXOUTノード間の寄生容量の低減や、当該ノードのノイズ耐性の向上等が可能になる。

(もっと読む)

発振装置および該発振装置を具備したクロック発生装置、半導体装置、ならびに電子装置

【課題】過渡的な電力消費をしないピークホールド回路(あるいはボトムホールド回路)を用いることで、無駄な電力消費を抑えるとともに、ノイズの発生を抑えて発振特性の悪化を防止することが可能な発振装置技術を提供。

【解決手段】基準電圧を発生する定電圧発生回路4と、駆動電圧または駆動電流によって発振する発振回路1と、発振回路1の出力である発振信号のピークレベルを検出して出力するピークホールド回路2と、定電圧発生回路4で発生された基準電圧VREFとピークホールド回路2で出力されたピークレベルPHに応じて駆動電圧または駆動電流を増減させて発振回路1の電源端子VRに入力するレギュレータ3からなる。ピークホールド回路2は定電流で動作し過渡的な電力を消費しない構成となっている。なお、ピークホールド回路2の代わりにボトムホールド回路を用いても良い。

(もっと読む)

発振回路

【課題】周波数の校正を簡単に且つ高精度に可能な発振回路の提供。

【解決手段】圧電振動子4の両端に接続された入力端子と出力端子を有する第1のインバータ回路1と,第1のインバータ回路の入出力端子間に設けられた第1のフィードバック抵抗3と,第1のインバータ回路の入出力端子に各々接続され,制御信号により容量値が可変設定可能な第1、第2の可変容量素子2a、2bと,所定基準電流を入力端子又は出力端子に供給して第1または第2の可変容量素子を充電する充電回路10と,入力端子又は出力端子の充電電圧と,参照電圧VRとを比較する比較器11と,キャリブレーション時に,第1の時間で,充電回路に入力端子又は出力端子への基準電流の供給を開始させ,第1の時間後の第2の時間での比較器の比較結果に応じて,充電電圧が参照電圧に近づく様に,第1又は第2の可変容量素子の容量値を設定する制御信号生成の制御回路12とを有する発振回路。

(もっと読む)

水晶発振回路

【課題】出力波形の歪みを低減する水晶発振回路を提供する。

【解決手段】正・負電源ライン間に接続されたnMOSM4・pMOSM5と、nMOSM4・pMOSM5にバイアスを与えるnMOSM2・pMOSM3と、nMOSM4・pMOSM5の中心点と正・負電源ライン間に接続されたキャパシタC22・C24と、正・負電源ライン間に接続されたnMOSM14・pMOSM15と、nMOSM14・pMOSM15にバイアスを与えるnMOSM12・pMOSM13と、nMOSM14・pMOSM15の中心点と正・負電源ライン間に接続されたキャパシタC23・C25と、nMOSM2・pMOSM3の中心点とnMOSM12・pMOSM13の中心点との間に接続された水晶振動子X1とを備える。

(もっと読む)

温度補償圧電発振器及びその周波数調整方法

【課題】温度上昇や温度下降の際の温度変化に対する周波数のヒステリシスが少なく安定した周波数温度特性が得られる温度補償圧電発振器及びその周波数調整方法を提供すること。

【解決手段】第1のメモリー30と第2のメモリー40には、それぞれ、圧電振動子80の温度上昇時、温度下降時における周波数温度特性を特定するための第1、第2の温度補償データ32、42が記憶される。温度変化検出回路10は、温度センサー50が取得した温度情報に基づいて温度上昇と温度下降のいずれかが生じたかを検出する。セレクター20は、温度変化検出回路の検出結果に基づいて、温度上昇時、温度下降時にそれぞれ第1、第2の温度補償データを選択する。温度補償電圧発生回路60は、セレクターにより選択された第1又は第2の温度補償データに基づいて、温度補償電圧62を発生させる。電圧制御発振回路70は、温度補償電圧に基づいて圧電振動子の周波数を制御する。

(もっと読む)

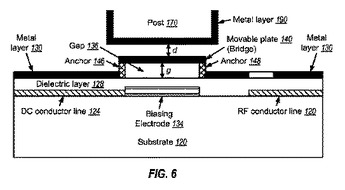

キャビティ内の調整可能なMEMS共振器

調節可能な共振周波数を有し、大きな信号を扱うことができる調整可能なMEMS共振器が説明される。1つの例示的設計では、調整可能なMEMS共振器は、(i)キャビティおよび支柱を有する第1の部分と、(ii)支柱の下に配置された可動プレートを含み、第1の部分と対になった第2の部分とを含む。各部分は、もう一方の部分と対向する表面上を金属層で覆われていてもよい。MEMS共振器の共振周波数を変化させるために、可動プレートを、直流電圧で機械的に動かすことができる。キャビティは、長方形または円形の形状を有してもよく、空であっても、誘電材料で満たされていてもよい。支柱は、キャビティの中央に位置してもよい。可動プレートは、第2の部分に、(i)1つのアンカーによって取り付けられて片持ち梁として働いてもよく、あるいは、(ii)2つのアンカーによって取り付けられてブリッジとして働いてもよい。  (もっと読む)

(もっと読む)

発振回路

【課題】デューティの設計値に対して、発振信号の振幅や周波数の変化に依存したズレが生じない、デューティ調整部を有する発振回路を提供することを目的とする。

【解決手段】発振回路は、発振部からの第1の発振信号が入力され、この第1の発振信号の振幅及び周波数に依存しない立ち上がり及び立下り時間を持つ第2の発振信号を生成する第1の差動回路と、第2の発振信号が入力され、バイアス電圧源から与えられる電圧に依存したデューティを持つ第3の発振信号を生成する第2の差動回路とを有する。

(もっと読む)

温度センサ及びこの温度センサを有する発振回路

【課題】電源電圧を低電圧とした場合でも、雑音を低減させることが可能な温度センサ及びこの温度センサを有する発振回路を提供することを目的とする。

【解決手段】電源電圧が供給される定電流源とアノードが接続されており、接地にカソードが接続された温度検出素子と、前記温度検出素子のアノードの電圧のレベルをシフトする温度特性を有したレベルシフト回路と、前記レベルシフト回路の出力が非反転入力端子と接続された非反転増幅回路と、を有する構成により実現する。

(もっと読む)

発振回路

【課題】発振バッファに過電圧が印加されるのを防止することができる発振回路を提供する。

【解決手段】発振回路10は、PTAT電流源12と、共振回路46と並列接続された発振バッファ14と、帰還抵抗Rfと、スイッチ素子54と、発振バッファ14と同一構成のレプリカバッファ52と、発振バッファ14の入力電圧を検知し、検知した入力電圧が発振時のバイアス電位よりも所定電位以上上昇した場合、及び、検知した入力電圧が発振時のバイアス電位よりも所定電位以下に下降した場合に、PTAT電流源12と発振バッファ14との接続点のノードVCCOSCの電位が発振バッファ14のPMOSトランジスタ42の耐圧を越えないように、PTAT電流源12からの電流をレプリカバッファ52回路にバイパスさせるための制御信号をスイッチ素子54手段に出力するレベル検知回路50と、を備える。

(もっと読む)

圧電発振器

【課題】圧電発振器にスリープモードを備える。

【解決手段】圧電振動子100を発振させた発振信号Vpを出力する発振回路110と、発振回路110に電流Idを供給する電流源回路120と、発振回路110から出力された発振信号Vpを整形した出力信号OUTを出力するバッファ回路130と、スリープモードとノーマルモードとを切り替える制御信号SLを入力する制御端子140と、を含み、電流源回路120は、制御信号SLがスリープモードの時はノーマルモードの時に比べて発振回路110に供給する電流Idが少なくなるように切り替える第1の切替部124を含み、バッファ回路130は、制御信号SLがスリープモードの時はバッファ回路130を構成する素子への電流の供給を止める第2の切替部132と、制御信号SLがスリープモードの時は発振信号Vpが出力されないように切り替える第3の切替部133と、を含む圧電発振器1。

(もっと読む)

圧電発振器

【課題】ピアース型圧電発振器で高い周波数出力を可能にする。

【解決手段】圧電振動子10の一方の端子と接地電位線GNDとの間に接続された第1の容量素子C1と、圧電振動子10の他方の端子と接地電位線GNDとの間に接続された第2の容量素子C2と、コレクタ端子が圧電振動子10の一方の端子に接続されベース端子が圧電振動子10の他方の端子と電流源20とに接続されエミッタ端子が接地電位線GNDに接続された発振用トランジスタQ1と、ベース端子が発振用トランジスタQ1のコレクタ端子に第1の抵抗Rbを介して接続されコレクタ端子が発振用トランジスタQ1のコレクタ端子に第2の抵抗Rcを介して接続されエミッタ端子が発振用トランジスタQ1のベース端子に接続された発振補助用トランジスタQ2と、を含んで構成される発振回路101と、発振用トランジスタQ1のコレクタ端子に接続されたバッファ回路BUFと、を含む圧電発振器1。

(もっと読む)

半導体集積回路

【課題】発振回路において発振動作が行われているか否かを判定する発振停止検出回路を内蔵した半導体集積回路において、電源電位が立ち上がる際の誤検出を防止する。

【解決手段】この半導体集積回路は、クロック信号又は反転クロック信号がゲートに印加されて交互にオン/オフする複数のトランジスタが直列に接続され、第1の電源電位から正の電荷を移送するトランジスタ列と、複数のトランジスタによって移送される電荷を蓄積する複数のコンデンサと、最終段のコンデンサの端子をプルダウンするプルダウン素子と、最終段のコンデンサの端子の電位がゲートに印加され、第2の電源電位がソースに供給されるNチャネルMOSトランジスタと、該NチャネルMOSトランジスタのドレインをプルアップするプルアップ素子と、該NチャネルMOSトランジスタのドレイン電位に基づいて出力信号を生成する論理回路とを具備する。

(もっと読む)

環境パラメータに対する依存特性補償信号生成回路

【課題】生成すべき補償信号の極性に制限がなく、環境パラメータ依存特性に対する補償信号の選択範囲が広い補償信号生成回路を、簡易な構成で実現する。

【解決手段】基準温度未満の低温側領域では出力レベルが周囲温度に線形依存し、高温側領域では基準温度に対応する一定の基準出力レベルとなる特性を有する低温側信号を生成する低温側信号生成回路7aと、低温側領域では基準出力レベルとなり、高温側領域では出力レベルが周囲温度に線形依存する特性を有する高温側信号を生成する高温側信号生成回路7bと、低温側信号における低温側領域での温度依存特性の勾配および極性を調整する低温側特性調整回路9a、10aと、高温側信号における高温側領域での温度依存特性の勾配および極性を調整する高温側特性調整回路9b、10bと、低温側特性調整回路および高温側特性調整回路の出力信号を加算して温度補償信号として出力する。

(もっと読む)

発振器

【課題】回路規模を増大することなく、複数の発振周波数を自由に選択することができる発振器を提供する。

【解決手段】複数の発振回路の出力を1つの出力ノードN1に束ね、圧電素子X1,X2の一端を、それぞれ各圧電素子に対応する増幅器の入力端に接続すると共に、圧電素子X1,X2の他端を出力ノードN1に共通して接続する。そして、選択信号SELによって、選択用トランジスタSM1,SM2及びスイッチSW1,Sw2を制御することで、圧電素子X1,X2の何れか一方を選択し駆動させることで、多入力1出力の発振器を実現する。

(もっと読む)

発振検出回路

【課題】低電力化を可能とし、リーク電流による誤動作の発生を無くした発振検出回路を提供する。

【解決手段】発振検出回路は、基準電圧源に接続された第1の入力端子と発振回路出力端に接続された第2の入力端子とを有しており、複数のバイポーラトランジスタにより構成される差動回路を採用し、差動回路の出力端に接続され出力端の電位に応じて充電または放電を行う容量素子と、容量素子の電位に基づいて発振信号端の所望の発振状態を検出する検出回路を有する。

(もっと読む)

MOS容量からなるコンデンサを備えたコンデンサ回路、そのコンデンサ回路を使用した可変容量回路、その可変容量回路を使用した発振回路及びコンデンサ回路の検査方法

【課題】接続不良を見つけた場合は、容量検査を行わないようにして検査時間を短縮させることができる検査回路を備えたコンデンサ回路、そのコンデンサ回路を使用した可変容量回路、その可変容量回路を使用した発振回路及びコンデンサ回路の検査方法を得る。

【解決手段】検査信号TESTがハイレベルになると、NMOSトランジスタM2がオフすると共にPMOSトランジスタM1及びM3がそれぞれオンし、NMOSトランジスタMCのドレインはPMOSトランジスタM1と電流計3を介して電源電圧Vddに接続され、NMOSトランジスタMCのゲート電圧が電源電圧Vddまで上昇してNMOSトランジスタMCはオン状態になり、電源電圧Vdd→電流計3→接続端子T1→PMOSトランジスタM1→NMOSトランジスタMC→接地電圧GNDの経路で電流i1が流れるようにした。

(もっと読む)

1 - 20 / 47

[ Back to top ]