Fターム[5J081BB06]の内容

LC分布定数、CR発振器 (9,854) | 用途 (545) | マイクロ波用 (108)

Fターム[5J081BB06]に分類される特許

1 - 20 / 108

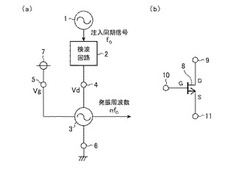

注入同期発振器

【課題】回路規模を小型化する注入同期発振器を得る。

【解決手段】発振周波数foの注入同期信号を発生する基準発振器1と、注入同期信号を検波し、注入同期信号の高周波電力に応じた直流電圧を発生すると共に発振周波数foの高調波を発生する検波回路2とを備え、検波回路2は、注入同期信号の高周波電力に応じた直流電圧および発振周波数foの高調波を、発振器3を構成するFET8のドレインに供給するので、FET8に注入同期信号を注入する回路と、FET8に直流バイアスを印加するバイアス回路とを検波回路2で共用することができ、注入同期発振器の回路規模を小型化することができる。

また、発振周波数foの高調波をFET8のドレインに供給するので、注入同期発振器として同期を容易にすることができる。

(もっと読む)

改良された帯域幅を備える電圧制御発振器を有する位相同期ループ回路

【課題】改良された電圧制御発振器を提供する。

【解決手段】電圧制御発振器(16)は複数の直列に接続された合成利得段(42、44、46)を含む。合成利得段はトランスコンダクタンス段(48)及びトランスインピーダンス段(50)を含む。トランスコンダクタンス段は第1電源電圧端子から第2電源電圧端子への第1電流経路(52、56、64)及び第2電流経路(54、58、66)を有する。第1可変抵抗(62)は第1電流経路と第2電流経路との間に接続される。トランスインピーダンス段は、第1電流経路の出力に接続された入力端子と、出力端子とを有する第1インバータ(68、72)及び第2電流経路の出力に接続された入力端子と、出力端子とを有する第2インバータ(70、74)を有する。第2可変抵抗(76)は第1インバータの入力端子と出力端子との間に、第3可変抵抗(78)は第2インバータの入力端子と出力端子との間に接続される。

(もっと読む)

静磁波発振装置の固定構造

【課題】信号線や電源線を経由して伝わる振動を除去するための静磁波発振装置の固定構造を提供する。

【解決手段】永久磁石もしくは電磁石等により加えられた磁界の強さに依存して共振周波数が変化する静磁波素子を用いて所望の発振周波数を得る静磁波発振装置であって、外部と接続する信号線と、前記外部と接続する電源線と、前記静磁波発振装置を実装するための筐体に固定された支持材と、該支持材に固定され前記信号線または前記電源線を固定する緩衝材とを有し、前記信号線や前記電源線を経由して前記静磁波発振装置に伝達される振動を吸収する。

(もっと読む)

高周波発振器

【課題】安定発振、コンパクトなパッケージを実現したSHF帯に好適な高周波発振器を提供する。

【解決手段】低誘電率、低損失の基板材料として水晶板等の耐熱材を最小限の厚さとした基板を主基板2とし、一次実装する能動素子7とIDT3やデスクリート部品8などを主基板2の表裏にそれぞれ配置し、貫通電極6で両面側の間を接続することで配線長を最短とした。LTCCなどの従来の本体基板に代えて薄い水晶等を要部構成部品を実装する主基板とすることにより、薄型化と小型化を実現した。外力・応力に対する脆弱性を、主面側の保護カバーに加えて裏面にも補強カバーを設け、あるいはモールド構造とすることで補強した。

(もっと読む)

電圧制御発振器

【課題】5GHz以上の周波数帯域で出力周波数を調整するコルピッツ回路を用いた電圧制御発振器において、出力周波数の可変幅(調整幅)の劣化(低下)を抑えると共に、位相雑音の良好な特性を持つ電圧制御発振器を提供すること。

【解決手段】可変周波数帯域内における周波数fに対応する波長をλとすると、共振部1のバリキャップダイオード13とトランジスタ21のベース端子との間に直列となるように、線路長Dがλ/4で且つ特性インピーダンスが10Ω以下の伝送線路6を配置して、トランジスタ21のベース端子からバリキャップダイオード13側を見た時に、当該バリキャップダイオード13と伝送線路6とがいわば可変インダクタンス素子Lと等価になるようにする。

(もっと読む)

帰還型発振装置

【課題】発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化すること。

【解決手段】準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置1において、入力端子から入力された信号を出力端子から出力する増幅素子(HEMT10)と、増幅素子の出力端子から入力端子に信号を帰還するための帰還回路(帰還回路40)と、増幅素子の出力端子と電源の間に挿入され、持続発振時に増幅素子に流れるバイアス電流を制限する抵抗素子(抵抗素子35)と、を有する。

(もっと読む)

高周波発振器

【課題】 位相雑音を劣化させずに2倍波の出力電力を増加できる高周波発振器を得る。

【解決手段】 第1から第3の端子を有する能動素子と、前記第1と第2の端子にそれぞれ接続され、所要の周波数において誘導性となる第1と第2のリアクタンス回路と、前記第3の端子に接続され、前記所要の周波数において容量性となる第3のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数の2倍の周波数においてインピーダンスがショートとなる第4のリアクタンス回路と、前記能動素子の前記第3の端子と前記第3のリアクタンス回路の間に並列に接続され、前記所要の周波数におけるリアクタンスが、前記所要の周波数における前記第4のリアクタンス回路のリアクタンスと絶対値が等しく符号が逆となる第5のリアクタンス回路と、を備える。

(もっと読む)

磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法

【課題】小型化及び低消費電力化を図ることができる磁気同調デバイス駆動回路及びそれを備えた測定装置並びに磁気同調デバイス駆動方法を提供する。

【解決手段】磁気同調デバイス駆動回路10は、固定電圧を出力する電源に接続され、印加された出力電圧制御信号に応じた電圧を出力するスイッチング電源回路11と、スイッチング電源回路11の出力電圧を所望の同調周波数に応じた電流に変換して同調コイル51に供給する定電流回路12と、同調コイル51の電圧の絶対値を所定値だけ大きくするシフト電圧を供給するシフト電圧供給部13と、電流が供給された同調コイル51の電圧とシフト電圧とを加算し、加算後の電圧を出力電圧制御信号としてスイッチング電源回路11に出力する加算回路14と、を備える。

(もっと読む)

高周波発振器

【課題】小型に構成され、高調波と基本波との電力比を増加可能な高周波発振器を得る。

【解決手段】印加された電源電圧に基づいて、発振周波数の基本波で発振動作を行い、発振周波数の2倍波を出力する2倍波取り出し型発振器10と、2倍波取り出し型発振器10の出力端子に接続され、発振周波数の2倍波を通過帯域とする出力回路20とを備え、出力回路20は、2倍波取り出し型発振器10に電源電圧を供給する電源端子21と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する結合線路22と、2倍波取り出し型発振器10と電源端子21との間に直列に接続され、発振周波数の2倍波に対してほぼ1/4波長の長さを有する伝送線路23と、結合線路22の結合量に応じた出力電力を得る第1負荷抵抗24と、電源端子21に対して並列に接続されたキャパシタ25とを有する。

(もっと読む)

アンテナとそれを用いた発振器

【課題】所望の周波数、特に100GHz以上のテラヘルツ帯において共振特性を良好とする新規なアンテナ及びそれを用いた発振器を提供する。

【解決手段】スロットアンテナは、スロットアンテナ本体2となる空隙と、この空隙に対して十字となるように空隙の長手方向に対して垂直方向に一つ以上設けたスリットリフレクタ部3となる空隙とが、導電性平板5に形成されて成り、所望されるインピーダンス又はアドミタンスの周波数特性が得られるようにスリットリフレクタ部3の配置場所、長さ及び幅が定められている。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

静磁波発振装置

【課題】外部磁界からの影響を防止しつつ、小型化及び軽量化を図ると共に、耐振動及び耐衝撃性を向上させた静磁波発振装置を提供する。

【解決手段】静磁波素子を用いて所望の発振周波数を得る静磁波発振装置1であって、静磁波発振装置本体2の周囲に強磁性体33a,33bと振動を吸収可能な非磁性体32a,32b,32cとを交互に積層させると共に、該非磁性体32a,32b,32cが吸収可能な振動周波数を層によって相違させる。

(もっと読む)

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

電子回路

【課題】負性抵抗回路において反射特性を向上させること。

【解決手段】制御端子、第1端子および第2端子を有する第1トランジスタとQ1、前記第1トランジスタの前記第2端子に接続された制御端子、第1端子およびDC電源が接続される第2端子を有する第2トランジスタQ2と、前記第1トランジスタの前記第1端子と前記第2トランジスタの前記第1端子との信号を前記第1トランジスタの制御端子に共通に帰還させる正帰還回路22と、前記第2トランジスタの前記第1端子と前記正帰還回路との間に接続された第1キャパシタC1と、前記第1トランジスタの前記第2端子と前記第2トランジスタの前記制御端子との間の第1ノードN1と、前記第2トランジスタの前記第1端子と前記第1キャパシタとの間の第2ノードN2と、をDC的に接続する経路12と、を具備する電子回路。

(もっと読む)

高周波二倍波発振器

【課題】本発明は、位相雑音の劣化原因によらず位相雑音を低減できる高周波二倍波発振器を提供することを目的とする。

【解決手段】トランジスタと、該トランジスタのベース側に接続された第一電気信号線路と、該第一電気信号線路に接続され他の端は接地された第一シャントキャパシタと、該トランジスタのコレクタ側に接続された第二電気信号線路と、該第二電気信号線路に接続され他の端は接地された第二シャントキャパシタと、該第一電気信号線路と該第二電気信号線路を接続する大容量キャパシタとを備える。該第一電気信号線路の線路長は、基本波信号の波長の1/4の値を奇数倍した長さから基本波信号の波長の1/16の長さを減算した長さと、基本波信号の波長の1/4の値を奇数倍した長さに基本波信号の波長の1/16の長さを加算した長さとの間の値である。

(もっと読む)

電圧制御発振器

【課題】コルピッツ回路を用いた電圧制御発振器において、帰還部の2つのコンデンサ間とトランジスタのエミッタとを接続する導電線路におけるインダクタンス成分の影響による出力周波数の可変幅(調整幅)の劣化(低下)を抑えることのできる電圧制御発振器を提供すること。

【解決手段】コルピッツ回路を用いたVCOにおいて、帰還部2のコンデンサ22、23について、トランジスタ21のベースから伸びる端子部8(T1)及び前記トランジスタ21のエミッタから伸びる端子部8(T2)が夫々装着されるベース基板5上のベース用端子(接続部7)とエミッタ用端子とを直結するように第1の帰還容量素子(コンデンサ)22を配置すると共に、上記エミッタ用端子とアース用端子(接地電極51)とを直結するように第2の帰還容量素子(コンデンサ)23を配置する。

(もっと読む)

マイクロ波発振回路およびその実装方法

【課題】 スルーホールを削減してプリント基板の製造コストアップを防ぎ、基板の線膨張率の違いによる発振周波数ずれを防ぎ、基板に窓を空ける必要がなく、発振周波数範囲が狭くなるのを防ぎ、かつ中心周波数の調整が可能なマイクロ波発振回路の提供。

【解決手段】 マイクロ波発振回路100は、上部基板1と、その表面に設けられる第1表層パターン2と、第1表層パターン上に設けられ第1表層パターンと電気的接続される可変容量素子3と、上部基板の表面の第1表層パターンとは異なる位置に設けられる第2表層パターン4と、第2表層パターン上に設けられ第2表層パターンと電気的接続される発振素子5と、上部基板の裏面に設けられる第1および第2裏面パターン6,7と、下部基板8と、下部基板の表面に設けられる第3表層パターン9と、下部基板の裏面に設けられる第3裏面パターン10とを含む。

(もっと読む)

電圧制御発振器

【課題】マイクロストリップラインのトリミングによってQ値の劣化を招くことなく、各種の周波数帯への調整を可能とする。

【解決手段】電圧制御発振器は、発振用トランジスタのベースに接続された共振回路を有しており、この共振回路には、バラクタダイオードとともにマイクロストリップライン10が設けられている。マイクロストリップライン10は、その一端が制御端子に接続されており、他端がビア7を介してグランド電極に接続されている。またマイクロストリップライン10は、その一端に位置する入力導体部10bから他端に位置する接地導体部10eに至る導電路がスパイラル形状をなしており、導電路の途中が粗調用導電体10aを介してグランドに接続されている。

(もっと読む)

高周波発振器

【課題】位相雑音特性を劣化させることなく出力電力を増大可能な高周波発振器を得る。

【解決手段】発振用の能動素子として用いられるバイポーラトランジスタ1と、バイポーラトランジスタ1のベース端子またはゲート端子に一端が接続されるとともに、他端が接地され、所定の発振周波数において誘導性を有するインダクタ2と、バイポーラトランジスタ1のコレクタ端子またはドレイン端子に一端が接続されるとともに、他端が接地され、発振周波数において誘導性を有するインダクタ3と、バイポーラトランジスタ1のエミッタ端子またはソース端子に一端が接続されるとともに、他端が接地され、発振周波数において容量性を有するキャパシタ4と、を備えた直列帰還型の高周波発振器であって、ベース端子またはゲート端子と、コレクタ端子またはドレイン端子との間に直列接続され、入力された信号の位相を変化させる移相回路5をさらに備えたものである。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

1 - 20 / 108

[ Back to top ]