Fターム[5J081CC08]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 特性の改善 (481) | 周波数特性の改善 (302) | 周波数シフト (75)

Fターム[5J081CC08]に分類される特許

1 - 20 / 75

電圧制御発振器およびそれを用いた情報機器

【課題】周波数変換利得の変動が少ない発振器のためのLC共振回路、それを用いた発振器及び情報機器を提供する。

【解決手段】発振器のLC共振回路が、インダクタL1、第1の微調容量と第1の容量バンクからなる並列回路と、第2の微調容量と第2の容量バンクの直列容量とを含む。発振器の周波数変換利得は、第1の容量バンクの容量値が大きくなるに従い低下する第1の微調容量による発振器の周波数変換利得と、第2の容量バンクの容量値が大きくなるに従い増大する第2の微調容量による周波数変換利得の和となる。

(もっと読む)

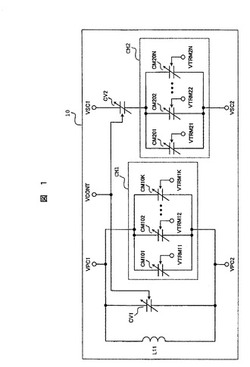

電圧制御発振回路

【課題】簡単な回路構成で応答性をよくし、切り替えられる発振信号の各周波数で同一電圧振幅を得られる電圧制御発振回路を提供する。

【解決手段】LCタンク回路1に第1及び第2のキャパシタ群11,12を備える、第1及び第2のキャパシタ群11,12はそれぞれ2つのキャパシタC1,C2を備える。負性コンダクタンス部2により、LCタンク回路1の共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成し、2つの出力端out1,out2から出力する。電流源31,32からなる電流源3から負性コンダクタンス部2を介してLCタンク回路1に電流を供給する。制御信号を、CMOSスイッチからなる電流源スイッチ4,第1キャパシタスイッチ5及び第2キャパシタスイッチ6に与え、電流源群3から供給する電流とLCタンク回路1のキャパシタンスを切り替える。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

共振器型発振器、及び同調コンデンサ回路

【課題】共振器型発振器のQ値などの特性を高く維持させた設計をより容易に行えるようにする技術を提供する。

【解決手段】静電容量Caの2n倍(nは0〜5までの整数)となっている計6個)のコンデンサ211a〜fが並列に接続され、それらコンデンサ211a〜fにはスイッチ212a〜fがそれぞれ直列に接続されている。コンデンサ211a〜fは、静電容量が大きいものほど、インダクタと接続させる配線402の長さが短い位置に配置されている。それにより、出力する信号の周波数が低くなるほど、配線402の抵抗がQ値に及ぼす影響を低減させる。

(もっと読む)

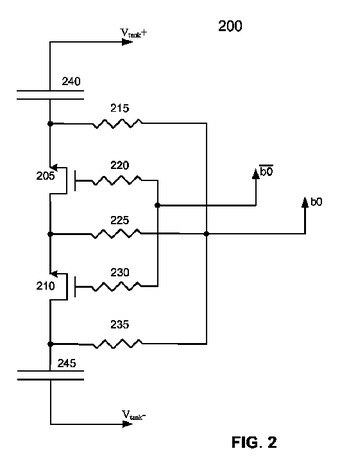

キャパシタスイッチング回路

キャパシタンススイッチング素子(200)が、トランジスタ(205、210)によって直列に接続された、第1のキャパシタ(240)と第2のキャパシタ(245)とを含む。トランジスタのゲートは、一組の抵抗器(220、230)を介して第1の信号(b0/)によってバイアスをかけられ、ソースおよびドレインは、第2の組の抵抗器(215、225、235)を介して第2の信号(b0)によってバイアスをかけられる。信号はレベルシフトされており、相補的であってよい。素子をオンにするためには、第1の信号(b0/)をVDDに設定することができ、第2の信号(b0)をゼロに設定することができる。素子をオフにするためには、第1の信号(b0/)をVDD/2の倍数に設定することができ、第2の信号(b0)をVDD/2の倍数プラス1(the multiple plus one)に設定することができる。素子が発振器同調回路で使用されるとき、トランジスタの圧力ストレスが低減され、トランジスタを薄酸化物で製作することができる。発振器は、セルラアクセス端末のトランシーバにおいて使用されてもよい。  (もっと読む)

(もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

VCO周波数チューニングのための、オーバーラップする2セグメントキャパシタバンク

【解決手段】(例えばFM受信機中の)VCOは、LC共振タンクを含む。LC共振タンクは、粗同調キャパシタバンクおよび微同調キャパシタバンクを含む。粗同調キャパシタバンクは複数のデジタル制御粗同調キャパシタエレメントを含み、アクティブな際に各々は第1キャパシタンス値を供給する。微同調キャパシタバンクは複数のデジタル制御微同調キャパシタエレメントを含み、アクティブな際に各々は第2キャパシタンス値を供給する。キャパシタミスマッチの現実的な問題に対処するため、VCOチューニング範囲の全体にわたるキャパシタンスオーバーラップが、微キャパシタバンクのデジタル制御微同調キャパシタエレメントの全てがアクティブな場合に、微キャパシタバンクのキャパシタンス値が第1キャパシタンス値より大きくなるように第1及び第2キャパシタンス値を選択することによって生成される。 (もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

発振器及びそれを用いた周波数生成回路並びに無線通信システム

【課題】LC型発振器において、高調波歪みによる位相雑音の劣化が小さく、かつ発振振幅の増大化を図り、これにより良好な低位相雑音特性を有する発振器及びそれを用いた通信システムを提供する。

【解決手段】トランジスタからなる少なくとも1つ以上の電圧-電流変換部と、1対の容量性素子と誘導性素子からなるLCタンクを2つ有している共振器とを具備して成り、前記の電圧-電流変換部の出力端子は、前記の共振器に接続され電流-電圧変換されたのちに、前記電圧-電流変換部の入力端子に接続されることにより、帰還ループが構成されて成り、前記共振器を構成している2つのLCタンクを構成する誘導性素子が相互誘導結合されており、前記相互結合係数がおおよそ-0.6であることを特徴とする。

(もっと読む)

可変インダクタ及び電圧制御発振器

【課題】LCの並列共振による電圧制御発振器を構成するための可変インダクタであって、小型かつQ値の劣化を抑制した、複数周波数発振可能な可変インダクタを提供すること。

【解決手段】可変インダクタ100は、線対称軸Y−Y’を有し、Y−Y’上の点Bを通るY−Y’に関して線対称なインダクタ部Ind1及びInd2を備える。インダクタ部Ind2は、点B以外でインダクタ部Ind1と交わらず、インダクタ部Ind1及びInd2は共に曲線のみで構成される。インダクタ部Ind1の線路長はInd2の線路長よりも短い。Ind1は、Y−Y’上の点Z1を中心点とした円周上の円弧で構成され、端子D’から点Bを通って端子D’とY−Y’に関して線対称な端子D’’まで延在する。Ind2は、Y−Y’上の点Z2を中心点とした円周上の円弧で構成され端子E’から点Bを通って端子E’とY−Y’に関して線対称な端子E’’まで延在する。

(もっと読む)

オーム調節可能な発振周波数を有する発振器

調節可能な発振周波数を有する発振器は、端子で負性入力抵抗を示している能動素子、負性入力抵抗を示しているその能動素子の端子と連結した発振回路、および、その発振器の発振周波数が調節可能である調節可能なオーム抵抗を有する素子を含む。 (もっと読む)

発振回路、集積回路装置及び電子機器

【課題】複数の周波数のうちから所望の周波数を選択してクロック信号を生成できる発振回路、集積回路装置及び電子機器を提供すること。

【解決手段】発振回路は、キャパシター10の一端、第1の抵抗素子20の一端及び第2の抵抗素子30の一端がその入力に接続される第1の反転回路と、キャパシター10の他端がその出力に接続される第n(nは2以上の偶数)の反転回路とを有する第1〜第nの反転回路INV1〜INVnと、第nの反転回路INVnの出力が入力され、第1の抵抗素子20の他端を駆動する第1の駆動用反転回路DR1と、第nの反転回路INVnの出力が入力され、第2の抵抗素子30の他端を駆動する第2の駆動用反転回路DR2とを含む。

(もっと読む)

電圧制御発振回路

【課題】製造コストの追加なく一般的に用いられる可変容量素子を利用し、位相雑音特性に優れたRTW形式の電圧制御発振回路を実現できるようにする。

【解決手段】電圧制御発振回路は、ループ状の伝送線路15と、信号線路と接続されたアクティブ回路17と、信号線路と接続され複数の可変容量ユニット23を有する可変容量部21とを備えている。各可変容量ユニット23は、可変容量素子31と、可変容量素子31に制御電位を印加する制御端子41と、可変容量素子31に基準電位を印加する基準電位端子43とを有している。少なくとも2つの可変容量ユニット23は、基準電位が互いに異なっている。

(もっと読む)

信号処理装置及び信号処理方法

【課題】最大の周波数マージンで、発生させる発振周波数をロック状態にする。

【解決手段】ループフィルタ23は、発振周波数における所定の特性に基づいて、入力される制御電圧に対応して発振周波数を発生させるVCO63であって、所定の特性が粗調整されるVCO63に、制御電圧を入力し、VCO粗調整回路135は、制御電圧が所定の設定範囲を超えた場合に、VCOによる所定の特性を、複数の特性のうちのいずれかに粗調整し、DAC133は、制御電圧が所定の設定範囲内で変化する場合に、発振周波数がロック状態とならないとき、所定の設定範囲を広げる方向に更新する。本発明は、例えばPLL回路やCDR回路に適用することができる。

(もっと読む)

プッシュ・プッシュ形式電圧制御発振回路、並びにそれを用いた無線通信機器およびRFモジュール

【課題】周波数可変範囲を狭くすることなく大きな逓倍出力を得られるプッシュ・プッシュ発振回路を提供すること、またその上で2系統の源発振周波数信号を供給可能なプッシュ・プッシュ発振回路を提供すること、或いはそれを用いた無線通信機器を提供する。

【解決手段】差動トランジスタ対と差動トランジスタ対の間に接続されたLC共振回路10と周波数選択回路30を備えたプッシュ・プッシュ電圧制御発振回路であって、前記周波数選択回路30は伝送線路300を備え、源発振周波数に対する2倍高調波信号を前記伝送線路300のグランドライン32から出力する。2倍高調波信号を伝送線路300のグランドライン32から出力することで、伝送線路300の線路を信号が伝播するときに発生する伝播損失を低減でき、大きな出力電力が得られる。

(もっと読む)

位相同期発振器アレイ及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】発振信号の位相差が90度である4位相の同一周波数の発振信号を出力する位相同期発振器アレイである。複数の閉線路21〜23から成る複数のリング共振器と、閉線路の全長を1/4分割した位置に設けられた4つのポート21a〜21dのうち隣接する2つのポート21b、21cと、この閉線路21に隣接する閉線路22の隣接する2つのポート22a、22d間を、それぞれ、負性抵抗として、接続する差動発振器31a、31bと、少なくとも何れか1方の端部に配置される閉線路21において、その閉線路の4つのポートのうち、差動発振器が接続されていない2つのポート21a、21dに対して、90度の位相差を有した信号を励振する励振装置30とを有する。

(もっと読む)

電圧制御発振器

【課題】VCO利得の変動を抑圧した簡易な構成のVCOの提供。

【解決手段】二つの周波数可変手段を具備することでマルチバンド動作を行なう電圧制御発振器(VCO)において、可変容量素子11iaと12ia及び11ibと12ib(i=1、2、3)をそれぞれ互いに極性が逆になる向きに並列接続可能とし、可変容量素子対を形成する。一般に、可変容量素子11iaと12ia、11ibと12ib(i=1、2、3)の容量値は異なる値に設定される。これらの可変容量素子対は、ループコントロール端子3に印加されるコントロール電圧VCNTにより制御されると同時に、帯域設定信号VSW1、VSW2、VSW3によってオンオフされるスイッチ素子であるトランジスタ101a、102a、103a、101b、102b、103bの切替により、VCO本体に電気的に分離・接続される。

(もっと読む)

発振回路装置

【課題】 この発明は、負性抵抗を示す帯域が広くして、使用できる発振周波数を多くすることを目的とするものである。

【解決手段】 この発明の発振回路装置は、相互接続された一対のトランジスタ1、2と抵抗・容量の回路網で構成された発振部100と、発振部100に接続されるループ状の伝送線路で構成された共振部200と、を備え、前記抵抗・容量の回路網の抵抗値及び容量値を前記発振部が第1の周波数帯で負性抵抗となり、その第1の周波数帯より高い周波数帯においてフラットな負性抵抗を示すように設定したことを特徴とする。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

1 - 20 / 75

[ Back to top ]