Fターム[5J081CC18]の内容

LC分布定数、CR発振器 (9,854) | 目的、効果 (1,425) | 補償 (131) | 電源電圧変動 (20)

Fターム[5J081CC18]に分類される特許

1 - 20 / 20

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

半導体発振回路および携帯電話

【課題】基準周波数生成回路は、ロジック回路の電源ノイズの影響を受けて、周波数偏差やピリオドジッターの悪化を引き起こしていた。

【解決手段】CPUや周辺回路などのロジック回路12の電源はレギュレータ13より供給し、基準周波数生成回路11の電源には電源の高周波ノイズを10dB以上の減衰量を持つローパスフィルター10を介してから供給する。これによりロジック回路12で発生する高周波ノイズ起因での周波数偏差やジッターの悪化を抑えることができ、この基準周波数をUARTシリアル回路に接続して通信ができる。

(もっと読む)

クロック生成回路及び当該クロック生成回路を備えた半導体装置

【課題】バッテリーの放電特性に伴う出力電圧の変化によるクロック生成回路からの発信周波数の変動を抑制し、かつバッテリーの蓄電残量を有効利用することのできるクロック生成回路を提供することを課題とする。

【解決手段】バッテリーの出力電圧を検出するための出力電圧検出回路と、出力電圧検出回路で検出された出力電圧の値により分周数を判定する分周数判定回路と、出力電圧の値により基準クロック信号を出力する発振回路と、分周数に応じた基準クロック信号の波の数をカウントするカウンター回路と、カウンター回路のカウンター値により、基準クロック信号を分周する分周回路を有する構成とする。

(もっと読む)

出力回路を備えた発振回路

【課題】電源電圧を低電圧化した場合においても、発振回路の最終出力波形のデューティー比を50%に調整し易く、且つ、種々の外乱要因によってもデューティー比の変動を少なく抑えることが可能な発振回路を提供する。

【解決手段】振動子、増幅回路及び出力回路を含む発振回路であって、前記増幅回路の入力端子に接続される側の前記振動子の端子と、前記出力回路の入力端子とが接続され、振動子の前記端子と、増幅回路の前記入力端子とが容量を介して接続され、さらに、振動子の前記端子側に、所定の電位をバイアスするためのバイアス回路が接続されている。

(もっと読む)

発振型近接センサ、および電界効果トランジスタを用いた発振型近接センサにおけるゲート電流の制御方法

【課題】電界効果トランジスタを発振素子として有する発振回路を備え、ソース端子又はドレイン端子の一方とゲート端子との間を接続して、ゲート電流をゲート端子へと帰還させる帰還路を流れる電流の変化に応じて外部変化を検出する発振型近接センサにおいて、温度変化や電源変動があってもゲート電流igの値を維持して安定性の高いセンサを実現する。

【解決手段】発振型近接センサ1を、ソース端子Sとドレイン端子Dとの間に印加する電圧を変えることによって、帰還路8を流れるゲート電流の直流成分igを所定値に維持する電圧制御部20を備えて構成する。

(もっと読む)

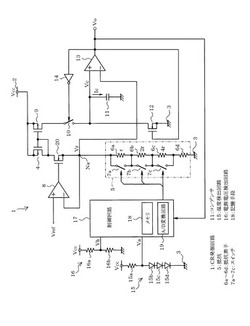

電源補償電圧および電流源

【課題】電源補償電圧または電流を供給する装置および方法を提供する。

【解決手段】電源補償電流および電圧源は、バンドギャップ基準電圧およびスケールされた電源電圧に接続された差動増幅器106を利用する。電源が変動すると、差動増幅器が安定した補償出力を調整する。出力は補償電圧でも電流でもよい。さらに、差動増幅器から複数の電流および電圧が参照されてもよい。安定した補償出力は、外部回路のための基準バイアスとして供給されてもよい。さらに、補償出力は、電圧制御発振器に供給されてもよい。電源補償電圧および電流源は、電源電圧が第1および第2の抵抗器102に跨って分配される、基準ノード122で第2の抵抗器と直列に接続された第1の抵抗器と、電圧基準電源104と、第1および第2の電圧入力および補償出力を有し、前記第1の入力が前記基準ノードに接続され、前記第2の入力が前記電圧基準電源に接続される差動増幅器と、を備える。

(もっと読む)

ボディーバイアス調節型電圧制御発振器

【課題】電源の変化に影響を受けずに常に一定のレベルの発振信号を生成することができるボディーバイアス調節型電圧制御発振器を提供する。

【解決手段】本発明のボディーバイアス調節型電圧制御発振器は、チューニング電圧VTに応じて共振周波数を生成する共振回路部100と、共振回路部100に電力を供給して共振回路部100の共振周波数を発振させて180度の位相差を有する第1、第2発振信号を生成し、ボディーバイアス電圧Vbbに応じて第1、第2発振信号のレベルが一定になるように調節する差動発振部200と、差動発振部200の第1、第2発振信号のレベルを検出し、この検出されたレベルに応じたボディーバイアス電圧Vbbを第1、第2トランジスタM10、M20の各ボディーに供給する出力レベル検出部300とを含むことを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】制御電圧の狭い変化範囲で安定に動作する電圧制御発振器を提供する。

【解決手段】電圧制御可能な可変容量回路12と、インダクタを有するインダクタ回路11と、負性抵抗回路13と、補正電圧を出力する容量制御回路14と、を備える。可変容量回路12とインダクタ回路11と負性抵抗回路13とを並列接続して発振回路を構成する。容量制御回路14は、発振回路における温度変動および/または電源電圧変動に対応して出力される補正電圧によって可変容量回路12におけるキャパシタンスを補正するように制御する。

(もっと読む)

電圧制御発振回路

【課題】バッファ増幅器の電源系を分離して定電圧発生回路と接続し、一部を共用化して電源電圧を下げずに電源ノイズの影響を抑制し小型化する。

【解決手段】差動バッファ増幅器11は、エミッタが共通接続のバイポーラトランジスタ24,25と電源電圧Vccに接続の負荷抵抗26,27からなり、共通エミッタは差動発振器12のインダクタの中点に接続される。差動発振器12のインダクタ中点には接地容量23が接続され、不要な干渉を抑え、ノイズ回り込みを抑制する。差動発振器12の発振信号は結合容量21,22を介して差動バッファ増幅器11の出力端子13から出力される。バイポーラトランジスタ24,25のベースは、抵抗28,29を介して定電圧発生回路61と接続され、電源系と分離してバイアス電圧が供給される。これにより電源ノイズの影響を抑制し、電源電圧を下げることなく出力ができ、消費電流を抑え、かつ電源ノイズの影響を抑制する。

(もっと読む)

集積回路

【課題】従来の発振器用集積回路では、低振幅の出力波形を要求された場合に、出力増幅回路トランジスタ対のゲート・ソース間電圧が十分に確保できず、大きな負荷を駆動できないという問題があった。

【解決手段】 出力増幅回路112のPチャネルトランジスタ110およびNチャネルトランジスタ111のゲートを、コンデンサ106および107により発振回路104の出力に交流的に結合するとともに、抵抗108および109を介してPチャネルトランジスタ110のゲートはGND電位に、Nチャネルトランジスタ111のゲートは電源電位にバイアスされていることにより、これらのトランジスタのゲート・ソース間電圧が充分に確保され、大きな負荷を駆動できるようにしたことを特徴とする集積回路。

(もっと読む)

高い直線性を有する直交発振器

本発明は、同相信号と直交信号の発振周波数を制御する発振回路及び方法に関するものである。第1差動発振回路及び第1差動結合回路を有する第1発振器手段(2)を設けて直交信号を発生する。さらに、第2差動発振回路及び第2差動結合回路を有する第2発振器手段(4)を設けて同相信号を発生する。周波数制御手段を設けて、第1及び第2発振器手段のコモンモード電流及びテール電流を制御することによって、同相信号及び直交信号の発振周波数を変化させる。これにより、高い直線性を有する高周波IQ発振器が得られる。  (もっと読む)

(もっと読む)

トランジスタ発振回路

【課題】 発振用トランジスタ3のベースバイアス回路を改良して電源電圧の変動に対して発振周波数の変化を少くできるトランジスタ発振回路を提供する。

【解決手段】 エミッタがエミッタ負荷抵抗8を介して接地点に接続され、ベースと接地点間に共振回路2が接続され、コレクタが電源端子に接続された発振用トランジスタ3を有し、発振用トランジスタ3のベースとコレクタとの間及びベースとエミッタとの間にそれぞれベースバイアス抵抗9、10が接続され、発振用トランジスタ3のエミッタと交流的接地点の間にコンデンサ7が接続される。

(もっと読む)

電圧制御発振器及びこれを備えた集積回路装置

【課題】本発明は、ある周波数を発振するに際して、いずれの電圧制御発振回路を選択すべきかを一意的に決定することが可能な電圧制御発振器を提供することを目的とする。

【解決手段】本発明に係る電圧制御発振器は、複数の電圧制御発振回路(図6ではVCO1〜VCO3)と、そのうちの1つを選択して動作させる選択回路と、を有して成り、隣接する電圧制御発振回路の発振周波数可変域がその端部で互いに重複されて成る電圧制御発振器において、最も低域側にばらついた状態(low状態)におけるn(≧1)番目の電圧制御発振回路の上端周波数が、最も高域側にばらついた状態(high状態)におけるm(=n+1)番目の電圧制御発振回路の下端周波数よりも高くなるように、各電圧制御発振回路の発振周波数可変域を調整して成る構成とされている。

(もっと読む)

発振回路及びフェーズロックトループ回路

【課題】電源電位が変動する場合であってもレギュレータが不要な発振回路およびフェーズロックトループ回路を実現する。

【解決手段】抵抗Raの一端に電源電位VDDを与え、抵抗Raの他端に定電流源75aを接続する。インダクタL1a,L2aの一端にも電源電位VDDを与え、キャパシタ群1a,2aの一端に、抵抗Raの他端における電位Vmaを与える。インダクタL1a,L2aの他端とキャパシタ群1a,2aの他端とを接続する。抵抗Raには定電流が流れるので、電位Vmaは電源電位VDDに対して一定の電位差を有し、インダクタL1a,L2aの一端およびキャパシタ群1a,2aの一端の間に常に一定の電圧が加わる。よって、たとえ電源電位VDDが変動しても、常に一定の電圧をインダクタおよびキャパシタの直列接続体に印加することができ、レギュレータが不要な発振回路を実現できる。

(もっと読む)

アナログ作動およびデジタル作動される電圧制御発振回路

【課題】電源電圧を小さくした場合でも、出力周波数の同期範囲を十分に大きくすることのできる電圧制御発振回路を提供する。

【解決手段】VCO回路(20)は、コイル(21)と、このコイルに並列の一定容量値の容量素子(24)と、調整可能な容量素子(22、23)とを有する。第1容量素子(22)は、1つまたは複数のバラクタ−から形成され、その容量は、アナログ制御電圧(Vtune)により調整可能である。第2容量素子(23)は、デジタルビットワードVCWD[N:1]により作動可能な複数の容量素子の配列部から形成される。VCO(20)のデジタル較正は、現時点の制御電圧が、特定の電圧の範囲内にあるか否かを判定し、特定の電圧範囲内でない場合、デジタルビットワードが、1ビット値ずつ上昇または低下する。

(もっと読む)

電圧制御発振器、及び無線通信機器

【課題】 電界効果トランジスタを用いる電圧制御発振器において、電源電圧変動に伴う発振周波数の揺れを小さくするためにバックゲート端子をソースに接続すると、基板ロスが大きくなり位相雑音特性が劣化する。

【解決手段】 発振トランジスタ115のバックゲート端子を、高インピーダンス素子119を介してソース端子に接続し、発振トランジスタ116のバックゲート端子を、高インピーダンス素子120を介してソース端子に接続する。

(もっと読む)

1 - 20 / 20

[ Back to top ]