Fターム[5J081KK23]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 二次要因 (416) | 切換・開閉 (120)

Fターム[5J081KK23]に分類される特許

1 - 20 / 120

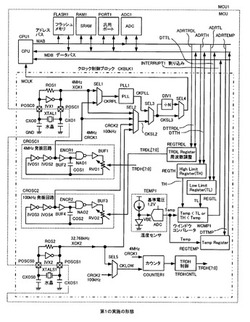

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】発振周波数遠方の雑音を低減することが可能なディジタル制御発振装置、ならびに高周波信号処理装置を提供する。

【解決手段】例えば、複数の単位容量ユニットCIU[1]〜CIU[k]を用いて分数容量を実現する。CIU[1]では、容量素子CFXp[1],CFXm[1]の一端がそれぞれ発振出力ノードOscP,OscMに接続される。一方、CIU[2]〜CIU[k]では、容量素子CFXp([2]〜[k]),CFXm([2]〜[k])の一端が固定電圧V6に接続される。CIU[1]〜CIU[k]の一方の容量素子の他端は共通接続され(SWFD)、他方の容量素子の他端も共通接続される(SWFS)。そして、CIU[1]〜CIU[k]内の各スイッチ(SWF1〜SWF3)のオン・オフは共通に制御される。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

発振回路

【課題】

発振周波数を切り替えたときの発振停止を抑制した発振回路を提供する。

【解決手段】

発振回路は,第1の基準電圧側に設けられた第1,第2のインダクタL,Lxと,第2の基準電圧と第1,第2のインダクタとの間にそれぞれ設けられゲートとドレインが交差接続された第1,第2のトランジスタP1,Px1と,第1,第2のインダクタンスそれぞれに接続され複数の周波数制御用キャパシタC0〜Cn,Cx0〜Cxnを並列に有する第1,第2のキャパシタ群と,第1,第2のキャパシタ群の対応する周波数制御用キャパシタ間に設けられ発振周波数制御信号に基づいて導通または非導通に制御される複数の第1のスイッチSW0〜SWnと,第1のスイッチの両端子と所定電圧との間にそれぞれ設けられた複数の第2のスイッチSWp,SWxpとを有し,発振周波数制御信号の切り替わり時に,導通から非導通に切り替えられる第1のスイッチの両端子に設けられた第2のスイッチが一時的に導通する。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

電圧制御発振回路

【課題】簡単な回路構成で応答性をよくし、切り替えられる発振信号の各周波数で同一電圧振幅を得られる電圧制御発振回路を提供する。

【解決手段】LCタンク回路1に第1及び第2のキャパシタ群11,12を備える、第1及び第2のキャパシタ群11,12はそれぞれ2つのキャパシタC1,C2を備える。負性コンダクタンス部2により、LCタンク回路1の共振信号をフィードバックして相互180°の位相差を有する2つの発振信号を生成し、2つの出力端out1,out2から出力する。電流源31,32からなる電流源3から負性コンダクタンス部2を介してLCタンク回路1に電流を供給する。制御信号を、CMOSスイッチからなる電流源スイッチ4,第1キャパシタスイッチ5及び第2キャパシタスイッチ6に与え、電流源群3から供給する電流とLCタンク回路1のキャパシタンスを切り替える。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

発振回路及び半導体装置

【課題】周波数可変範囲の広い発振回路及び発振回路を備えた半導体装置を提供する。

【解決手段】第1の端子と第2の端子との間に接続されたインダクタンス素子と、インダクタンス素子と並列に第1の端子と第2の端子との間に接続された増幅回路と、第1の端子及び第2の端子に接続された第1の容量素子と、を備えた共振型発振回路であって、インダクタンス素子の配線の途中に2箇所以上の引き出し部を設け、2箇所以上設けた引き出し部の間にオンしたときに当該引き出し部間を短絡するスイッチ素子と第2の容量素子とが並列に接続されている。

(もっと読む)

切り替え可能インダクタネットワーク

制御信号に応じて設定可能インダクタンスを有する切換可能インダクタネットワークを提供するための技術。前記切り替え可能インダクタネットワークは、差動モード動作の寄生素子の影響を低減するために完全に対称的なアーキテクチャを採用することができる。前記切り替え可能インダクタネットワークは、特に、マルチモード通信回路への用途、例えば、電圧制御発振器(VCO)またはそのような回路におけるアンプもしくはバッファに適している。 (もっと読む)

共振器型発振器、及び同調コンデンサ回路

【課題】共振器型発振器のQ値などの特性を高く維持させた設計をより容易に行えるようにする技術を提供する。

【解決手段】静電容量Caの2n倍(nは0〜5までの整数)となっている計6個)のコンデンサ211a〜fが並列に接続され、それらコンデンサ211a〜fにはスイッチ212a〜fがそれぞれ直列に接続されている。コンデンサ211a〜fは、静電容量が大きいものほど、インダクタと接続させる配線402の長さが短い位置に配置されている。それにより、出力する信号の周波数が低くなるほど、配線402の抵抗がQ値に及ぼす影響を低減させる。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

設定可能ワイドチューニングレンジ発振器コア

発振器は、共振器と、第1および第2のp型トランジスタと、第1および第2のn型トランジスタとを含む。共振器は、第1の端子と第2の端子とを持つ。第1のp型トランジスタは、第1の端子にスイッチ可能に接続されており、第2のp型トランジスタは、第2の端子にスイッチ可能に接続されている。第1のn型トランジスタの第1のドレインと第2のn型トランジスタの第2のドレインとは、それぞれ、第1の端子および第2の端子に電気的に接続される。発振器はNMOSのみモードおよびCMOSモードで作動可能である。 (もっと読む)

1 - 20 / 120

[ Back to top ]