Fターム[5J098AB02]の内容

能動素子を用いた回路網 (5,588) | 回路要素 (1,356) | 増幅器 (406) | 演算増幅器 (140)

Fターム[5J098AB02]に分類される特許

1 - 20 / 140

フィルタ回路及び受信装置

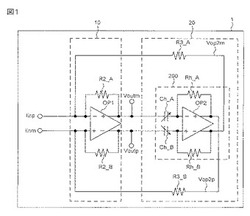

【課題】低雑音かつ低カットオフ周波数のフィルタ回路をより小面積で実現する。

【解決手段】フィルタ回路(1〜5)は、入力端子(Iinp、Iinm、(Vinp、Vinm))に供給された入力信号を受け、信号を増幅して出力端子(Voutm、Voutp)に出力する第1回路(10、11)と、第1容量素子(Ch_A、Ch_B)を介して前記第1回路の出力信号を入力する第1差動増幅回路(OP2)と、前記第1差動増幅回路(OP2)の入出力間に負帰還経路を形成する第1抵抗素子(Rh_A、Ch_B)と、前記第1差動増幅回路の出力と前記第1回路の入力との間に負帰還経路を形成する第2抵抗素子(R3_A、R3_B)とを有する。

(もっと読む)

受信装置及び多重フィルタの制御方法

【目的】受信強度に拘わらず高精度な復調を行うことが可能な受信装置及び多重フィルタの制御方法を提供することを目的とする。

【構成】送信信号を受信して得られた周波数信号に対して、夫々が異なる周波数特性を有する複数のフィルタが直列に接続されてなる多重フィルタによって周波数選択処理を施すにあたり、受信強度が所定の閾値受信強度よりも高い場合には、複数のフィルタの内の少なくとも1つのフィルタの中心周波数を偏倚させる。

(もっと読む)

トランスコンダクタンス調整回路、回路装置及び電子機器

【課題】トランスコンダクタンスを精度良く調整することができるトランスコンダクタンス調整回路、回路装置及び電子機器等を提供すること。

【解決手段】トランスコンダクタンス調整回路100は、第1の信号I及び第1の信号Iと位相が90度異なる第2の信号Qが入力され、第1、第2の抵抗素子RA1と、第1、第2のキャパシターCA1、CA2と、演算トランスコンダクタンス増幅器で構成される中心周波数シフト回路110と、トランスコンダクタンス調整信号AGMを出力する調整信号生成回路120とを含む。調整信号生成回路120は、第2の信号Qと第1の出力信号OIとに基づいて、又は第1の信号Iと第2の出力信号OQとに基づいて、又は第1の信号Iと第1の出力信号OIとに基づいて、又は第2の信号Qと第2の出力信号OQとに基づいて、トランスコンダクタンス調整信号AGMを生成する。

(もっと読む)

バンドパスフィルタ及びバンドパスフィルタのキャリブレーション方法

【課題】BPFを構成するOTAの個数を削減し,低消費電力で高次のバンドパスフィルタを提供する。

【解決手段】バンドパスフィルタは,入力信号が入力されるハイパスフィルタ(14)と,ハイパスフィルタの出力が反転入力端子に入力され,反転入力端子と非反転入力端子間の入力電圧を増幅して出力信号を出力端子に出力するアンプ(10)と,アンプの非反転出力端子と反転入力端子との間に接続された第1抵抗(R2)と,反転入力端子に第1端子が接続された第1キャパシタ(C2)と,アンプの非反転出力端子の出力信号の極性を反転し,当該反転した信号をキャパシタの第2端子に出力する反転アンプ(12)とを有する。

(もっと読む)

フィルタ回路

【課題】フィルタ回路の遮断周波数精度を悪化させること無く、回路規模を低減することができるフィルタ回路を提供する。

【解決手段】駆動電流生成回路303は、容量C1に第1の基準電流を一定期間充電することにより生成される充電電圧を用いて、容量C1と第1の基準電流の比に比例した第1の駆動電流を生成する。OTA301は、正入力端子と負入力端子間の電位差に応じて、第1の駆動電流から、容量C1と第1の基準電流の比に逆比例した第2の駆動電流を生成して電圧に変換し、この電圧に応じて第2の基準電流を分配する。OTA301は、第2の基準電流を分配した電流と同量の電流を折り返して供給するカレントミラー回路を有し、正入力端子と負入力端子間の電位差に応じた電流をカレントミラー回路により折り返して負荷容量302に供給する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】半導体集積回路に集積化された内蔵フィルタの周波数特性を正確に設定すること。

【解決手段】半導体集積回路は、フィルタ回路(1)と、カットオフ周波数補償回路(2)と、Q値補償回路(3)とを具備する。カットオフ周波数補償回路(2)は、フィルタ回路(1)の容量成分(C1、C2)を調整することによってフィルタ回路のカットオフ周波数を所望の値に調整する。Q値補償回路(3)は、カットオフ周波数補償回路(2)によるフィルタ回路(1)のカットオフ周波数の調整の後に、フィルタ回路(1)の抵抗成分(R3)を調整することによってフィルタ回路(1)のQ値を所望の値に調整する。

(もっと読む)

アクティブフィルタ

【課題】フィルタのQ値が変動することがないアクティブフィルタを提供する。

【解決手段】位相容量素子を含む演算増幅器、フィルタ用抵抗素子、フィルタ用容量素子、バイアス回路を含むアクティブフィルタにおいて、バイアス回路を、ゲート同士が接続されるMOSTr41、42、MOSTr41とドレイン同士が接続されるMOSTr43、MOSTr44とゲート同士が接続され、MOSTr42とドレイン同士が接続されるMOSTr44、MOSTr41またはMOSTr42のうちのいずれか1つのソースに接続される抵抗素子45、MOSTr41のドレインに接続される出力端子46またはMOSTr44のドレインに接続される出力端子47によって構成し、抵抗素子45を、フィルタ用抵抗素子と同じプロセス条件で製造し、位相補償容量素子をフィルタ用容量素子と同じプロセス条件で製造する。

(もっと読む)

バンドパスフィルタ

【課題】スーパーヘテロダイン構成のミキサの出力について不要周波数成分の除去を行うバンドパスフィルタにおいて、信号通過帯域の広い範囲で、より大きな減衰特性を実現する。

【解決手段】全差動オペアンプOP1i〜OP3i、OP1q〜OP3qと、その出力と入力との間に並列に接続された抵抗R1〜R3および容量C1〜C3、Czからなるローパスフィルタを、複数段縦続接続してバンドパスフィルタを構成する。縦続接続されたローパスフィルタのうち、1つのフィルタに容量を追加して、マイナス側の周波数にのみゼロ点を設ける。容量を追加してノッチフィルタに置き換えることにより、信号通過帯域の低い周波数にゼロ点が追加され、信号通過帯域の広い領域で大きな減衰特性を取ることができる。

(もっと読む)

フィルタ調整装置、電源制御システム、およびフィルタ調整方法、

【課題】位相比較を行わず、振幅検出結果に基づいてフィルタ特性のばらつきを高精度、かつ自動的に補償可能なフィルタ調整装置を提供すること。

【解決手段】実施形態によれば、フィルタ調整装置はフィルタと、基準信号生成部と、制御部と、振幅検出部と、調整部とを具備する。フィルタは特性制御信号に応じてフィルタ特性が制御される。基準信号生成部は振幅制御信号に応じた振幅の基準信号を生成し、フィルタに供給する。制御部は特性制御信号によりフィルタに異なるフィルタ特性を設定し、振幅制御信号により基準信号の振幅を異なる振幅に設定する。振幅検出部は特性制御信号によりフィルタに異なるフィルタ特性が設定される状態において、異なる振幅の基準信号に対するフィルタの出力信号の振幅を検出する。調整部は振幅検出部によって検出された複数の振幅に従い、フィルタ特性が所望の特性となる所望の特性制御信号を決定する。

(もっと読む)

カットオフ周波数自動調整回路及び携帯情報端末

【課題】フィルタのカットオフ周波数を、その調整範囲内の任意の設定値に自動調整可能にする。

【解決手段】電圧電流変換回路(30)、充電回路(50)、放電回路(40)、複数の静電容量を有するデジタル容量(70)、上記デジタル容量に入力される電圧と基準電圧との対比を行う比較器(80)及び上記デジタル容量を制御する容量制御回路(600)を含んでカットオフ周波数自動調整回路(412)を構成する。上記リセット信号が所定の論理レベルになったときから、上記比較器によって上記デジタル容量に入力される電圧が上記基準電圧より高くなったことが検知されるまでの時間を計測し、その計測結果と、上記デジタル容量の目標値と、上記デジタル容量の現在の値とに基づいて上記デジタル容量の次の設定値を求める処理を、所定の条件下で繰り返すことによって上記デジタル容量を制御する。上記目標値は、調整範囲内の任意の設定値とすることができる。

(もっと読む)

電磁誘導型埋設物探査装置

【課題】デジタル信号処理装置(略称「DSP」)による電磁誘導型埋設物探査装置では、デジタル化時の量子化レベル等の制約によって十分な感度が得られず、非金属管路に収容される光ファイバーケーブルを、手軽な間接法によって検出することが難しかった。

【解決手段】本発明の水晶アクティブフィルタは中心周波数の調整機能と水晶振動子の破損防護機能を有しており、多段接続により超狭帯域かつ高DU比のフィルタを容易に構成することができ、高感度の電磁誘導型埋設物探査装置を実現することができる。これによって、非金属管に収容される光ファイバーケーブルを、間接法によって検出することが可能となる。

(もっと読む)

オペレイショナル・トランスコンダクタンス・アンプ、オペレイショナル・トランスコンダクタンス・アンプを用いたフィルタ回路

【課題】入力電圧範囲を広くしても線形性能の優れ、かつトランスコンダクタンス値精度の優れたOTA、OTAを用いたフィルタ回路を提供する。

【解決手段】I−V変換器と、内部抵抗素子の抵抗値に比例する増幅率でI−V変換器の出力電流を増幅する電流制御回路1、2とによってOTAを構成する。そして、電流制御回路1、2を、入力電流が入力されるドレイン、第1制御電圧が供給されるゲートを有するMOSトランジスタ10、出力電流が出力されるドレインを有するMOSトランジスタ13、第2制御電圧が供給されるゲートを有するMOSトランジスタ11、MOSトランジスタ10のドレインと接続される非反転入力端子、MOSトランジスタ13のゲートと接続される出力端子、MOSトランジスタ13のソース及びMOSトランジスタ11のドレインと接続される反転入力端子を有する差動増幅器12によって構成する。

(もっと読む)

フィルタ較正

【課題】費用対効果が大きく、簡単であり、さらに正確な、フィルタを較正する方法を提供する。

【解決手段】フィルタ104、116は、較正中に発振器として再構成される。フィルタを再構成するために、スイッチおよび/または他の構成が使用されて、フィルタの負のフィードバックループに対して正のフィードバックループを再構成する。フィルタのコンポーネントを調整して、所望のフィルタ特性に対応する発振を達成するために発振パラメータが次に測定される。

(もっと読む)

スイッチトキャパシタフィルタ及びスイッチトキャパシタフィルタの制御方法

【課題】簡易な構成により雑音を低減することができるスイッチトキャパシタフィルタ及びその制御方法を提供すること。

【解決手段】本発明では、演算増幅器AMPの反転入力は積分キャパシタC0の一端と、出力は積分キャパシタC0他端と接続される。スイッチトキャパシタは第1〜3の順に接続状態が移行する。第1の接続状態では、第1の端子は入力信号と、第2の端子は固定電圧と接続される。第2の接続状態では、第1の端子は固定電圧と、第2の端子は演算増幅器AMPの反転入力と接続される。第3の接続状態では、第1の端子は演算増幅器AMPの出力と、第2の端子は演算増幅器AMPの反転入力と接続される。第2及び第3の接続状態のスイッチトキャパシタが各1個以上存在する場合の第2の接続状態のスイッチトキャパシタの個数は常に同じであり、第3の接続状態のスイッチトキャパシタの個数も常に同じである。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルター10は、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプをOP1と、第1の入力キャパシターC1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、前記ハイパスフィルター10の入力信号VINが供給され、第2の入力端に、出力端から帰還された帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルター10の出力信号VOUTが出力される。

(もっと読む)

スイッチトキャパシター回路を用いたハイパスフィルター及び電子機器

【課題】設計の自由度を失うことなく、SC回路を構成するスイッチのクロック周波数を高く、且つカットオフ周波数を低くする場合において面積をより小さくできるSC回路を用いたHPF等を提供する。

【解決手段】スイッチトキャパシター回路を用いたM(Mは2以上の整数)次のハイパスフィルターは、第1の入力端、第2の入力端及び出力端を備える第1のオペアンプOP1と、第1の入力キャパシターC1と、出力端から帰還される帰還信号に対してハイパスフィルターのゲイン調整を行うゲイン調整回路GA1とを有する第1のスイッチトキャパシター積分器1001を含み、第1の入力端に、ハイパスフィルターの入力信号VINが供給され、第2の入力端に、帰還信号が第1の入力キャパシターC1を介して供給され、出力端からハイパスフィルターの出力信号VOUTが出力される。

(もっと読む)

受信装置及びイメージ除去方法

【課題】ウィーバー方式又はハートレー方式等のイメージ除去構成と複素フィルタを組み合わせて用いる場合に、希望信号及びイメージ信号の直交性を共に維持する。

【解決手段】直交ミキサ(ミキサ101及び102)は、RF信号をダウンコンバートし、I信号及びQ信号を生成する。複素フィルタ103は、正の周波数領域と負の周波数領域との間で非対称な周波数利得特性を有し、I信号及びQ信号に含まれるイメージ信号を希望信号に比べて抑圧する。直交補償回路106は、複素フィルタ103の後段に配置され、複素フィルタ103によってイメージ抑圧されたI信号及びQ信号の間における希望信号の位相差誤差及び振幅誤差を打ち消すように、I信号及びQ信号を補正する。また、制御回路117は、複素フィルタの後段にてI信号及びQ信号に現れるイメージ信号の位相差誤差及び振幅誤差を打ち消すように、複素フィルタ103の素子特性を調整する。

(もっと読む)

フィルタ回路

【課題】フィルタ特性の可変幅が細かく且つ範囲が広い場合であっても、回路の増大を抑制できると共に、コストを抑制し得るフィルタ回路を提供する。

【解決手段】フィルタ回路2のフィルタ特性を決定する少なくとも1種の素子3の素子値を、動作クロックCLKに基づきデジタルコード入力Codeをシグマデルタ変調するΣΔ変調器1の出力、或いは該ΣΔ変調器1の出力をコード変換するデコーダ4を介した信号に基づき変化させる。

(もっと読む)

gm−Cフィルタの周波数補正方法と該方法を使うことができる装置

【課題】gm−Cフィルタの周波数補正方法を提供する。

【解決手段】周波数補正方法は、周波数補正回路が、gm−Cオシレータから出力され、工程変化を表わすオシレーション信号の周波数と基準コードとによって、gm−Cフィルタのカットオフ周波数を調節することができる補正コードを生成する段階と、周波数補正回路が生成された補正コードが、基準コードの範囲内に属するか否かを判断する段階と、周波数補正回路が、判断結果によって生成された補正コードをgm−Cフィルタに出力するか、またはgm−Cオシレータのトランスコンダクタンスとgm−Cフィルタのトランスコンダクタンスとを調節するための可変電流を生成する段階と、を含む。

(もっと読む)

1 - 20 / 140

[ Back to top ]