Fターム[5J106BB03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 用途 (1,086) | 情報機器 (112)

Fターム[5J106BB03]に分類される特許

1 - 20 / 112

マイクロコントローラー

【課題】誤動作を確実に防止する。

【解決手段】クロック信号が供給されて動作する演算回路と、第1クロック信号を生成する発振回路と、基準クロックに基づいて第2クロック信号を生成するPLL回路と、第2クロック信号の異常を検出する異常検出回路と、第1クロック信号と第2クロック信号のいずれかを選択して演算回路に供給する選択回路であって、電源起動時には第1クロック信号を選択し、異常検出回路で異常が検出されない場合には、ファームウェアの設定に応じて第1クロック信号から第2クロック信号に切り換え、異常検出回路で異常が検出された場合には、ファームウェアの設定に関わらずに、第1クロック信号から第2クロック信号への切り換えを行わない選択回路と、異常検出回路で異常が検出された場合に、第1クロック信号から第2クロック信号への切り換えが行われなかったことを演算回路に知らせるステータスレジスタと、を備える。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

半導体装置及びその制御方法

【課題】クロック信号にジッタ成分が重畳している場合であってもDLL回路を正しくロックさせる。

【解決手段】カウンタ部102のカウント値に応じてクロック信号LCLKを生成するディレイライン101と、クロック信号LCLKを反転させるか否かを制御する反転制御部103とを備える。カウンタ部102のカウント値を第1の初期値にリセットした後、反転制御部103はクロック信号LCLKを反転させ又は反転させることなく出力する。次に、カウンタ部102のカウント値を第2の初期値にリセットする。本発明によれば、ジッタなどの影響によってクロック信号LCLKを誤って反転させ、或いは誤って反転させなかった場合であっても、ダウンカウント(またはアップカウント)が多数回連続することがなくなる。これにより、第1及び第2の初期値としてオフセットした値を用いることが可能となる。

(もっと読む)

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

クロックデータリカバリ回路および送受信半導体集積回路

【課題】高速ジッタに追従してクロック再生とデータ再生を可能とする。

【解決手段】クロックデータリカバリ回路1のパルス幅整形回路102はハイとローの期間のデューティ比が略5:5の第1多相クロックCLK’0〜9に応答して、デューティ比が略5−α:5+αの第2多相クロックCLK0〜9を生成する。サンプリング回路106は受信データ信号RXDATAを第2多相クロックでサンプリングして、複数のサンプリング信号を生成する。エッジ検出回路105は複数のエッジ検出信号を生成し、位相選択信号生成回路103は複数の位相選択信号を生成する。クロックデータ生成回路104は、複数のサンプリング信号Sample_Φ0〜9と受信データ信号RXDATAの一方の信号と複数の位相選択信号と第2の多相クロックに応答して、再生クロックRCLKと再生データRDATAを生成する。

(もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】高速且つ正確にDLL回路をロックさせる。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD0の論理レベルに基づいてカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が変化しない期間においてはカウンタ回路130の更新ピッチを最小ピッチの2倍に設定し、位相判定信号PD0が変化したことに応答してカウンタ回路130の更新ピッチを最小ピッチに設定するピッチ調整回路300と、を備える。これにより、高速且つ正確にDLL回路をロックさせることが可能となる。

(もっと読む)

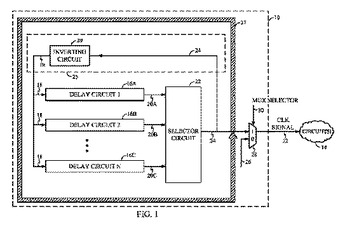

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

クロックデータリカバリー回路およびその動作方法

【課題】回路規模および消費電力を削減すること。

【解決手段】クロックデータリカバリー回路3では、クロック発生器300のサンプリングクロックに応答してA/D変換器301がA/D変換し、順次生成の複数のデジタル出力信号はデータ補正部303に供給され、順次生成の複数の補正デジタル信号は位相比較器305に供給される。位相比較器305の出力はループフィルタ306を介してタイミング生成部304に供給され、複数の再サンプリングタイミングの情報Pvcoはデータ補正部303に供給される。検出回路302はアナログ入力信号の周期Tとサンプリングクロックの周期tの比T/tの誤差情報nvcoを生成して、タイミング生成部304は複数の遅延時間で複数の再サンプリングタイミングを生成して、データ補正部303は複数の補正率で複数の補正デジタル信号を生成する。

(もっと読む)

デジタル位相同期回路

【課題】ホールドオーバ期間中の温度特性と経年変化に対する影響を抑え、周波数の高安定性を維持するホールドオーバ機能を有するデジタル位相同期回路を得る。

【解決手段】電圧制御型クロック発振手段の周辺の温度を測定する温度測定手段と、同期対象と同期している間、デジタルフィルタ手段からの出力で電圧制御型クロック発振手段を制御するとともにデジタルフィルタ手段からの出力と電圧制御型クロック発振手段の周辺の温度、経過時問の履歴から経過時間と電圧制御型クロック発振手段の周辺の温度と項に持つ2元多項式を求め、同期対象と同期していない間、同期対象に同期しなくなってからの経過時間および電圧制御型クロック発振手段の周辺の温度から2元多項式で電圧制御型クロック発振手段を制御する制御信号を推定するとともに推定した制御信号で電圧制御型クロック発振手段を制御するホールドオーバ手段と、を有する。

(もっと読む)

クロック信号制御回路及びクロック信号制御方法

【課題】クロック信号の周波数制御をより好適に行うこと。

【解決手段】モニタ回路12のリングオシレータ16によるモニタ結果であるモニタ信号MSの周波数に応じて設定値記憶回路13からテーブル値TVALを出力させる。そして、そのテーブル値TVALに応じてクロック信号生成回路14のPLL回路15a,15bにより生成した発振信号と等しい周波数のクロック信号CLKを対象回路11に供給する。

(もっと読む)

PLL回路及び光ディスク装置

【課題】適切な動作モードとすることができなかった。

【解決手段】それぞれ位相が異なる複数の基準クロックを出力する多相基準クロック出力回路と、複数の基準クロックをそれぞれ所定の値で分周した複数の分周クロックを出力する多相分周回路と、複数の基準クロックのいずれか1つ、もしくは、複数の分周クロックのいずれか1つのうちのどちらかを選択し、その選択したクロックを選択クロックとして出力する選択スイッチ回路と、選択クロックを動作クロックとし、周波数制御入力データの値に応じて周波数が変動する出力クロックと、出力クロックと周波数制御入力データの値に応じて計算される理想位相との位相差を示す遅延量データとを出力するデジタルVCOと、遅延量データに応じて複数の分周クロックのうち1つに同期した出力クロックを選択して出力する選択回路と、を有するPLL回路。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

1 - 20 / 112

[ Back to top ]