Fターム[5J106CC16]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 局部発振回路 (38)

Fターム[5J106CC16]に分類される特許

1 - 20 / 38

時間差加算器を含むシステムオンチップ、時間差累算器を含むシステムオンチップ、シグマ−デルタタイムデジタル変換器、デジタル位相ロックループ、温度センサ、及びシステムオンチップ

【課題】 入力信号間の時間差を加算する時間差加算器を含むシステムオンチップを提供する。

【解決手段】 時間差加算器100は、第1入力信号SIN1、第2入力信号SIN2、第3入力信号SIN3、及び第4入力信号SIN4に応答して第1出力信号SOUT1及び第2出力信号SOUT2を生成する。時間差加算器100は、第1入力信号SIN1と第2入力信号SIN2との間の第1時間差TD1、及び、第3入力信号SIN3と第4入力信号SIN4との間の第2時間差TD2を加算することによって、第1時間差TD1と第2時間差TD2との和に相応する時間差(TD1+TD2)を有する第1出力信号SOUT1及び第2出力信号SOUT2を出力する。これにより、低い電源電圧環境において、時間ドメインで信号処理を遂行することができ、性能を向上させることができる。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

位相補正方法、位相補正回路、及びそれを含む信号処理装置

【課題】ローカルオシレーターから出力された信号の位相補正方法を提供する。

【解決手段】方法は、同位相出力信号の位相と直交位相出力信号の位相との比較結果に相応するデジタルコードを発生させる。方法は、同位相出力信号の位相と直交位相出力信号の位相との差を90°にするために、直交位相差動入力信号とデジタルコードとに応答して、同位相出力信号の位相を調節し、同位相差動入力信号とデジタルコードとに応答して、直交位相出力信号の位相を調節する。

(もっと読む)

位相補正装置、位相補正方法

【課題】無線送信用の電力増幅器の出力をフィードバックする位相補正装置及び位相補正方法において、フィードバック系の安定性を向上させたものを提供すること。

【解決手段】位相検出器10により検出された位相誤差(電圧CV)に対して、想定される位相誤差の全範囲でスイープさせた位相量(スイープ信号の電圧VSWP)を付加して、位相補正の目標値(電圧CV’)とする。これにより、位相補正処理の初期において、PLLのロックレンジへの引き込みを素早く行う。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

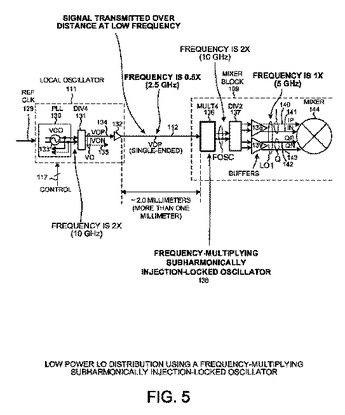

周波数逓倍サブハーモニック注入同期発振器を使用した低電力LO分配

局部発振器は、相対的に低い周波数の信号を、集積回路にわたりミキサの位置まで伝達する。ミキサの近くでは、周波数逓倍サブハーモニック注入同期発振器(SHILO)が、その信号を受信し、それからより高い周波数の信号を発生させる。SHILOがIおよびQ直交位相信号を出力する場合には、IおよびQ信号がミキサをドライブする。SHILOが直交位相信号を発生させない場合には、直交位相発生回路が、SHILO出力信号を受信し、それからミキサをドライブするIおよびQ信号を発生させる。1つの有利な態様において、局部発振器からSHILOまでの距離を越えて伝達される信号の周波数は、近くでミキサをドライブするIおよびQ信号の周波数よりも低い。距離を越えて伝達される信号の周波数を低くすることは、従来のシステムと比較すると、50パーセント以上、LO信号分配システムの電力消費を減じることができる。  (もっと読む)

(もっと読む)

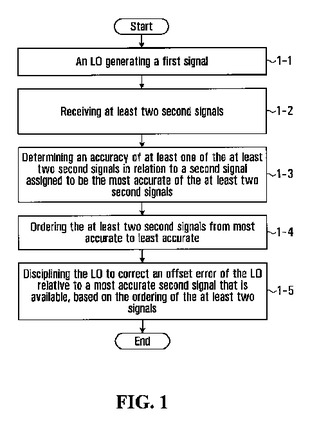

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、少なくとも2つの入力を有する優先制御部とを有し、入力の各々は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号をそれぞれ受信し、優先制御部は、少なくとも2つの第2信号の内の少なくとも1つの第2信号の精度を判定し、何れかの第2信号は少なくとも2つの第2信号の内で精度が最高であるように指定され、優先制御部は、最高精度から最低精度へ少なくとも2つの第2信号を順番に並べ、少なくとも2つの第2信号の順番に基づいて、装置に利用可能な最高精度の第2信号に対してLOのオフセットエラーを補正するように、LOが調整される。  (もっと読む)

(もっと読む)

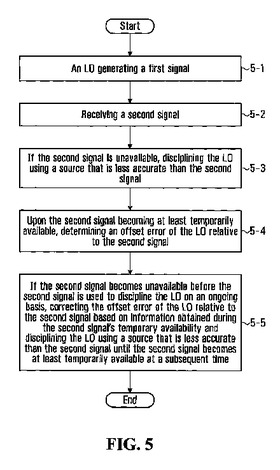

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

復調器および通信装置

【課題】高精度に復調処理を行う。

【解決手段】復調器30Aの局部発振器70は、変調器10から送信されて注入される変調信号SRFの局部発振周波数に局部発振信号SLOの周波数を同期させ、同期させた局部発振信号SLOをミキサ40に出力する。ミキサ40は、同期した局部発振信号SLOと変調器10から送信される変調信号SRFとを掛け算して復調信号SDMを生成する。このとき、局部発振信号SLOと周波数同期した変調信号SRFとの間の位相差に応じて復調信号SDMにDC成分が発生する。DC補正部50は、復調信号SDMのDC電圧Vdcを検出し、検出したDC電圧Vdcが予め設定されている基準電圧となるように補正する。

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

無線周波数集積回路

【課題】無線周波数集積回路において位相エラーを十分に低減する。

【解決手段】無線周波数集積回路は、与えられた電圧に応じた発振周波数の発振周波数信号を生成する電圧制御発振器を有し、発振周波数信号を分周して得られる搬送波に信号波を乗せた無線周波数信号を生成する送信部と、無線周波数回路からの前記無線周波数信号を増幅する電力増幅器と電力増幅器から送信部に回り込む、少なくとも前記発振周波数の同じ周波数の高調波成分を低減する低減手段と、

を有する。

(もっと読む)

PLL回路

【課題】VCOのVT端子側から見えるバラクタダイオード数を減少させることによりリファレンスリークを低減するPLL回路を提供する。

【解決手段】PLL回路を構成するループフィルタから出力されるVCO制御電圧とVCOを予め関連付けて設定し、ループフィルタのVCO制御電圧に基づいて対応するVCOを選択し、該VCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を制御する切替信号を生成するVCO切替回路と、切替信号に基づいて、選択されたVCOのみの電圧制御発振器制御電圧端子とループフィルタの出力端子を接続し、他のVCOの電圧制御発振器制御電圧端子とループフィルタの出力端子との接続を解除するVT選択回路と、を備えるVCOの制御電圧端子にバラクタダイオードが接続された、発振周波数帯域の異なる複数のVCOを備えるPLL回路である。

(もっと読む)

発振回路、発振回路を持つ装置、および発振方法

【課題】局部発振周波数を制御する制御電圧を得る際に用いられる電源回路(DC/DCコンバータ)の内部発振周波数に起因する障害を回避する。

【解決手段】電源回路10と電圧制御発振器13と基準発振器15と電圧制御発振器の発振周波数f(VCO)を電圧制御する制御回路16を備える。電源回路10は内部発振器11の発振信号Voから所定電圧Vzを提供する。電圧制御発振器13は可変容量ダイオード14に印加される制御電圧Vcontによって発振周波数が変化する。制御回路16は、基準発振器15の発振周波数f(REF)に基づく比較周波数f(COMP)とf(VCO)に基づく検査周波数f(CHK)との比較結果によりVcontを制御する。Vcontは所定電圧Vzを用いて生成される。ここで、Nを自然数としたときに、内部発振器11の発振周波数f(DD)が比較周波数f(COMP)のN倍より高くN+1倍より低くなるようにする。

(もっと読む)

正確で安定したLC型基準発振器のための方法、システム、および装置

【課題】周波数の安定性およびジッタの要件を満たしつつ、CMOS技術における既存の最適化プロセスの手順に依拠した集積化の解決手法を利用した、温度に対して非依存型のLC型発振器を提供する。

【解決手段】実質的に温度に非依存のLC型発振器は、温度ヌル位相に実質的に等しい位相でタンク発振を生成するLC発振器タンク10を用いて達成される。該温度ヌル位相は、LC型発振器の出力発振の周波数の温度変化に伴う変動が最小化されるときの、LC発振器タンク10の位相である。該LC型発振器はさらに、該LC発振器タンク10に接続されて、該温度ヌル位相に実質的に等しい位相で該LC発振器タンク10を発振させる周波数安定化回路を含む。

(もっと読む)

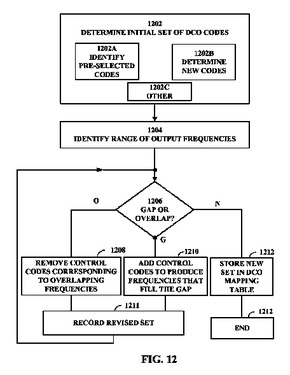

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

局部発振信号生成装置、信号受信装置、及び同期装置

【課題】局部発振信号を生成する装置において、発生するスプリアスを低減させること。

【解決手段】局部発振信号生成装置であって、第一の基準クロックを生成する第一基準クロック生成部と、第一の基準クロックとは異なる周波数の第二の基準クロックを生成する第二基準クロック生成部と、局部発振信号の生成において用いられる基準クロックを、第一の基準クロックと第二の基準クロックのうち、発生するスプリアスがより小さくなる方を選択する選択部と、選択された基準クロックを用いて局部発振信号を生成する局部発振部と、を備える。

(もっと読む)

PLL回路

【課題】 広い周波数範囲が必要とされるPLL回路において、そのPLL特性を一定に保つことができるようにするとともに、そのための構成を簡単化する。

【解決手段】 VCO11と、その発振信号を1/Nの周波数に分周する可変分周回路12と、その分周信号と基準信号とを位相比較する位相比較回路13とを設ける。位相比較回路13の比較出力から分周信号と基準信号との位相差に対応してパルス幅の変化するチャージポンプ電流ICPを出力するチャージポンプ回路14と、チャージポンプ電流ICPが供給されて分周信号と基準信号との位相差に対応してレベルの変化する電圧を出力するとともに、この電圧をVCO11にその制御電圧として供給するループフィルタ15とを設ける。VCO11の発振周波数と、PLL帯域を設定するための係数との関数として、チャージポンプ電流ICPの値を計算してチャージポンプ回路14に設定する制御回路22を設ける。

(もっと読む)

周波数補正回路及びそれを用いた無線通信装置

【課題】 発振器の出力周波数が増減した場合に自動補正を可能として常に出力周波数の精度を一定の範囲内に維持する周波数補正回路を得る。

【解決手段】 発振器2の発振周波数よりも高精度の基準周波数を、発振周波数を分周した分周周期毎に計数するカウンタ5と、発振周波数が正常な時のカウンタの計数値に相当する正常値に対して所定値Mを加算した値とカウンタの計数値とを比較して一致したときに発振周波数の減少を示す信号を生成する比較回路7と、正常値に対してMを減算した値とカウンタの計数値とを比較する比較回路8と、この比較回路8の一致結果に応答してこの一致結果を所定時間マスクするためのマスク信号を生成する単安定マルチバイブレータ11と、比較回路7の減少を示す信号に応じて発振周波数を減少方向に制御し、マスク信号の非生成時に発振周波数を増加方向に制御する制御回路12及びCPU1とを含む。

(もっと読む)

局部発振信号発生装置の検査方法

【課題】発振周波数可変域の異なる複数の電圧制御発振器を有する局部発振信号発生装置を検査するための検査方法であって、安価な半導体検査装置を用いて実現可能であり且つ検査効率のよい検査方法を提供する。

【解決手段】発振周波数可変域の異なる複数の電圧制御発振器1_1〜1_nを有する局部発振信号発生装置を検査するための検査方法であって、前記複数の電圧制御発振器1_1〜1_nの各発振周波数可変域の上端周波数及び下端周波数のうち一部のみ(例えばfA,fB)を探索し、その探索結果を用いた演算によって得られた周波数ポイント(例えばfD)の正常発振の有無を判定することにより、発振周波数可変域が隣接する電圧制御発振器同士において発振周波数可変域が規定以上重複していることを検査する検査方法。

(もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

1 - 20 / 38

[ Back to top ]