Fターム[5J106CC52]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数変換回路 (1,116) | 分周回路 (990)

Fターム[5J106CC52]の下位に属するFターム

可変分周回路 (277)

Fターム[5J106CC52]に分類される特許

501 - 520 / 713

位相同期ループ回路及びこの位相同期ループ回路で使用される制御方法

【課題】基準クロックに異常が発生しても、この異常に対処し得る位相同期ループ回路を提供する。

【解決手段】カウンタ111にて外部クロック信号から内部クロック信号に同期した矩形波信号を生成するとともに、カウンタ112−2にて内部クロック信号から外部クロック信号の異常を検出するために必要なウインドウ信号を生成し、異常判定制御部114−2にて矩形波信号の立ち上がりがウインドウ信号のハイレベル期間内に入っているか否かを判定し、入っていない場合に、矩形波信号の立ち上がりがウインドウ信号のハイレベル期間内に入るようにカウンタ111を制御すると共に、スイッチ13のオン/オフを制御して、電圧制御水晶発振器12への制御電圧の供給を制御するようにしている。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子側のインピーダンスを低くし、VCOの位相雑音特性の劣化を防ぎ、VCOの固体バラツキや温度変化に対して固有周波数を一定値に保つVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータをアナログ出力する粗調用DAC4と、微調用周波数のデジタルデータをアナログ出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを抵抗R6 で接続し、LPF5の出力とLPF7の出力とをコンデンサC8 で容量結合し、LPF7に電圧制御手段としての可変抵抗R4 を設けたVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

PLL周波数シンセサイザ回路

【課題】スプリアス信号がシンセサイザ回路の基準周波数信号に含まれると、発振出力信号のS/Nが著しく低下し、受信機の復調音声中に可聴音として出力される不具合が生じる。発明は、希望信号周波数近傍のスプリアスであっても、これを除去し得る機能を備えたPLL周波数シンセサイザ回路を提供することを目的とする。

【解決手段】電圧制御発振器、位相比較器、低域フィルタ、可変分周手段、を備えたPLL周波数シンセサイザ回路において、基準周波数信号に含まれる不要交流信号成分と振幅が同一で位相が逆相のレプリカ信号を生成し、該レプリカ信号によって前記不要交流信号成分を相殺除去するように構成する。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子からみたインピーダンスを低くして、VCOの位相雑音特性の劣化を防ぐことができるVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータを入力し、アナログ信号を出力する粗調用DAC4と、微調用周波数のデジタルデータを入力し、アナログ信号を出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを接続する抵抗R6 と、LPF5の出力にLPF7の出力が加算されるよう容量結合するコンデンサC8 とを有するVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

PLL回路及び半導体装置

【課題】本発明は、PLL回路及び半導体装置に関し、電源電圧が比較的低くても、半導体集積回路の微細化を難しくすることなく消費電力の増大を防止することを目的とする。

【解決手段】入力信号とフィードバック信号とが入力される位相比較器と、位相比較器の出力で制御されるチャージポンプと、チャージポンプの出力が入力されるローパスフィルタ部と、ローパスフィルタ部の出力により制御される電流制御発振器と、電流制御発振器の出力を分周してフィードバック信号を出力する分周器とを備え、ローパスフィルタ部は、チャージポンプの出力と基準電圧が入力される増幅器と、コンデンサ及び抵抗からなりチャージポンプの出力と増幅器の出力が入力される回路部分を含むように構成する。

(もっと読む)

送信装置及び制御方法

【課題】FSK無線送信機10において、電圧制御発振器136へのFSK変調データのDCオフセットにもかかわらず、各論理値に対応する送信波の周波数を適格化する。

【解決手段】A/D変換器15は、FSK変調データの電圧をA/D変換して、CPU14へ送る。選択チャンネルの送信波の指示周波数をfoとする。また、FSK変調データの各論理値に対応して周波数軸方向上側及び下側に生じる送信波の周波数をそれぞれfu,flとし、fu,flの中心点の周波数を中心点周波数fmと呼ぶことにする。CPU14は、検出したDCオフセット量に基づいて、DDS12の設定データを調整することにより、DDS12の出力周波数を制御する。DDS12の出力周波数は、中心点周波数fmがfoとなるようなものに制御される。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】クロックの周波数成分を広く拡散できるアナログ処理で変調信号を生成し、効率的な回路構成で変調信号についても周波数拡散させることで、スペクトラム成分をさらに分散できる、スペクトラムのピークの低減率が高いスペクトラム拡散クロック発生回路を提供する。

【解決手段】スペクトラム拡散クロック発生回路に、基準クロックと帰還クロックの位相を比較し位相差に応じた誤差信号を出力する位相比較手段と、前記誤差信号を平滑化するループフィルタと、平滑化された誤差信号を変調してスペクトラム拡散変調信号を生成する変調生成手段と、前記スペクトラム拡散変調信号に応じた周波数のクロックを生成するクロック生成手段とを備え、前記変調生成手段が、周波数が拡散された変調信号を生成するようにすることにより上記課題を解決する。

(もっと読む)

PLL回路

【課題】位相比較周波数が低い場合、ループフィルタのカットオフ周波数も低くなり、PLL回路の同期確立に多大な時間を要する。

【解決手段】微少な位相比較出力をA/D変換器8で認識することが可能な直流電圧とする手段を用いる。この手段5は、位相比較クロックの周波数よりはるかに高いカットオフ周波数のRC積分回路を備え、位相差の時間のみコンデンサに電荷をチャージして直流電圧へ変換する。チャージ時間が終わるとチャージされた最大電圧値がA/D変換器でホールドされる。これにより、1クロック前の位相比較からのずれを算出し、VCO制御電圧を出力するD/A変換器12の設定値を、算出した誤差分だけ変動させる。

(もっと読む)

マイクロコンピュータ

【課題】温度が変化する環境下において、CR発振回路を利用して生成されるクロック信号の発振周波数自体が一定となるように補正できるマイクロコンピュータを提供する。

【解決手段】マイクロコンピュータのEEPROMに、温度により変動するCR発振回路の発振周期データを記憶しておき、CPUは、温度検出回路によって検出される温度に応じてEEPROMに記憶されているデータを読み出し(ステップS2,S3)、決定した逓倍値をDPLL回路に設定することで(ステップS4,S5)逓倍クロック信号の発振周波数を補正する。

(もっと読む)

クロック再生装置

【課題】本発明はクロック再生装置に関し、バーストモードに対応でき、また10Gbps以上の高速通信の場合にも安定に発振することができるクロック再生装置を提供することを目的としている。

【解決手段】入力データを受けて該入力データからパルスを作成するパルス作成回路20と、ゲート付きオッシレータ31と、該ゲート付きオッシレータ31の出力と基準クロックとを比較し、その比較結果により前記ゲート付きオッシレータ31に遅延時間を設定するための位相制御信号を与える周波数コントロール回路32から構成されるクロック再生回路30と、によりなり、前記パルス作成回路20の出力で前記ゲート付きオッシレータ31をリセットすると共に、当該ゲート付きオッシレータ31の出力をクロック再生出力とするように構成される。

(もっと読む)

位相同期発振器

【課題】基準信号に位相同期した信号を出力する位相同期発振器に関し、定常位相誤差を任意に制御可能とする。

【解決手段】位相比較出力部1とローパスフィルタ2と電圧制御発振器3とを含み、基準周波数frの信号位相に、電圧制御発振器3の出力周波数foutの信号又は分周器4により分周した信号を比較周波数fpの信号として位相同期化させる位相同期発振器に於いて、基準周波数frの信号と比較周波数fpの信号との位相比較を行う位相比較出力部1のチャージポンプの出力信号をローパスフィルタ2に入力し、そのローパスフィルタ2の入力端子に、電圧Vccを印加する為の第1の可変抵抗5と、アースに接続する為の第2の可変抵抗6との何れか一方又は両方を接続した構成を有するものである。

(もっと読む)

クロック再生装置

【課題】本発明はクロック再生装置に関し、バーストモードに対応でき、また20Gbps以上の高速通信の場合にも安定に発振することができるクロック再生装置を提供することを目的としている。

【解決手段】ゲート付きオッシレータ25と、該ゲート付きオッシレータ25の出力と基準クロックの位相とを比較し、その比較結果により前記ゲート付きオッシレータ25に遅延時間を設定するための位相制御信号を与える周波数コントロール回路26から構成されるクロック再生回路10と、によりなり、前記ゲート付きオッシレータ25は内部に2系統の発振回路を有しており、該ゲート付きオッシレータ25のリセット入力端子に入力データを入力し、該入力データが“H”の時と“L”の時とで異なるルートの発信回路を動作させるように構成される。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、オーバーヘッドを低減することができるクロック生成技術を提供する。

【解決手段】外部から入力されたクロックを逓倍するPLL回路109aと、PLL回路109aで逓倍されたクロックを分周してシステムクロックを生成する分周回路110a及び選択回路111cと、外部から入力されたクロックを逓倍するPLL回路109bと、PLL回路109bで逓倍されたクロックを分周して通信回路用クロックを生成する分周回路110b及び選択回路111dとを有し、PLL回路109aは、リセット後、次のリセットまでに再設定可能であり、PLL回路109bは、リセット後、次のリセットまでは再設定できない半導体集積回路装置。

(もっと読む)

位相同期回路

【課題】簡単な構成により高精度な発振位相(周波数)で同期発振と自走発振の切り替え制御を可能とし、正常な同期発振状態及び自走発振状態でアラームを発生しないアラーム回路を備える位相同期回路を提供する。

【解決手段】電圧制御発振器6の出力と同期クロックとの位相を比較する位相比較器2に供給電源をオンオフする電源制御回路10を設けるとともに、ループフィルタ4の出力に電圧制御発振器6の自走発振用の電圧を印加する電圧発生回路8を備える。電源制御回路10の電源のオンオフ制御により電圧制御発振器6の同期発振と自走発振の切り替えが可能である。また位相比較器2の出力に閾値により異常を検出するアラーム回路の3を備える。位相同期動作の異常時にアラーム回路3はアラームを出力するが、前記電源制御回路10で電源供給をオフ状態に切り替え、電圧制御発振器を自走発振の動作にするとアラームはノーマルに戻る。

(もっと読む)

位相比較回路およびそれを用いたPLL周波数シンセサイザ

【課題】高速に周波数切り換えが可能であり、且つ小型でスプリアスを低減することが可能な位相比較回路を提供する。

【解決手段】本発明の一実施形態に係る位相比較回路は、制御回路からの制御信号に基づいて、クロックを分数分周した分数分周信号を生成する分数分周器と、分数分周信号を整数分周した第1の整数分周信号を生成する第1の整数分周器と、基準クロックを整数分周した第2の整数分周信号を生成する第2の整数分周器と、切換信号に基づいて、分数分周信号と第1の整数分周信号とのいずれか一方を選択的に出力する第1の選択回路と、制御回路からの切換信号に基づいて、基準クロックと第2の整数分周信号とのいずれか一方を選択的に出力する第2の選択回路と、第1の選択回路からの出力信号と第2の選択回路からの出力信号との周波数差および位相差を表す比較信号を生成する位相比較器とを備えている。

(もっと読む)

半導体装置

【課題】PLL回路のロックタイムを短縮しつつ、ロック時のチャージポンプのリーク電流を削減して安定した出力信号を供給する半導体装置を提供する。

【解決手段】一の電源電圧と接続され、半導体基板上に位相同期ループ回路1を配設する半導体装置において、位相同期ループ回路には、複数の回路ブロック2、3、5、6が備わり、半導体基板上には、一の電源電圧から電圧値の異なる電圧を生成して、回路ブロックごとにそれぞれ電圧値の異なる電圧を供給する複数の電源電圧供給手段7、8、9と、かかる電源電圧供給手段から生成された電圧の何れか一つを回路ブロックのうちの少なくとも一つの回路ブロックに含まれるPMOSトランジスタ基板に選択的に供給することにより電圧の供給先となる回路ブロックの出力を制御する供給電圧制御手段10と、を備えることを特徴とする。

(もっと読む)

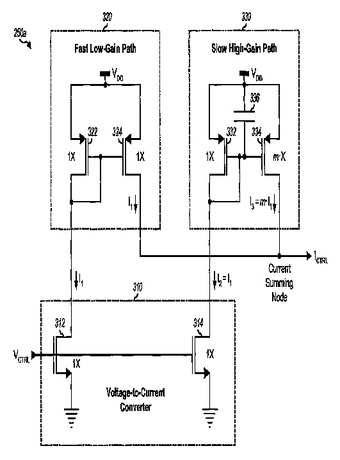

電流−モード利得分割デュアル−パスVCO

大きな電圧制御オシレータ(VCO)利得を効率的に取り扱うための技術が記載される。本技術は、(1)VCOの中心周波数を調節する平均制御電流を供給するための低速高利得パス、及び(2)通常動作の間VCO周波数を調節する瞬間的な制御電流を供給するための高速低利得パス、を利用する。1つのデザインでは、VCOは、電圧−電流コンバータ、電流増幅器、総和器、及び電流制御オシレータ(ICO)を含む。電圧−電流コンバータは、制御電圧を受け取り、そして第1電流と第2電流とを発生する。電流増幅器は、第1電流を増幅しそしてフィルタし、そして第3電流を発生する。総和器は、第2電流と第3電流を合算し、そして制御電流を発生する。ICOは、制御電流を受け取り、そして制御電流により決定される周波数を有するオシレータ信号を発生する。  (もっと読む)

(もっと読む)

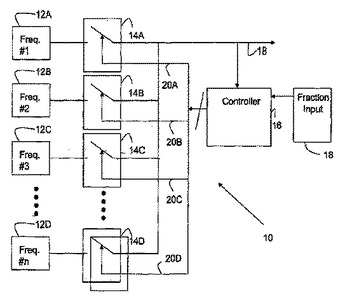

高速スイッチングのための周波数合成の新規方法

単一のソースの設計、マルチプレクサの設計、分数分周器の設計、または周波数逓倍器と周波数分周器の設計で実装可能なデジタル周波数シンセサイザである。実装は、制御器のディザリング回路またはデルタシグマ変調器を利用可能である。この周波数シンセサイザは、CMOS構成において実装可能であり、クリーンアップ位相ロックループ(PLL)を利用可能である。  (もっと読む)

(もっと読む)

チャージポンプ回路

【課題】 チャージポンプ回路へ入力されるアップ信号、ダウン信号が短いパルスであった場合でも、電流源Tr(トランジスタ)のゲート電位の変動を防ぎ、出力電流の立ち上がり時間を小さくし、高速で動作する、不感帯が低減されたチャージポンプ回路を得る。

【解決手段】 各ゲート端子に共通にバイアスされ、それぞれのゲート・ソース間容量がほぼ等しい充電用電流源Trと充電用ダミーTrの一方のソース端子での電位の増加量と他方のソース端子での電位の減少量をほぼ等しくするようソース端子の接続先を切り替え、充電用電流源Trと放電用電流源Trのドレイン端子同士を接続して出力端子とし、放電用電流源Trと放電用ダミーTrで前記充電用回路と同様に放電用回路を形成し、一方のソース端子での電位の増加量と他方のソース端子での電位の減少量をほぼ等しくするようソース端子の接続先を切り替える。

(もっと読む)

カウント値を維持した後で出力するカウンタ及び該カウンタを備える位相固定ループ

【課題】カウント値を維持した後で出力するカウンタ及び該カウンタを備える位相固定ループを提供する。

【解決手段】選択部及びカウント部を備えるカウンタ。選択部は、所定の選択信号に応答して、クロック信号またはホールド信号を選択して出力する。カウント部は、クロック信号をカウントし、ホールド信号に応答してクロック信号をカウントしたクロック数を維持した後に、維持したクロック数を出力する。これにより、伝搬遅延時間に関係なく安定的にカウント値を出力しうる。

(もっと読む)

501 - 520 / 713

[ Back to top ]