Fターム[5J106DD19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442) | アップダウンカウンタ (62)

Fターム[5J106DD19]に分類される特許

21 - 40 / 62

PLL回路

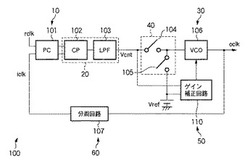

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部と、を有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記生成部から出力された前記制御電圧と前記参照電圧とを比較し、前記生成部から出力される制御電圧が前記参照電圧に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

PLL回路

【課題】PLL回路におけるPLL応答特性を、参照電圧に応じた所望の特性にする。

【解決手段】PLL回路は、入力された電圧に応じた周波数で発振することにより、内部信号を生成する発振部と、前記内部信号を分周して分周信号を生成する分周部と、外部から入力された基準信号の位相と前記分周部から受けた前記分周信号の位相とを比較し、比較結果に応じた位相誤差信号を出力する位相比較部と、前記位相誤差信号に基づいて制御電圧を生成する生成部とを有するPLL回路であって、前記生成部から出力された前記制御電圧が前記発振部へ入力される第1の状態と、参照電圧が前記発振部へ入力される第2の状態とを切り替える切り替え部と、前記第2の状態において、前記分周信号の周波数と前記基準信号の周波数とを比較し、前記分周信号の周波数が前記基準信号の周波数に等しくなるように、前記発振部に入力された電圧に対する前記発振部における発振する周波数を補正する補正部とを備える。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

発振回路、DC−DCコンバータ及び半導体装置

【課題】CPUなどの特別な制御回路が不要で、しかも無線送受信回路で用いている周波数に関わりなく、スイッチングノイズの影響を無視できるレベルまで軽減することが可能な発振周波数制御回路を提供する。

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

DLL回路

【課題】補間回路の最小動作周期を低減でき、DLLの最大動作周波数を向上させることができる、DLL回路を提供する。

【解決手段】位相検知回路21は、入力される基準クロック信号とレプリカ回路17から出力されるクロック信号との位相の差を検知し遅延制御回路22に出力する。遅延制御回路22は、位差の信号を基に、基準クロック信号の位相を調整する制御信号を出力する。そして、遅延制御回路22から出力される制御信号を基に、マルチプレクサ12、13は、粗調整遅延回路10からインバータ2段分の遅延差を有する信号を選択して出力し、第1の微調整遅延回路14は、マルチプレクサから入力した2段分の遅延差の信号を基に、インバータ1段分の遅延差を有する信号を出力する。第2の微調整遅延回路15は、この1段分の遅延差を有する信号に基づいてクロック信号の位相を調整する。

(もっと読む)

遅延同期ループ回路および表示装置

【課題】所望の単位遅延回路の1個分の遅延追加がなされた場合であっても不安定な単位遅延回路が連続しないようにすること。

【解決手段】本発明は、外部クロックと内部クロックとの位相差を比較する位相比較器1と、位相比較器1からの出力信号により遅延時間を制御するアップダウンカウンタ2と、外部クロックの遅延を制御して内部クロックとするため、アップダウンカウンタ2から出力される信号の複数ビットに対応した複数個の単位遅延回路(Delay-Cell)を備え、この複数個のDelay-Cellを直列に接続するにあたり、アップダウンカウンタ2からの出力における同一ビットの出力により制御されるDelay-Cellが隣り合わないよう接続されるデジタル遅延ライン3とを有する遅延同期ループ回路である。

(もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

デジタル位相ロックループを実施するためのシステム及び方法

【課題】デジタル位相ロックループを実施するシステム及び方法を提供する。

【解決手段】デジタル位相ロックループを実施する装置は、VCO制御電圧に応答して1次クロック信号を発生する電圧制御式発振器を含む。検出手段は、カウントアップ信号及びカウントダウン信号を含むカウンタ制御信号を発生し、1次クロック信号と基準信号の現在の関係を示す。アップ/ダウンカウンタは、次に対応するカウンタ制御信号に応答してカウンタ値を増分又は減分する。カウンタ値は、次に電圧制御式発振器により発生された1次クロック信号の周波数を調節するためにデジタル/アナログ変換器によってVCO制御電圧に変換される。代替実施形態では、上述のアップ/ダウンカウンタを利用して、デジタル/アナログ変換器でVCO制御電圧を発生する以外の適切な技術の利用により、カウンタ値に比例して電圧制御式発振器の周波数を調節することができる。

(もっと読む)

DLL回路及びこれを用いた半導体装置、並びに、DLL回路の制御方法

【課題】チップ上における占有面積が小さく、広範囲なクロック周波数に対応可能なDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させるディレイライン210と、ディレイライン210による遅延量を制御する制御回路とを備える。ディレイライン210は、従属接続された複数の可変遅延素子500を有し、可変遅延素子500は、バイアス電流量によって遅延量が変化する差動回路構成であり、制御回路は、バイアス電流量を設定する第1の制御部300と、複数の可変遅延素子500のうち出力を取り出す可変遅延素子を選択する第2の制御部400とを有している。本発明によれば、可変遅延素子によってディレイラインが構成されていることから、少ない段数にて広範囲なクロック周波数に対応することが可能となる。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】クロックの周波数が高い場合であっても、パルスの消失リスクが少ないDLL回路を提供すること。

【解決手段】DLL回路100において、CKとLCLKの各立ち上がりエッジの位相を比較して判定信号R−U/Dを生成する位相判定回路111と、CKとLCLKの各立ち下がりエッジの位相を比較して判定信号F−U/Dを生成する位相判定回路112と、判定信号R−U/Dに基づいてLCLKRのアクティブエッジの位置を調整する第1の調整回路と、判定信号F−U/Dに基づいてLCLKFのアクティブエッジの位置を調整する第2の調整回路と、LCLKRとLCLKFに基づいてLCLKを生成するクロック生成回路と、LCLKRのアクティブエッジの調整方向とLCLKFのアクティブエッジの調整方向とが互いに逆方向であることに応答して、第2の調整回路による調整動作を停止させる停止回路150とを備える。

(もっと読む)

クロック信号生成回路とクロック信号生成方法

【課題】複数系統の基準信号のいずれか、又は全てが断となってしまった場合でも、安定してクロック信号を生成することができるようにする。

【解決手段】断検出部2−A,2−Bで現用系の基準信号Aと予備系の基準信号Bの断を検出するようにし、断検出時には断検出信号を制御部8へ出力する。制御部8は、断検出部2−Aからの断検出信号を受け取ると、入力切替部1の導出を基準信号Bに切り替え、その後、断検出部2−Bからの断検出信号を通知されると、制御電圧保持部6の保持電圧の更新を停止させ、切替部7の導出を制御電圧生成部5で生成される制御電圧から制御電圧保持部6に保持される保持電圧に切り替える。

(もっと読む)

拡散スペクトラムクロック生成装置

【課題】回路規模を大きくせずにEMIを十分に低減できる拡散スペクトラムクロック生成装置を提供する。

【解決手段】拡散スペクトラムクロック生成装置は、クロック信号を生成するPLL(Phase Locked Loop)回路1と、クロック信号の周波数変調を行う周波数変調回路2とを備え、周波数変調回路2は、カウンタ11と、設定レジスタ12,13と、マルチプレクサ14と、1/P分周器15と、ラッチレジスタ16と、アップダウンカウンタ17と、設定レジスタ18と、加算器19とを有する。Hershey-kiss変調プロファイルの1周期分を8等分した各相対時刻ごとの変調ポイントを直線でつないだ変調プロファイルを用いて、1/N分周器8の分周比を1周期に8回変化させるため、Hershey-kiss変調プロファイル用の特性テーブルを設けなくても、Hershey-kiss変調プロファイルと同様の周波数変調を行える。

(もっと読む)

入出力回路

【課題】クロックアンドデータリカバリ回路の動作余裕度の大きさを最適化するSERDES回路の提供。

【解決手段】SERDE回路において、クロックアンドデータリカバリ回路(14)は、位相オフセット信号(31)と閾値電圧制御信号(32)を用いて、時間方向と電圧方向の動作余裕度を測定可能し、伝送路におけるISIを低減するためにプリエンファシスドライバ回路(21)とイコライザ回路(22)と、全体を制御するための最適化制御回路(23)を備え、最適化制御回路(23)は、イコライザ回路(22)の特性を調整するイコライザ制御信号(33)、プリエンファアイスドライバ回路(21)の特性を調整するドライバ制御信号(34)を制御可能であり、クロックアンドデータリカバリ回路(14)の動作余裕度を最大化するように設定することができる。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を安定させる。

【解決手段】位相検出器210は、位相補間器270からの同期クロックとシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。第1の積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。第2の積分器240は、位相補正制御信号をさらに積分してアップ/ダウン信号を得る。パターン発生器250は、アップ/ダウン信号からシリアルデータの周波数変動に追従するための周波数補正制御信号を生成する。パターン発生器250のパターン長と第2の積分器240のカウント幅の積は、第1の積分器230のカウント幅が大きいほど大きくなる大きさの閾値以上である。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を向上させる。

【解決手段】位相検出器210は、同期クロック信号とシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。積分器240は、所定の長さの平滑期間毎に位相誤差信号を積分して平滑誤差信号を得る。パターン発生器250は、所定の長さのパターン発生期間毎に、平滑誤差信号に応じた頻度で同期クロック信号の位相を変更するパターンを発生して周波数補正制御信号として出力する。積分器240は、周波数補正制御信号がフィードバックされ、該周波数補正制御信号における頻度の変動方向に応じて、平滑化期間の長さを変更する。

(もっと読む)

周波数切替え装置

【課題】 回路規模が大きくなるのを抑えることができ、動作中に周波数を切り替えたときにシステム誤動作が起きるのを防ぐことのできる周波数切替え装置を提供する。

【解決手段】 周波数切替え器5は、位相周波数比較器10と、チャージポンプ回路11と、LPF回路12と、VCO回路13と、カウンタ回路14と、カウンタ回路14の動作を制御する制御部8を備える。制御部8は、逓倍数変更部16と、変更許可判定部15を備える。変更許可判定部15は、カウンタ回路14のカウンタ値に基づいて、逓倍数を目標逓倍数に変更するのを許可するか否かを判定する。例えば、カウンタ値が目標逓倍数以下の基準値(例えば、カウンタ値0)になったときに、逓倍数の変更を許可する。

(もっと読む)

PLL同期はずれ検出回路

【課題】電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、PLL同期はずれ検出回路の検出精度を向上させることを目的とする。

【解決手段】基準クロックと電圧制御発振器3の出力クロックの位相を比較して位相差に対応する信号を出力する位相比較器1と、位相比較器の出力により出力クロックの周波数を調整する電圧制御発振回路を有し、電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、時間を計測するタイマ6と、電圧制御発振器の出力クロックをカウントし、タイマからの信号でリセットされるカウンタ5と、カウンタのカウントした値が判定値を超えると信号を出力し、電圧制御発振器の出力クロック周波数増加方向の同期はずれを検出する検出器とを備える。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

位相調整回路及びフェイズロックドループ回路

【課題】周波数の高いクロックを用いる事無く、小さな回路規模で実現でき、より細かい分解能で位相調整することができる位相調整回路及びフェイズロックドループ回路を提供する。

【解決手段】入力される水平同期信号SYNC_INは、位相シフト回路21により位相調整データCKPHASEの上位2Bitsの値に応じてシフトされ、その出力によりアップダウンカウンタ22はクロックNCKPをアップ及びダウンカウントして、逓倍回路32等経てラッチ回路23に出力し、ラッチ回路23は、データイネーブル用パルスENCKPによりラッチして、位相調整出力HD_SIGを出力する。

(もっと読む)

21 - 40 / 62

[ Back to top ]