Fターム[5J106DD19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 計数(カウンタ)回路 (442) | アップダウンカウンタ (62)

Fターム[5J106DD19]に分類される特許

41 - 60 / 62

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、第1、第2の信号(例えば、NCLK信号およびMCLK信号)の周波数が一致しているか否かを正しく判定できるようにした周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法を提供する。

【解決手段】NCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたUP信号を生成するエッジ検出回路111aと、MCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたDown信号を生成するエッジ検出回路111bと、UP信号及びDown信号をカウントし、そのカウント値をQ1、Q0信号で出力する2ビットアップダウンカウンタ112と、Q1、Q0信号に基づいて、NCLK信号の周波数とMCLK信号の周波数とが一致しているか否かを判定する判定回路113と、を有する。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、NCLK信号およびMCLK信号等の周波数が一致しているか否かを正しく判定できるようにする。

【解決手段】NCLP信号の分周信号であるNCLP2信号と、MCLP信号の分周信号であるMCLP2信号とを生成する。次に、MCLP2信号がHレベルのときはNCLP信号をアップ信号としてカウントし、MCLP2信号がLレベルのときはNCLP信号をダウン信号としてカウントし、そのカウント値をQN1、QN0信号で出力する。また、NCLP2信号がHレベルのときはMCLP信号をアップ信号としてカウントし、NCLP2信号がLレベルのときはMCLP信号をダウン信号としてカウントし、そのカウント値をQM1、QM0信号で出力する。そして、QN1、QN0、QM1、QM0の各信号に基づいて、NCLP信号とMCLP信号の各周波数が一致しているか否かを判定する。

(もっと読む)

PLL回路及びPLL回路を構成する可変ディレイラインの制御方法

【課題】 任意の幅で重なり合う発振レンジの設定を行い、PLL回路でのジッタの発生を抑制する。

【解決手段】 デジタルPLL回路10の発振制御回路2には、カウンタ制御回路11、第1のアップダウンカウンタ12、及び第2のアップダウンカウンタ13が設けられ、カウンタ制御回路11は、制御信号Scmが、ある値M=Xである状態からM=X+1である状態に変化するときに、制御信号Scnが段階的にアップカウントせずに、例えばスキップしてアップカウントが可能となる制御信号Smupと、制御信号Scmが、ある値M=X+1である状態からM=Xである状態に変化するときに、制御信号Scnが段階的にダウンカウントせずに、例えばスキップしてダウンカウントが可能となる制御信号Smdnとを入力する。このため、可変ディレイラインから出力されるディレイ信号は製造バラツキ、温度、及び電源電圧などの変動によらず任意の幅で重なり合う。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

デジタルPLL回路及びそれを備えた光ディスク装置

【課題】動作周波数が低く、安価にIC化を行うことができ、設計が容易なデジタル回路を用いて時間分解能の高いクロック信号を生成することができるDPLL回路を備えた光ディスク装置を提供する。

【解決手段】デジタルPLL回路部は、エッジ検出回路部と、クロックデータ生成回路部と、位相差検出回路部とを備え、一周期毎に、デジタルクロックデータから、デジタルクロック信号の立ち上がりエッジ又は立ち下がりエッジの有無を時間分解能単位で示した書き込みタイミング信号を生成して出力する。

(もっと読む)

クロック生成回路

【課題】逓倍回路から正確な逓倍クロックが出力されず、温度等の変動に対する補正能力が低下し、ロックが困難になるという課題があった。

【解決手段】互いに直列に接続された複数個の遅延素子から構成されるデジタルディレイライン56,69,71を有し、デジタルディレイライン56,69,71に対応したカウンタ52,65から出力されるカウント値に応じて複数の遅延素子のいずれかの遅延を選択し、選択した遅延素子およびこれに隣接する1つの遅延素子によって遅延時間を設定制御する。

(もっと読む)

クロック信号発生装置、クロック信号発生方法及びプログラム

【課題】位相の変化に迅速に追従しつつ、クロックスリップが起こり難い(安定した)クロック信号を再生するクロック信号発生装置等を提供することである。

【解決手段】位相比較器1Aは、データ信号と、デジタルVCO1Cの再生クロック信号を基準としたデータ信号の位相の遅れ及び進みを検出する。ランダムウォークフィルタ1Bは、この遅れ進みの回数差を計測して、回数差の絶対値が所定値に達すると、差を打ち消す方向に再生クロック信号の位相を変化させるようデジタルVCO1Cを制御し、計測結果をリセットして計測を再開する。再生位相比較器3は、デジタルVCO1C及び2Cの各再生クロック信号の位相差を検出してランダムウォークフィルタ1Bに通知する。ランダムウォークフィルタ1Bは、通知された位相差が所定量に達している間は、計測結果のリセットやデジタルVCO1Cの再生クロック信号の位相の変更を行わない。

(もっと読む)

電源電圧制御装置

【課題】システムクロック周波数に応じて自由にクロック周期設定マージンを設定でき、システムクロック周波数の変化に対し、内部回路を誤動作させずに短時間で電源電圧を正常に動作する最小電源電圧に収束させること。

【解決手段】電源電圧制御装置100は、システムクロックを分周比1で分周する分周回路121、電圧制御発振回路110の出力を分周比2で分周する分周回路122、分周回路121と分周回路122のそれぞれの出力信号を位相比較/周波数比較する位相比較器/周波数比較器130、及びコントローラ145内にメモリ142を備え、システムクロック周波数に連動した動作モード信号に応じて、制御回路141によりそれぞれの分周回路121,122の分周比を設定する。また、システムクロック周波数が変化する時に、コントローラ145内のプリセット値を用いてアップダウンカウンタ143の初期設定とレジスタ設定を行う。

(もっと読む)

マルチプレクサ機能と補間機能とが埋め込まれた電圧制御遅延線(VCDL)

電圧制御遅延線(VCDL)である。VCDL(120)は1つ以上のセル(125)を含む。この1つ以上のセルの各々は2つ以上の入力(Va、VaX、Vb、VbX)と出力(Vout、VoutX)とを含む。この1つ以上のセルの各々は、補間機能ならびにマルチプレクサ機能に加えて、遅延をもたらすように構成されている。VCDLは、遅延ロックループ(DLL)にて遅延をもたらすように使用される。  (もっと読む)

(もっと読む)

PLL制御のためのシステム及び方法

【課題】フェーズロックループ(PLL)回路に対するロジックの動作の影響を弱めるためのシステム及び方法を提供する。

【解決手段】システムと方法は、PLL回路が命令の予期される影響を命令の実行前、同時、あるいは後で補償することを実質的に許してもよい。より特に、システムの命令の発行に関連したロジックは、命令に基づいたシステムでのPLLに信号を供給してもよい。その後、PLLはこの制御信号に基づいた命令の予期される影響を補償するために調節されてもよい。

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

電圧保持回路及びクロック同期回路

【課題】本発明は、コストを抑制しつつ、入力された信号の電圧を長時間保持することができる電圧保持回路及び電圧保持回路を備えるクロック同期回路を提供することを目的とする。

【解決手段】 外部から入力される制御信号の電圧と、出力されるアナログ保持信号の電圧との比較結果を出力する電圧比較部110と、比較結果に基づいて、保持しているデジタル値である保持値を増減させ、保持値に基づいて生成されるデジタル値であるデジタル保持信号を出力するデジタル値保持部120と、デジタル保持信号をアナログ値に変換しアナログ保持信号として出力するD/A変換部130とを備える。

(もっと読む)

クロック生成回路、PLL及びクロック生成方法

【課題】発振周波数のスペクトラムを拡散して、電磁波輻射を低減させるクロック生成回路を提供することを目的とする。

【解決手段】

本発明は、基準クロックと動作クロックとが入力される位相比較器と、前記位相比較器の出力信号に基づいて前記動作クロックを生成する電圧制御発振器とを備えるクロック生成回路において、前記電圧制御発振器は、電圧信号を電流信号に変換する電圧電流変換器と、前記電流信号を可変とする電流可変回路と、前記可変電流信号に基づいた周波数を発振する電流制御発振器とを備えることを特徴とするクロック生成回路を提供する。

(もっと読む)

クロック再生回路

【課題】映像クロックの総累積値を制御入力としながら、送信側から伝送するクロック情報を小さくすることができるクロック再生回路を提供する。

【解決手段】レジスタ13は、クロックの累積値を自然数Nで除算した剰余であるクロック再生情報を保持し、レジスタ17は、VCXO25のクロックの累積値を前記自然数Nで除算した剰余を保持する。桁上がり・桁下がり判定器18,19はそれぞれ、レジスタ13,17の値から桁上がり又は桁下がりが発生したか否かを判定する。アップダウンカウンタ20は、桁上がり・桁下がり判定器18,19の桁上がり又は桁下がりの回数に応じて値を増減する。乗算器21は、アップダウンカウンタから出力をN倍する。加算器22は、レジスタ13の値とレジスタ17の値との差分値を乗算器21の出力に加算し、これをPLLの制御量とし、VCXO25を制御する。

(もっと読む)

分周回路およびデジタルPLL回路

【課題】出力信号に生じるジッタ量を抑えることができる分周回路を提供する。

【解決手段】直列に接続されたD−FF7,9,11を、入力信号S0を基準クロック信号として駆動し、分周比決定信号S21によって選択された分周比で入力信号S0を分周して第1の分周信号S7を生成する回路モジュール3と、直列に接続されたD−FF47,49,51,53を、第1の分周信号S7を基準クロック信号として駆動し、当該直列に接続されたD−FFの段数に応じた分周比である8分周で、第1の分周信号S7を分周して出力信号S57を生成する回路モジュール45と、回路モジュール45のD−FFの出力および4/5選択信号S24に基づいて、分周比決定信号S21を生成するOR回路55とを有する。

(もっと読む)

半導体装置及び発振周波数補正方法

【課題】 本発明は、半導体装置の動作時の発振周波数の変動要因に対応できるとともに、特定の通信機能や通信相手を必要とすることなく、RC発振回路の発振周波数の補正が可能な半導体装置を提供することを目的とする。

【解決手段】 半導体装置は、第1の周期で発振する第1の発振信号を出力するRC発振器と、RC発振器の出力に結合され第1の発振信号の第1の周期の長さを第2の周期を有する第2の発振信号に基づき計測し、その計測値を出力する計測回路と、計測回路の出力とRC発振器の出力とに結合され計測値に応じた数で該第1の発振信号を分周する補正回路を含むことを特徴とする。

(もっと読む)

ディジタル位相同期ループ回路

【課題】ディジタル位相同期ループ回路において制御発振部の追従性能を向上させる。

【解決手段】このディジタル位相同期ループ回路において、第2の分周器18は、第1の位相比較器10からの第1の同期制御信号(c),(d)にしたがって所定のマスタ・クロックを1/Nに分周して基準クロック(a)のM倍の周波数を有する出力クロック(g)を生成する。第2の位相比較器54は、基準クロック(a)の位相とフィードバック・クロック(b)の位相とを比較して、それらの位相差に応じた第2の同期制御信号(m),(n)を生成する。そして、レンジカウンタ(分周比制御部)56は、分周器18おける分周比Nを第2の同期制御信号(m),(n)にしたがって可変制御する。

(もっと読む)

デュアルループPLLおよび逓倍クロック発生装置

【課題】 初期起動においてロックアップ時間を短縮できるデュアルループPLL(Phase Looked Loop)を提供すること、および消費電力低減に寄与する逓倍クロック発生装置を提供すること。

【解決手段】 デュアルループPLLは、位相を比較する位相比較器1を有する位相比較ループと、周波数を比較する周波数比較器7を有する周波数比較ループとを有するデュアルループPLLを備え、周波数比較器7は、位相比較器1に用いる、外部基準クロックラインCLex11から入力される基準クロック信号と異なる、キャリブレーションクロックラインCLcal18から入力される入力信号を用いて周波数比較を行う。また、上記デュアルループPLLを用いて、逓倍クロック発生装置を構成する。

(もっと読む)

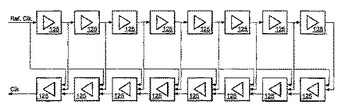

ディジタルPLL回路

周波数比較器は、基準クロックおよび出力クロックの周波数を比較し、周波数比較信号を出力する。周波数可変回路は、直列接続された複数の反転回路を有する遅延回路と第1選択回路とから構成される。第1選択回路は、奇数番目の反転回路から出力される奇数出力信号のいずれかを周波数比較信号に応じて選択し、帰還信号として遅延回路の入力に帰還させる。位相比較器は、基準クロックおよび出力クロックの位相を比較し、位相比較信号を出力する。第2選択回路は、奇数出力信号のいずれかを位相比較信号に応じて選択し、出力クロックとして出力する。周波数可変回路は、帰還ループを構成する反転回路の接続段数を調整することで、出力クロックの周波数を変更する可変発振器として機能する。遅延回路は、出力クロックの周波数調整および位相調整の両方に共通して用いられる。このため、回路規模を低減できる。  (もっと読む)

(もっと読む)

41 - 60 / 62

[ Back to top ]