Fターム[5J106DD24]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 同期化クロック制御回路 (365) | 移相・遅延量制御 (201)

Fターム[5J106DD24]に分類される特許

1 - 20 / 201

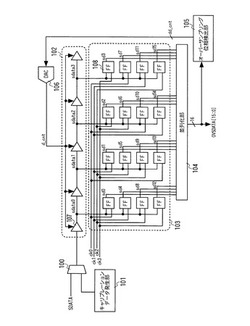

オーバーサンプリング回路及びそれを備えた通信装置

【課題】多相シリアルデータを多相クロックでサンプリングするオーバーサンプリング回路において、遅延量制御動作に伴う消費電流を低減する。

【解決手段】シリアルデータSDATAは、データ遅延部102により多相シリアルデータsdata0〜sdata3とされ、オーバーサンプリング部103において、多相クロックck0〜ck3により、オーバーサンプリングされる。データ遅延部102のデータ遅延素子107の遅延時間は、キャリブレーションデータ発生部101で生成されたデータのオーバーサンプリング出力の位相差をオーバーサンプリング位相検出部105により検出し、その位相差が所望の値となるように、遅延量制御デジタル信号dd_cntを調整する。遅延量制御デジタル信号dd_cntをデジタルアナログ変換部106によりアナログの遅延量発生信号d_cntに変換し、データ遅延素子107に供給する。

(もっと読む)

PLL回路

【課題】本発明は、遅延素子の遅延時間のばらつきを補償するように、デジタルコードを補正する必要のないTDCを提供することを目的とする。

【解決手段】基準信号の周波数に対して所望倍数の周波数を有する出力信号を出力する発振部と、基準信号についての出力信号の整数分周及び小数分周の和並びに当該所望倍数について差分を計算し、発振部に当該差分を0にするように出力信号を出力させる位相比較部と、を備えるPLL回路において、TDC2は、小数分周の初期値を設定し、初期値を計測値として出力するデジタルコード発生器23と、初期値に基づく位相比較部及び発振部の動作後に、当該差分を0にする方向に、小数分周の分解能を1ステップとして段階的に、小数分周を初期値から最適値へと更新し、最適値を計測値として出力するデジタルコード発生器23及び加減算器24と、を備える。

(もっと読む)

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

DLL回路、逓倍回路、及び半導体記憶装置

【課題】例えば、遅延クロックの位相と基準クロックの位相とを同期させるためのロック時間を低減する。

【解決手段】1つの実施形態によれば、ディレイチェーン、複数の位相比較器、制御部を有するDLL回路が提供される。ディレイチェーンでは、複数段の遅延素子が直列に接続されている。複数段の遅延素子は、基準クロックに対して互いに異なる遅延量のクロックを発生させる。複数の位相比較器は、基準クロックをそれぞれ受けるとともに、複数段の遅延素子における互いに異なる段の遅延素子からクロックを受ける。制御部は、複数の位相比較器による比較結果に基づいて、複数段の遅延素子のうち基準クロックに対して位相が同期するクロックを発生させる段数を決定する。制御部は、遅延クロックを出力するように、その決定された段数に基づいて複数段の遅延素子における出力段数を選択する。遅延クロックは、基準クロックが要求に応じた遅延量で遅延されたクロックである。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

クロック生成回路、クロック生成方法および半導体集積回路

【課題】占有面積や定常位相誤差の増大、並びに、クロックが安定するまでに長時間を要することなく、スペクトラム拡散クロックを生成してEMI対策を図る。

【解決手段】基準信号CK1を受け取って、立ち上がりエッジの傾き、または、立ち下がりエッジの傾き、または、立ち上がりエッジおよび立ち下がりエッジの傾きを、周期的に変化させた第1信号CK2を生成する第1回路4と、前記第1信号を受け取って、周期的に周波数が変化するクロックを生成する第2回路5と、を有する。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

多相信号を生成するための方法、回路及びシステム

【課題】位相誤差を補償しながら設定可能な位相オフセットで多相信号を生成するための方法等を提供する。

【解決手段】一実施形態において、回路は、第1の周波数及び第1の位相を有する第1の周期信号を生成する第1のLC型電圧制御発振器(LCVCO)と、第2の周波数及び第2の位相を有する第2の周期信号を生成する第2のLCVCOとを有し、第2の位相は、90度オフセットで第1の位相に対してオフセットされる。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

ラッチ回路、CDR回路、および受信装置

【課題】 消費電力を抑えた受信回路を提供する。

【解決手段】 本発明では、差動信号を差動増幅させる際に、差動入力によって発生する電流を対となる差動出力により遮断することで差動信号をラッチする回路を提供する。該ラッチ回路の適用により、受信信号の差動信号電圧差が小さい場合でも伝送データを受信できる為、増幅用アンプの削減が可能となり、受信装置の消費電力の低減を図ることができる。

(もっと読む)

デジタルクロックリカバリ回路及び半導体チップ

【課題】小型で、省電力で、かつパルスベースの超高速シリアル転送にも用いることのできるデジタルクロックリカバリ回路(CDR)を実現することを目的とする。

【解決手段】デジタルロックループ(DLL)、エッジ検出器、デジタルコンパレータ等を用いて、データ信号にDLLクロック信号をロックさせ、全ての回路要素をデジタル回路で構成し、クロックデータリカバリ(CDR)を実現する。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

DLL回路

【課題】従来のDLL回路では、クロック信号の立ち上がりエッジと立ち下がりエッジとで遅延時間に差が生じる問題があった。

【解決手段】本発明のDLL回路は、入力クロック信号φinに制御電圧Vlfに応じた遅延量を与える遅延バッファBUF1〜BUF4と、入力クロック信号φinを反転させるインバータとINV1、INV2、を含み、入力クロック信号φinを遅延させた出力クロック信号φoutを生成するディレイライン10と、入力クロック信号φinと前記出力クロック信号φoutとの位相差に基づいて制御電圧Vlfを生成する制御電圧生成部とを有し、ディレイライン10は、インバータINV1と遅延バッファBUF1、BUF2とを含む第1の遅延部と、第1の遅延部の後段に設けられ、第1の遅延部と同数のインバータ及び遅延バッファ(INV2、BUF3、BUF4)を含む第2の遅延部と、を有する。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の外部に接続される半導体チップのプロセス状態を検出して、マスク解除信号に対する制御信号のセットアップ時間またはホールド時間のマージンを大きくする。

【解決手段】 モニタモード中に、通常より低い参照電位を受信回路に供給して伝送信号の論理レベルを判定することで、半導体集積回路の外部に接続される半導体チップのプロセス状態を検出する。検出したプロセス状態に応じて可変遅延回路を制御し、内部同期信号および外部同期信号の少なくともいずれかの遅延時間を調整する。これにより、内部同期信号に応じて生成されるマスク解除信号に対する半導体チップからの制御信号のセットアップ時間またはホールド時間を、半導体チップのプロセス状態に拘わらず一定にできる。

(もっと読む)

クロック生成回路及びこれを備える半導体装置、並びに、クロック信号の生成方法

【課題】クロック信号の周波数に依存しないデューティ調整回路が搭載されたDLL回路を提供する。

【解決手段】内部クロック信号ICLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を指定するカウンタ回路123と、カウンタ回路123のカウント値を調整するカウンタ制御回路122と、内部クロック信号ICLKとレプリカクロック信号RepCLKのライズエッジが一致する第1及び第2のカウント値との差分を演算する減算回路133とを備え、得られた差分の1/2に相当する値に基づいて、内部クロック信号LCLKのフォールエッジを調整する。これにより、キャパシタを交互にディスチャージするタイプのデューティ調整回路を用いた場合のように、適用可能な周波数帯域が限られることがない。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

1 - 20 / 201

[ Back to top ]