Fターム[5J106DD36]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | A/D変換器 (140)

Fターム[5J106DD36]に分類される特許

1 - 20 / 140

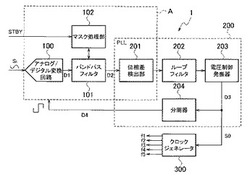

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

周波数シンセサイザ

【課題】 外部基準信号の入力断からスイッチを切り替えて一定の電圧を発振器の制御電圧として出力するに際して、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号が「断」となった場合には、SW3に可変電圧供給回路12からの出力電圧にループフィルタ4に出力させる切替信号を出力し、更にループフィルタ4からの出力電圧を1/N分圧器13で分圧した電圧を微調制御電圧とし、オフセット電圧供給回路15からの電圧を粗調電圧として加算器14で加算してOCXO5の制御電圧として出力する周波数シンセサイザである。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

水晶発振器回路の温度依存性及び処理依存性周波数変動を低減させるシステム及び方法

【課題】無線通信エレメントの発振器に於いて、共振器の温度依存性に対する処理の変動を補償する発振器の提供。

【解決手段】発振器210は、アクティブ・エレメント312と並列に共振器310を含み、共振器は、可変静電容量を有する可変コンデンサ314に結合し、発振器の出力周波数同調を可能にする。所定の温度補償算出器324は温度センサ322からの温度信号に基づき、共振器のロットに対して行われる特徴付けデータを参照して、温度ベースの周波数補償信号を出力する。又、周波数推定器326からの周波数推定信号に基づき、処理補償算出器328は共振器の処理依存性補償を算出して処理ベースの補償信号を出力し、乗算器330は前記周波数補償信号及び前記補償信号に基づき乗算器出力信号を出力し、制御モジュール332は、乗算器出力信号に基づき、制御信号を可変コンデンサに供給し、共振器における温度、処理ベースの変動を補償する。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

高周波発振源

【課題】位相雑音の劣化を抑制することができる高周波発振源を得ることを目的とする。

【解決手段】所定の周波数で発振する基準発振器1と、その基準発振器の出力波が注入されていない場合の発振周波数が、その基準発振器の出力波の周波数の整数倍に設定されている(または設定される)注入同期発振器とを備え、その基準発振器から注入同期発振器に注入される電力を、注入同期発振器の低離調周波数の位相雑音が基準発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように、かつ高離調周波数の位相雑音が注入電力がない時の注入同期発振器の位相雑音と(同じ周波数で比較した場合に)等しくなるように適切な注入電力とする電力調整手段を設ける。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

PLL回路

【課題】 基準周波数断時におけるフリーランの出力周波数の精度を向上させるPLL回路を提供する。

【解決手段】 比例積分方式のPLL回路を用いて、積分器14の後にA/D変換部15とパタン生成部16を付加した構成とし、A/D変換部15が、ロック時の積分器14の出力電圧をデジタル信号として得て、ロック外れ時はロック時のデジタル信号を保持する機能を備え、ロック外れ時で基準周波数断時には、保持したデジタル信号に応じてパタン生成部16がパタン生成し、セレクタ13によって積分器14に出力するものであり、基準周波数断時には、パタン生成の波形を積分器14に代替入力するPLL回路である。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

PLL回路

【課題】ロックアップタイムの高速化とリファレンスリークの低減化をとバランス良く達成する。

【解決手段】電圧制御発振器(104)の制御電圧VCONTをアナログ/デジタル変換して得られるデジタル信号(ADCO)を出力するアナログ/デジタル変換回路(106)と、基準クロック信号(FREF)と帰還クロック信号(FDIV)とがロックしたことを検出した時にロック検出信号(S201)を出力するロック検出部(201)と、ロック検出部からロック検出信号が入力された時にアナログ/デジタル変換回路から入力されたロック時デジタル信号を保持する保持部(107)と、保持部に保持されたロック時デジタル信号とアナログ/デジタル変換回路から出力されたデジタル信号との比較結果に基づいてチャージポンプ電流の電流量を段階的に減少させるチャージポンプ電流量制御信号(CPCONT)を生成するチャージポンプ制御部(108)と、を備えるPLL回路。

(もっと読む)

受信回路及びサンプリングクロック制御方法

【課題】1ユニットインターバルに対するサンプリング数を一定に保つことができる受信回路を提供することを課題とする。

【解決手段】1サイクル内で複数の異なる位相のクロック信号を生成するクロック発生回路(301)と、複数の異なる位相のクロック信号により入力データをオーバーサンプリングするオーバーサンプリング回路(303)と、オーバーサンプリング回路により出力されたデジタルデータの時系列の変化点を検出し、1ユニットインターバルの両端の2個のデータバウンダリを判定するデータバウンダリ判定回路(305)と、判定された2個のデータバウンダリの間の1ユニットインターバルのサンプリング数が閾値より多いときには、隣接する1ユニットインターバルのサンプリング数が一定となるようにクロック発生回路で生成するクロック信号の位相を制御するクロック位相制御回路(306)とを有する受信回路が提供される。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

周波数ジェネレータ

【課題】 DDSを用いて高速スイープを可能にすると共に、周波数設定を容易に行うことができる周波数ジェネレータを提供する。

【解決手段】 スイープ制御部1が、スタート周波数やスイープ周波数ステップ設定値等の周波数設定値を入力して十進数の周波数設定データを出力し、周波数設定データ変換部2が、スイープ制御部1から入力された十進数に、動作周波数、DDS3への入力設定データのビット数、スイープ周波数のステップ設定値に基づく係数をスイープ制御部から入力される十進数の周波数設定データに乗算することで二進数に変換するbitデータ変換部21と、丸め処理を行う丸め処理部22とを備え、DDS3が、入力された二進数の周波数設定データに従って周波数信号を生成して出力する周波数ジェネレータである。

(もっと読む)

原子発振器の光源を制御する方法

【課題】透過光強度が最小となる点に直流バイアス電流を追い込むことが可能な原子発振

器の光源を制御する方法を提供する。

【解決手段】アルカリ金属原子に電磁誘起透過現象を発生させるための共鳴光対を生成す

る半導体レーザー1と、アルカリ金属原子を封入したcell2と、cell2を透過し

た共鳴光対を検出するPD3と、PD3の出力信号をデジタル信号に変換するA/Dコン

バーター4と、A/Dコンバーター4により変換されたデジタル信号を記憶するメモリ6

と、メモリ6へデジタル信号を書き込み、そのデジタル信号を読み出すメモリ制御部5と

、メモリ6に既に記憶されているデジタルデータとA/Dコンバーター4により変換され

たデジタル信号とを比較する比較部7と、比較結果に基づき半導体レーザー1に与える直

流バイアス電流を制御する電流源制御部8と、半導体レーザー1に直流バイアス電流を供

給する電流源9と、を備えて構成されている。

(もっと読む)

原子発振器、及び光源を制御する方法

【課題】透過光強度が最小となる点に直流バイアス電流を追い込むことが可能な原子発振

器を提供する。

【解決手段】アルカリ金属原子に電磁誘起透過現象を発生させるための共鳴光対を生成す

る半導体レーザー1と、アルカリ金属原子を封入したcell2と、cell2を透過し

た共鳴光対を検出するPD3と、PD3の出力信号をデジタル信号に変換するA/Dコン

バーター4と、A/Dコンバーター4により変換されたデジタル信号を記憶するメモリ6

と、メモリ6へデジタル信号を書き込み、メモリ6に記憶されたデジタル信号を読み出す

メモリ制御部5と、メモリ6に既に記憶されているデジタルデータとA/Dコンバーター

4により変換されたデジタル信号とを比較する比較部7と、比較結果に基づき半導体レー

ザー1に与える直流バイアス電流を制御する電流源制御部8と、半導体レーザー1に直流

バイアス電流を供給する電流源9と、を備えて構成されている。

(もっと読む)

発振回路

【課題】 本発明は、出力信号の発振周波数の精度を向上させることができる発振回路を提供することを目的とする。

【解決手段】 圧電素子の周波数温度特性を補償するための補償電圧S150を生成する補償電圧生成部160と、制御電圧S130に補償電圧S150を加算することにより、補正制御電圧S160を生成する加算部150と、補正制御電圧S160に基づいて、発振周波数を変化させることにより、所望の発振周波数を有する出力信号S170を生成し出力する電圧制御発振部220とを備える。

(もっと読む)

1 - 20 / 140

[ Back to top ]