Fターム[5J106DD39]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | レジスタ (165) | シフトレジスタ (48)

Fターム[5J106DD39]に分類される特許

1 - 20 / 48

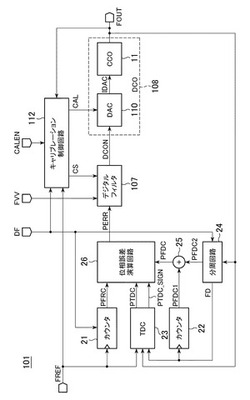

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

内部コマンド生成回路

【課題】電流消耗を減少させることができる内部コマンド生成回路を提供する。

【解決手段】本発明の内部コマンド生成回路は、読出しまたは書込み動作のためのコマンドを受信して、所定の周期で発生する複数のパルスを含む第1バーストパルスを生成するバーストパルス発生部と、前記第1バーストパルスをシフトして内部コマンドを生成するパルスシフト部と、を含み、前記内部コマンドは、バースト終了信号またはバーストコマンドのパルスが入力されるとディセーブルされる。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

クロックデータリカバリ回路および逓倍クロック生成回路

【課題】データ入力の位相変化に対する受信マージンの減少を抑止でき、誤受信の確率の増大を抑止できるクロックデータリカバリ回路および逓倍クロック生成回路を提供する。

【解決手段】入力データと抽出クロックの位相差を検出して位相差に応じたアナログ量を出力する第1の位相検出器110と、ループフィルタ150と、第1の位相検出器の出力に応じてループフィルタから電流を充電または放電するチャージポンプ130,140と、VCO160と、入力データと抽出クロックの位相差の極性を検出する第2の位相検出器120と、第2の位相検出器の検出結果に応じて第1の位相検出器がもつ位相オフセットを相殺する補正位相情報を発生する補正位相情報発生部210と、補正位相をループ200に加算する補正位相加算部220と、を有し、補正位相加算部220は、チャージポンプの充電電流と放電電流を相対的に変化させる。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

DLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法

【課題】本発明は、アップデート条件を緩和させて効率的なアップデートを行い、位相比較感知結果値が不規則に変化しても内部クロックの位相をより正確に制御することができるDLL回路、DLL回路のアップデート制御装置、及びDLL回路のアップデート方法を提供する。

【解決手段】本発明のDLL(Delay Locked Loop)回路は、基準クロックとフィードバッククロックの位相を比較感知して位相感知信号を生成する位相感知手段;前記基準クロックに応答して前記位相感知信号が有する第1論理値と第2論理値の個数の差を判別して有効区間信号とアップデート制御信号を生成するアップデート制御装置;及び前記有効区間信号のイネーブル時に前記アップデート制御信号に応答して遅延ラインに付与する遅延値をアップデートするシフトレジスタ;を備える。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

位相補間制御装置

【課題】位相補間制御装置中のノイズフィルタ帯域幅を動的に調整し、位相補間制御装置を広く応用することができる上、CDRのロック時間を短縮させることができる位相補間制御装置を提供する。

【解決手段】位相補間制御装置400は、第1の信号と第2の信号との位相関係を表す指示を受信し、複数の双方向シフトレジスタを含む。複数の双方向シフトレジスタは、互いに直列接続され、位相補間制御装置が受信した指示が、第1の信号の位相が第2の信号の位相より進んでいることを表すとき、直列接続された複数の双方向シフトレジスタをそのうちの1方向でシフトさせる。位相補間制御装置400が受信した指示が、第1の信号の位相が第2の信号の位相より遅れていることを表すとき、直列接続された複数の双方向シフトレジスタを他の方向でシフトさせる。

(もっと読む)

PLL回路並びに無線通信装置

【課題】発振器毎の変換利得を吸収し、いずれの発振器を用いても発振周波数を安定して収束させることができる、優れたPLL回路を提供する。

【解決手段】ビット・シフト量演算部は、ディジタル制御発振器の変換利得の概算値と、位相比較器の出力の下限値及び上限値に相当するデータ変換部の出力の下限値及び上限値に基づいて、当該PLLを収束させるために必要なビット・シフト量nを決定する。ビット・シフト回路は、ディジタル制御発振器へのディジタル制御データに対し、当該帰還ループを収束させるために必要となるビット・シフト量を与える。

(もっと読む)

1 - 20 / 48

[ Back to top ]