Fターム[5J106FF09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数のループ (130)

Fターム[5J106FF09]に分類される特許

101 - 120 / 130

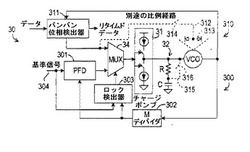

別途の比例経路を有するクロックデータリカバリループ

【課題】安定性の高いバンバンCDRループを提供すること。

【解決手段】本発明によるクロックデータリカバリループ(30)は、非線形(例えば、バンバン)位相検出器(311)、チャージポンプ(31)、RCループフィルタ(32)、および、信号生成器(例えば、電圧制御発振器(VCO)(33))を含む。データ速度が遅いときは、ループ(30)はチャージポンプ(31)と、安定な二次挙動を示すループフィルタ(32)とともに、動作され得る。このとき、ループフィルタ(32)の抵抗器Rは比例経路として機能する。また、別途の比例経路(312)も提供され、VCO(33)の制御入力に位相検出器(311)の出力を直接提供する。その間、ループフィルタ(32)の抵抗器Rもバイパスされる。データ速度の増加が、三次の影響を生じさせるとき、別途の比例経路(312)が二次挙動を維持するように活性化され得る。

(もっと読む)

ジッターなしのクライアントクロックの復元

本発明は、クライアント信号クロックを復元するためのシステム、装置、および方法を提供する。本発明は、入力基準クロックにおける突然の変化を補償するために、PLLシステムのフィードバックにおいて位相シフト要素を提供することによって、クロック信号内のジッターをさらに効果的に除去することができる。PLLシステムは、対応する調整カウント数に依存せず、クライアントクロック信号を抽出するので、さまざまなペイロードタイプに適応することができるように、柔軟なクロック復元を提供する。  (もっと読む)

(もっと読む)

デジタル制御発振器

【課題】

出力周波数の可変範囲の変動を低減し、性能の劣化を抑止できるデジタル制御発振器を提供すること。

【解決手段】

本発明にかかるデジタル制御発振器は、制御電流I1及び制御電流I2を生成するPLL100a,100bと、制御電流I1及び制御電流I2を参照し、入力されるデジタルの制御データDFを、制御電流I1から制御電流I2までを範囲とするアナログの制御電流Idacに変換する変換回路10と、制御電流Idacに応じた周波数のクロックを出力するCCO111と、を有するものである。

(もっと読む)

回路、制御システム、IC、送受信装置、制御方法およびプログラム

【課題】 位相誤差を小さくでき、かつ高周波ジッタ成分および低周波ワンダ成分を同時に抑圧することができる回路、制御システム、IC、送受信装置、制御方法およびプログラムを提供する。

【解決手段】 高周波ジッタ抑圧部であるPLL1部100と、低周波ワンダ抑圧部であるPLL2部200と、再生クロック部であるPLL3部300をマルチループ・シンセサイザ構成とする。

(もっと読む)

システムクロック装置

【課題】冗長構成されたシステムクロック装置100に関し、クロック切替時に発生するクロック間の位相差に起因する位相飛びを無くす。

【解決手段】シンセサイザ44が、周波数設定値Δφ1に基づいて、入力された第1基準クロック701を、周波数の異なる第2基準クロック703を出力し、分周器41が、冗長構成された他方の系から入力された第1クロック704を第2基準クロック702(703)の周波数となるように分周して、第2クロック705を出力し、位相比較器42が、第2基準クロック703と第2クロック705との位相差を検出し、第2クロック705の位相に第2基準クロック703の位相を合わせて該位相差を減ずる方向の周波数設定値Δφをシンセサイザに与え、スイッチ30が、第1基準クロック701が正常なとき、第2基準クロック703を選択し、異常のとき、第2クロック705を選択して出力する。

(もっと読む)

半導体集積回路装置

【課題】 簡単な構成で高逓倍能力を持ち、高速応答を実現したクロック生成回路を備えた半導体集積回路装置を提供する。

【解決手段】 遅延回路の各段遅延信号をゲート手段で選択し初段側に帰還してリングオシレータを構成する。デコーダにより1つのゲート手段の選択信号を形成して上記ゲート手段を制御する。基準周波数信号の1周期間での上記リングオシレータの発振出力のカウンタ出力とX倍指定値との比較結果により第1レジスタで上記デコーダの入力信号を形成する。第1動作モードで上記制御回路の代表比較結果に対応してバイナリスキャンにより上記入力信号を形成する。第2動作モードでは、上記比較結果により上記入力信号に対して+1又は−1とする。

(もっと読む)

低ジッタ2ループフラクショナルN合成器のための方法および装置

第1の位相ロックループ(PLL)回路(301)は、発振器303からのタイミング基準信号を受信するための入力と、発振器出力信号を供給する制御可能発振器回路(805)と、複数係数フィードバック分周器回路(809)とを含む。第2の制御ループ回路は、選択回路853を介して選択可能に結合されて、デジタル制御値(M)を第1のループ回路の複数係数フィードバック分周器回路に供給することにより発振器出力信号を制御する。第2の制御ループが結合されて制御値をフィードバック分周器回路に供給する間、制御値は、発振器出力信号と、分周器回路(335)において第2の制御ループ回路に結合される基準信号との間の検出された差に従って定められる。第2の制御ループ回路が第1のPLL回路を制御するように結合されていない間、第1のPLL回路はデジタル制御値を受信して、フィードバック分周器の分周比率を制御する。デジタル制御値は、不揮発性記憶装置(317)に記憶される記憶制御値に少なくとも部分的に従って定められ、記憶制御値は発振器出力信号の所望の周波数に対応する。  (もっと読む)

(もっと読む)

高周波発生装置

【課題】 本発明は、高周波出力を安定化させる高周波発生装置を提供する。

【解決手段】 高周波発振源1と、この高周波発振源の出力信号に基づく高周波出力電力を検出する高周波出力電力検出部4とを備え、前記高周波出力電力検出部から得られた高周波出力電力検出信号とローカル発振器22より発振されたローカル発振信号に基づいてフィードバック制御をかけるフィードバック制御回路を備えた高周波発生装置であって、前記ローカル発振器は、第二の高周波発振源13と、この高周波発振源の出力信号に基づく高周波出力電力を検出する第二の高周波出力電力検出部15とを備えてあることを特徴とする高周波発生装置。

(もっと読む)

局部発振回路、携帯情報端末および局部発振制御方法

【課題】 TDMA/TDDのスロット可変型通信における周波数の変動を防止する。

【解決手段】 2系統のPLL回路をそれぞれ有する第1の集積回路(40a)および第2の集積回路(40b)と、基準発振回路(30)と、2系統の周波数帯域の信号を出力する出力回路(50,60)とを備える。互いに同一系統となる2つの第1PLL回路(70A,70B)は、該各PLL回路をフレーム期間中の異なるタイムスロットにて動作させるための制御信号が供給される信号線(70AC,70BC)と出力回路とに接続される。第1の集積回路の第2PLL回路(80A)は、該PLL回路を上記タイムスロットの双方にて動作させるための制御信号が供給される信号線(80AC)と出力回路とに接続される。第2の集積回路の第2PLL回路(80B)は、出力回路には接続されず、第1の集積回路のPLL回路が接続された信号線(70AC,80AC)のうちのいずれかと接続される。

(もっと読む)

位相周波数検出回路およびPLL

【課題】 媒体の傷等の影響を受けず、変調マークに左右されずに安定に高速にPLLを引き込むことが可能な位相周波数検出回路およびPLLを提供することにある。

【解決手段】 再生信号に基づいて再生クロック信号を生成する回路において、前記再生クロック信号を生成する電圧制御発振器と、前記再生クロックから前記所定周期の信号を発生する第1の周期発生器と前記第1の周期発生器とは位相が異なり、前記再生クロックから前記所定周期の信号を発生する第2の周期発生器と、前記再生信号と前記第1の周期発生器の出力とを乗算する第1の乗算器と、前記再生信号と前記第2の周期発生器の出力とを乗算する第2の乗算器と、前記第1の乗算器の出力と第2の乗算器の出力に応じて前記電圧制御発振器の制御電圧を制御するPLL。

(もっと読む)

通信用半導体集積回路および携帯通信端末

【課題】 受信の途中でPGAのゲインの切替えを行なってもPLL回路の周波数変動を所定の時間内に収束させることができるとともに、送信時の位相雑音特性および送信スペクトラム特性が所定の条件を満足することができる通信用半導体集積回路(高周波IC)を提供する。

【解決手段】 位相変調および振幅変調された受信信号を受信するモードと位相変調のみされた受信信号を受信するモードとで動作可能な通信用半導体集積回路(高周波IC)において、PLL回路のループフィルタ(634)の周波数帯域を、受信モードでは大きく、送信モードでは小さくなるように切り替え設定するようにした。

(もっと読む)

90゜位相差発生回路および周波数シンセサイザおよび直交変調回路および直交復調回路

【課題】90゜位相差が生成できているかどうかを検証しながら出力し、従来回路で必要であったリミッティングアンプは必要とせず、入力信号の周波数が変わってもある程度の周波数範囲であれば90゜位相差を確保することのできる90゜位相差発生回路を提供する。

【解決手段】請求項1に記載の90゜位相差発生回路では、

入力信号から90゜位相差を持った第1および第2の出力信号を発生させる90゜位相差発生回路において、位相調整感度に比例して入力信号の位相を遅らせる可変移相器と、

前記第1と第2の出力信号について90゜位相差からのずれを位相差検出感度に比例した誤差電圧信号として出力する位相比較器と、この位相比較器の出力を積分して前記可変移相器の移相量を調整する帰還回路を備える。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】

半導体集積回路は、位相周波数比較回路とループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する電圧を電流に変換し、変換後の電流をこれら複数のCDR回路に分配する。

(もっと読む)

クロックおよびデータリカバリ位相ロックループならびに高速位相検出器アーキテクチャ

入力データ速度の2分の1(すなわちハーフレートのクロック)に等しいクロック速度で動作するクロックリカバリ回路および高速位相検出器回路が提示される。クロックリカバリ回路は二重入力ラッチを用いて、ハーフレートのクロック信号の立ち上がりエッジおよび立下りエッジの双方で入力シリアルデータをサンプリングして、等価の最高データ速度のクロックリカバリを与える。クロックリカバリ回路は、入力シリアルデータビットの中心におけるハーフレートのクロック遷移を維持するように機能する。クロックリカバリ回路は、位相検出器、チャージポンプ、制御された発振モジュールおよびフィードバックモジュールを含む。位相検出器は、チャージポンプへの入力データ信号における位相およびデータの遷移に関する情報を生成する。一般的に、回路は遅延の影響を受けず、互いに対してずらされた位相および遷移情報を受信する。高速位相検出器回路は、入力シリアルデータからの位相情報および遷移情報を与える。高速位相検出器回路は、ハーフレートのクロックの立ち上がりエッジおよび立下りエッジの双方での入力シリアルデータをサンプリングして、等価の最高データ速度サンプリングを与える。高速位相検出器回路は、位相情報および遷移情報の間で遅延を生じる。位相情報は第1のビット周期で生成され、遷移情報は第1のビット周期に対する第2のビット周期で生成される。  (もっと読む)

(もっと読む)

通信装置

【課題】複数回の周波数変換を行う通信装置において、周波数変換に用いる局部発振器の数を削減する。

【解決手段】送信系において、第1の周波数シンセサイザ51では、基準信号と帰還ループにより帰還された第1の出力信号(F4)との位相差に応じて該基準信号と同期した該第1の出力信号(F4)を出力し、第2の周波数シンセサイザ52では、該第1の出力信号(F4)と帰還ループにより帰還された第2の出力信号(F5)との位相差に応じて該第1の出力信号(F4)と同期した該第2の出力信号(F5)を出力する。そして、第1の周波数変換器1では、入力される第1の周波数信号(F1)を該第1の出力信号(F4)の周波数に従って第2の周波数信号(F2)に変換し、第2の周波数変換器2では、該第2の周波数信号(F2)を該第2の出力信号(F5)の周波数に従って第3の周波数信号(F3)に変換して送信する。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】 位相同期の高速な収束動作を維持しつつ、低雑音となる位相同期ループ形周波数シンセサイザを得る。

【解決手段】 加算器7は、第1の電圧制御発振器4への制御信号として、局部発振源20の設定信号を用いる。局部発振源20は、第2の基準信号を生成する第2の基準発振源11と、局部発振信号を生成する第2の電圧制御発振器14と、局部発振信号を周波数分周し第2の同期信号を出力する第2の可変分周器15と、第2の基準信号と第2の同期信号を入力とし、第2の位相比較信号を出力する第2の位相比較器12と、第2の位相比較信号を平滑して第2の電圧制御発振器14と加算器7に出力する第2のループフィルタ13とで構成される。

(もっと読む)

ディジタルPLL回路

周波数比較器は、基準クロックおよび出力クロックの周波数を比較し、周波数比較信号を出力する。周波数可変回路は、直列接続された複数の反転回路を有する遅延回路と第1選択回路とから構成される。第1選択回路は、奇数番目の反転回路から出力される奇数出力信号のいずれかを周波数比較信号に応じて選択し、帰還信号として遅延回路の入力に帰還させる。位相比較器は、基準クロックおよび出力クロックの位相を比較し、位相比較信号を出力する。第2選択回路は、奇数出力信号のいずれかを位相比較信号に応じて選択し、出力クロックとして出力する。周波数可変回路は、帰還ループを構成する反転回路の接続段数を調整することで、出力クロックの周波数を変更する可変発振器として機能する。遅延回路は、出力クロックの周波数調整および位相調整の両方に共通して用いられる。このため、回路規模を低減できる。  (もっと読む)

(もっと読む)

スプレッドスペクトルクロック生成器及びスプレッドスペクトルクロック信号を生成する方法

【課題】スプレッドスペクトルクロック生成器(SSCG)及びスプレッドスペクトルクロック(SSC)信号を生成する方法を提供する。

【解決手段】第1フィードバック信号の平均周波数と受信された比較周波数信号との差に基づくか、第2フィードバック信号と比較周波数信号との総位相変化量に基づいて所定の変調電圧信号を出力する制御部、受信された既存周波数信号及び受信された第2フィードバック信号の機能で第1制御電圧を生成するサブシステムを備えるSSCGである。合算部は、第1制御電圧信号と変調電圧信号とを合算して第2制御電圧信号を生成し、電圧制御オシレータは、第2制御電圧信号に基づいてSSC信号を生成する。

(もっと読む)

ACシュタルクシフトが低減された光ポンプ周波数標準器

【課題】低コストで実現可能な光ポンプ周波数標準器を提供する。

【解決手段】安定化された周波数信号を生成するための装置(20)を開示する。装置(20)は、第1、第2、及び第3のエネルギー状態を有する量子吸収器(13)を備える。量子吸収器(13)は、周波数νLの電磁放射を生成する第1の放射源(21)によって照射される。この電磁放射は第1と第3のエネルギー状態間の遷移を誘起する。量子吸収器(13)は、周波数νMの電磁放射を生成する第2の放射源(18)によっても照射される。この電磁放射は、第1と第2のエネルギー状態間の遷移を誘起する。量子吸収器(13)から出る、νLを含む周波数範囲内の放射レベルを示す検出器信号を生成する検出器が複数のサーボループによって使用される。サーボループの1つが、検出器信号を最小化または最大化するνLの値を決定し、他の1つのサーボループ(31)が、第1の放射源(21)の強度に対するνMの依存度を低減するオフセット信号を決定する。

(もっと読む)

タイミング抽出回路

【課題】 メインVCOにおいてデータとの位相同期を瞬時に行なうことができるタイミング抽出回路を提供する。

【解決手段】 バーストデータからタイミングを抽出する回路において、データとの同期をとるメインVCO1の発振周波数とメインVCO1への制御信号を生成するサブVCO2の発振周波数とを周波数比較器4を用いて比較し、周波数差に応じた制御信号12を用いて両発振周波数を自動的に一致させるフィードバックループを設けることで、バーストデータに対して瞬時に応答することを可能とする。

(もっと読む)

101 - 120 / 130

[ Back to top ]