Fターム[5J106FF09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数のループ (130)

Fターム[5J106FF09]に分類される特許

41 - 60 / 130

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

基準信号生成装置及びこれを用いた機器

【課題】広く普及しているADSL方式等を採用した通信回線を利用して、利用者側において、通信品質の低下や発着信の制約等を生じることなく、高精度な基準信号を容易且つ安価に得ることが可能な基準信号生成装置及びこれを用いた機器を提供する。

【解決手段】局側の通信装置と、利用者側の端末装置との間で、通信回線を介して通信を行う通信システムを用いて基準信号を生成する基準信号生成装置において、前記局側の通信装置から前記通信回線を介して伝送される一定の周波数を有する基準信号が含まれる信号を入力し、前記入力信号から基準信号を抽出する基準信号抽出回路を備えるように構成した。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

DLL回路及びその制御方法

【課題】冗長な回路、配線を不要とし、回路規模の増大を回避し、デューティを変更可能とするDLLを提供する。

【解決手段】外部信号の第1遷移(Rise)を可変に遅延させる第1可変遅延回路(10R)と、外部信号の第2遷移(Fall)を可変に遅延する第2可変遅延回路(10F)と、第1可変遅延回路(10R)の出力信号と第2可変遅延回路(10F)の出力信号とを合成する合成回路(13)と、合成回路(13)の出力信号のデューティの変更と検出を行うデューティ変更検出回路(21)と、デューティ変更検出回路(21)のデューティ検出結果(DCC)に従って第1可変遅延回路(10R)又は第2可変遅延回路(10F)の遅延を可変させる遅延制御回路(15R、15F)と、を備える。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステム

【課題】 グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステムを提供する。

【解決手段】 一実施形態のシステムは、個々のチャネルに関連する誤差信号をそれぞれ受け取る複数の入力を備えたグローバルPLL回路と、前記グローバルPLL回路と結合された遅延補償回路と、を含む。一実施形態の方法は、個々のチャネルにそれぞれ関連する複数の誤差信号を受け取るステップと、前記誤差信号に1つ又は複数の遅延補償信号を適用するステップと、前記チャネルのそれぞれに関する位相誤差出力信号を出力するステップと、を含む。

(もっと読む)

PLL制御装置及びPLL制御方法

【課題】親機、複数台の中継機、複数台の子機を備えた大規模なシステムで符号長が比較的長い同期信号を用いても、安定したPLLの引き込みを実現可能とする。

【解決手段】このPLL制御装置では、TIM抽出回路101は入力信号からタイミング成分を抽出し、VCXOは供給される制御信号に基づき基準信号の位相及び/又は発振周波数を制御する。0次PLL回路102はタイミング成分の位相差に基づき基準信号の発振周波数範囲を設定するための制御信号を出力し、1次PLL回路103はタイミング成分の位相差に基づき基準信号の位相を制御するための制御信号を出力する。制御セレクタ105は、0次PLL回路102又は1次PLL回路103からの制御信号を順次切り替えてVCXOに供給する。

(もっと読む)

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

原子発振器およびその制御方法

【課題】光情報の検出精度の劣化を抑えながら、ガスセルの温度制御を量子レベルで制御する原子発振器およびその制御方法を提供する。

【解決手段】本実施形態の原子発振器の光学系の要部である物理部50は、ガス状の金属原子を封入したガスセル10およびそれを保持するガスセル保持部材21からなるセルユニット20、ガスセル10を所定の温度に加熱するヒータ15、ガスセル10中の金属原子を励起するコヒーレント光の光源である光源30、ガスセル10を透過した励起光を検出するフォトセンサ40、フォトセンサ40により検出された励起光の強度に基づいてヒータ15を制御する温度制御手段、を有する。ガスセル10は、円筒部11と、該円筒部11の両端の開口部をそれぞれ封鎖して励起光の光路の入射面および出射面を形成する窓部12と、を有し、ヒータ15が、窓部12の前記光路と異なる領域に設けられている。

(もっと読む)

クロック再生回路

【課題】短いビット同期時間、クロックワンダー追随性能、高い高周波ジッタ耐性、を同時に満たすクロック再生回路を提供する。

【解決手段】入力データ信号101と再生クロック102との位相差を検出する位相差検出回路103、位相差検出回路103の出力を平均化する平均化回路104、位相差検出回路103の出力をサンプル/ホールドするリセット付サンプル/ホールド回路105、平均化回路104の出力の積分値とリセット付サンプル/ホールド回路105の出力値との和に相当する位相の再生クロック102を生成する再生クロック生成回路106を備える。リセット付サンプル/ホールド回路105は、バースト伝送開始信号110を受けて位相差検出回路103の出力をサンプル/ホールドし、バースト伝送終了信号111を受けてホールドしている値を初期値にリセットする。

(もっと読む)

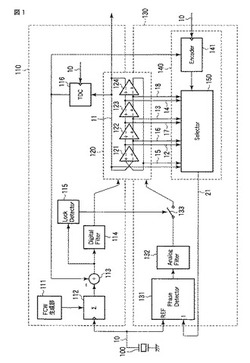

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティー比特性を有するクロックを生成し、半導体集積回路の動作をより安定的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL回路は、基準クロックを所定の分周比で分周して分周クロックを生成するクロック分周手段;前記分周クロックに対する遅延固定動作を行って遅延クロックを生成するフィードバックループ;前記遅延クロックを前記基準クロックの半周期だけ遅延させて半周期遅延クロックを生成する半周期遅延手段;および前記遅延クロックと前記半周期遅延クロックを組み合わせ演算して出力クロックを生成する演算手段;を含むことを特徴とする。

(もっと読む)

通信装置、発振器、並びに周波数シンセサイザ

【課題】CDMAやOFDMといった大きな包絡線変動を伴う変調方式を使用することができ、送信機に線形性と高効率を両立するLINC送信機を提供する。

【解決手段】変調データの周波数変換を行なうPLLにおいて2ポイント変調方式を採用することで、発振器に入力される変調データはPLLにとって外乱とは見えなくなり、PLLのループ帯域幅に制限されない広帯域変調を実現することが可能となる。また、発振器の積分効果により、サンプリング周波数付近におけるレプリカを、アナログ・スムージング・フィルタを追加することなく大幅に抑制することができ、回路のリコンフィギャラビリティを高めることができる。

(もっと読む)

待ち時間不確実性を減少したトランシーバシステム

【課題】待ち時間不確実性を減少したトランシーバシステムを提供すること。

【解決手段】トランシーバシステムは、ワードアライナを備え、0のワードアライナ待ち時間不確実性を有し、ワードアライナに結合されるビットスリッパをさらに備えている。該トランシーバーシステムは、ワードアライナによるワード整列およびビットスリッパによるビットスリップに起因する全遅延が回復クロックのすべての位相に対して一定であるように、ビットスリッパがビットをスリップさせる、トランシーバシステムである。

(もっと読む)

遅延固定ループ

【課題】ノイズの干渉、PVTの変動、及び頻繁に起こるパワーダウンモードへの進入・脱出など、半導体メモリ素子の最悪の状況でも安定的に動作できる遅延固定ループを提供すること。

【解決手段】遅延固定をなすために、ソースクロックの第1のクロックエッジ及び第2のクロックエッジに対応する第1の遅延クロック及び第2の遅延クロックを生成する遅延固定部と、前記第1の遅延クロックと第2の遅延クロックとの位相差を検出して加重値選択信号を出力する位相検出部と、前記第1の遅延クロックと第2の遅延クロックとの遅延固定時点から予定された期間に獲得した前記加重値選択信号を格納する加重値格納部と、該加重値格納部に格納された加重値選択信号に対応する加重値を反映し、前記第1の遅延クロックの位相と第2の遅延クロックの位相とを混合して遅延固定ループクロックとして出力する位相混合部とを備えることを特徴とする。

(もっと読む)

クロック発生回路

【課題】高精度な周波数変調が可能なスペクトラム拡散クロック発生回路を提供する。

【解決手段】このスペクトラム拡散クロック発生回路において、PLL回路31は、それぞれ位相の異なるクロック信号CLKV1〜CLKV5を出力する。セレクタ23は、クロック信号CLKV1〜CLKV5のうちのいずれか1つを選択し、制御回路24はセレクタ9の信号選択動作を制御する。入力分周回路1は選択クロック信号を分周して基準クロック信号CLKRを出力する。PLL回路21は、基準クロック信号CLKRを周波数逓倍した発振クロック信号CLKOを生成する。これにより、発振クロック信号CLKOの位相を微調整することができる。したがって、高精度な周波数変調が可能なスペクトラム拡散クロック発生回路が実現できる。

(もっと読む)

拡張されたトラッキング範囲を有する位相ロック・ループ(PLL)

PLLのトラッキング範囲を拡張するための方法は、それに関連する第1の幅を有する、PLLの初期トラッキング・ウィンドウを確立するステップと、PLLに供給された入力信号の周波数がトラッキング・ウィンドウ外にあるとき、第1の幅よりも大きい、それに関連する第2の幅を有する拡張されたトラッキング範囲内にPLLのトラッキング・ウィンドウを動的に調整するステップとを含む。  (もっと読む)

(もっと読む)

集積回路装置

【課題】VCOを備える周波数シンセサイザに関し、VCOのf−V特性のばらつきに対処する手法を提案する。

【解決手段】制御電圧V1に応じて発振周波数f1が変化する第1の電圧制御発振器を備え、基準周波数に応じた周波数の信号を発振する第1の周波数シンセサイザと、制御電圧V2に応じて発振周波数f2が変化する第2の電圧制御発振器を備え、前記第1の周波数シンセサイザと同じチップ上に設けられており、前記基準周波数に応じた周波数の信号を発振する第2の周波数シンセサイザと、前記第1の電圧制御発振器の制御電圧V1をモニタし、前記第1の周波数シンセサイザの周波数がロックしているときにモニタされた前記制御電圧V1と基準電圧とを比較し、前記制御電圧V1と前記基準電圧との比較結果に基づいて、前記第2の電圧制御発振器のf2−V2(発振周波数−制御電圧)特性を変化させるコンパレータとを備えることを特徴とする集積回路装置。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を安定させる。

【解決手段】位相検出器210は、位相補間器270からの同期クロックとシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。第1の積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。第2の積分器240は、位相補正制御信号をさらに積分してアップ/ダウン信号を得る。パターン発生器250は、アップ/ダウン信号からシリアルデータの周波数変動に追従するための周波数補正制御信号を生成する。パターン発生器250のパターン長と第2の積分器240のカウント幅の積は、第1の積分器230のカウント幅が大きいほど大きくなる大きさの閾値以上である。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】クロックアンドデータリカバリ回路において、周波数追従ループのジッタ耐性を向上させる。

【解決手段】位相検出器210は、同期クロック信号とシリアルデータの位相を比較して比較結果に応じた位相誤差信号を出力する。積分器230は、位相誤差信号を積分してシリアルデータの位相変動に追従するための位相補正制御信号を得る。積分器240は、所定の長さの平滑期間毎に位相誤差信号を積分して平滑誤差信号を得る。パターン発生器250は、所定の長さのパターン発生期間毎に、平滑誤差信号に応じた頻度で同期クロック信号の位相を変更するパターンを発生して周波数補正制御信号として出力する。積分器240は、周波数補正制御信号がフィードバックされ、該周波数補正制御信号における頻度の変動方向に応じて、平滑化期間の長さを変更する。

(もっと読む)

41 - 60 / 130

[ Back to top ]