Fターム[5J106FF09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数のループ (130)

Fターム[5J106FF09]に分類される特許

21 - 40 / 130

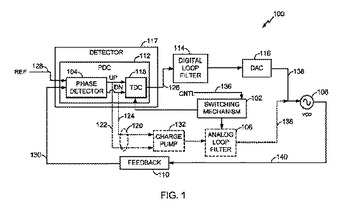

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

PLL回路

【課題】ループ内の無駄時間を補償し、所望の特性を取得可能なPLL回路を提供する。

【解決手段】メインパス110は、入力段に配置され、入力信号と実信号との位相検出を行うフェーズディテクタ111と、フェーズディテクタの出力側に配置され、ループの応答特性を決めるためのループフィルタ113と、ループフィルタの出力信号に応じた周波数で発振し、発振信号を実信号としてメイン帰還パスに出力する制御発振器114と、を含み、ローカル帰還パス130は、ループフィルタの出力が入力され、制御発振器のレプリカとして機能するレプリカ部131と、レプリカ部の出力を一巡無駄時間分遅延させる遅延部132と、遅延部の入力信号と出力信号の差分を得る第1の減算器133と、第1の減算部の出力信号からループフィルタ中の内部信号を定数倍した信号を減算し、ループフィルタの入力側に出力する第2の減算器136と、を含む。

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御に対して、多重PLL回路を適用可能な回路構成を得る。

【解決手段】発振信号を出力する発振器12及び該発振信号と入力信号との位相差に対応する信号を出力する第1位相比較回路14を有する第1PLL11と、入力に応じて回転制御され且つ回転子の回転位置を信号出力するモータ部22及び該モータ部22からの出力信号と入力信号との位相差に対応する信号を出力する第2位相比較回路24を有する第2PLL21と、上記第1PLL11及び第2PLL21が上記入力信号の入力側に対して互いに並列に接続されるように、互いの位相比較回路14,24の出力同士を加算する加算器26と、を備える。上記第1PLL11の発振器12の入力側及び上記第2PLL21のモータ部22の入力側には、それぞれ、ループフィルタ15,25を設ける。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

PLL回路

【課題】特性が悪化する可能性があった。

【解決手段】本発明は、第1および第2のループフィルタを有するPLL回路であって、前記第1のループフィルタに出力される第1の電流信号を生成する第1の出力ドライバと、前記第2のループフィルタに出力される第2の電流信号を生成する第2の出力ドライバとを備える電流信号生成回路と、前記第1もしくは第2の出力ドライバのいずれを活性化するか選択する制御回路と、を有するPLL回路である。

(もっと読む)

放射線硬化チャージポンプ・トポロジ

【課題】シングル・イベント・アップセット(SEUs)により影響されにくいチャージポンプ回路を提供する。

【解決手段】第1のチャージポンプ出力を備えた第1のチャージポンプ30と、第2のチャージポンプ出力を備えた第2のチャージポンプ32と、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するように受け取り、第1の一致信号を出力するように生成する第1の一致検出器34と、第1の一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2:1マルチプレクサ36とを有する。

(もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

遅延ロックドループ回路

【課題】原理的に定常ジッタがなく、基準クロック信号のデューティ比にかかわらず高精度な遅延クロック信号を生成可能な遅延ロックドループ回路を実現する。

【解決手段】遅延素子(10)は、基準クロック信号の立ち上がり(又は立ち下がり)から、ループフィルタ(40)の出力に基づいた量だけ遅延して変化する遅延クロック信号を生成する。信号生成回路(20)は、基準クロック信号の立ち上がり及び立ち下がり並びに遅延クロック信号の変化に応じて相補的に変化する二つの信号を生成する。チャージポンプ回路(30)は、ループフィルタ(40)に対して、これら二つの信号に従って、基準クロック信号の立ち上がり(又は立ち下がり)から遅延クロック信号の変化までの間プッシュ動作(又はプル動作)を、遅延クロック信号の変化から基準クロック信号の立ち下がり(又は立ち上がり)までの間プル動作(又はプッシュ動作)を行う。

(もっと読む)

PLL回路及び発振装置

【課題】クロック信号を安定的に生成するPLL回路及び発振装置を提供すること。

【解決手段】水晶発振回路1は、同水晶発振回路1に設けた駆動可変部の駆動能力をPLL回路50aのループフィルタ59から出力される制御信号Slfの電圧値に応じて制御する。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】フラクショナルスプリアスの発生しない位相同期回路を提供する。

【解決手段】第1の分数及び第2の分数の和で表される比率を基準信号の周波数に乗じて得られる対象信号に周波数及び位相が一致した出力信号を得る位相同期回路において、第1の分数の分母と第2の分数の分母と2との最小公倍数を更に2で除した数と同じ段数の増幅器を環状接続して構成され、最小公倍数と同じ信号数の多相信号が取り出し可能であって多相信号の周波数がデジタル制御信号及びアナログ制御信号によって制御され、多相信号の1つが出力信号として出力される制御発振器120と、出力信号と基準信号との間の周波数差及び位相差をデジタル信号に変換する変換部116と、デジタル信号に基づいて、基準信号の周期毎に、次の周期において基準信号と位相が一致する信号を多相信号から順次選択する信号選択部140とを具備する。

(もっと読む)

21 - 40 / 130

[ Back to top ]