Fターム[5J106FF09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 入出力、ループ構成 (832) | 複数のループ (130)

Fターム[5J106FF09]に分類される特許

61 - 80 / 130

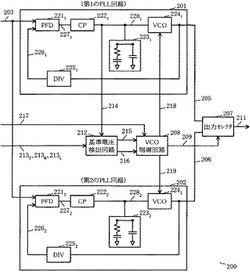

クロック発生装置

【課題】PLL回路を使用し、より幅広い環境変動に適応して周波数を一定値にロックすることのできるクロック発生装置を得る。

【解決手段】クロック発生装置200は、基本的に同一構成で共にLC型VCOを備えた第1および第2のPLL回路201、202を備えている。マスタ側の第1のPLL回路201の第1のVCO2241に加わる第1の制御電圧2281は基準電圧検出回路212で3つの固定値と比較され、その結果に応じて第2のPLL回路202の容量スイッチ247、257の値を調整しておいて、出力セレクタ207で第1のPLL回路201から第2のPLL回路202にクロックの選択を切り替える。

(もっと読む)

クロック供給装置

【課題】上位からのクロックに位相同期したクロックを供給するクロック供給装置に関し、現用系と予備系とのクロックの位相を一致させる。

【解決手段】システムクロックに位相同期した現用系クロックを出力する現用系システムクロック供給装置1aと予備系クロックを出力する予備系システムクロック供給装置1bとを有し、システムクロックに位相同期したクロックを出力するDPLL部2a,2bと、このDPLL部2a,2bからのクロックを遅延制御する可変遅延回路4a,4bと、この可変遅延回路4a,4bを介して出力する現用系クロックと予備系クロックとの位相を比較する位相比較部7a,7bと、この位相比較部7a,7bによる現用系クロックと予備系クロックとの位相比較結果により、可変遅延回路4a,4bの遅延量を制御する位相比較判定部5a,5bとをそれぞれ備えている。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

PLL制御システム

【課題】VCOのバンド毎にチャージポンプ電流を設定しても、ループ帯域のばらつきを抑圧することができるPLL制御システムを提供する。

【解決手段】PLL制御システムにおいて、TCXO8と、分周器B8と、複数のバンドを有するVCO4と、分周器A5と、分周器A5と分周器B8の2つの分周信号を比較する位相比較器6と、VCO4への電圧を出力するループフィルタ2と、位相比較器6の比較信号に応じてループフィルタ2へ電流を供給するチャージポンプ回路3と、ループフィルタ2に対してプリチャージするプリチャージ回路1と、制御部9とを備え、制御部9は、プリチャージ回路1によるプリチャージを、複数のバンドに対応して予め設定された離散的な情報に基づいて離散的に制御する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

PLL回路とPLL回路の電圧制御発振器に供給する制御電圧の制御方法およびプログラム

【課題】 同一のRF周波数で複数の送信所から同一時間、同一内容の電波を送出するSFN(SINGLE FREQUENCY NETWORK)が構築される地上デジタル放送方式においては、受信が重なり合うエリアでは送信信号のFFTクロック精度や送信タイミングにずれが発生すると受信不能(SFNの破綻)が発生する。

【解決手段】 外部同期クロックのエラーを検出した時、正常時トレースし記録しておいた制御電圧を元に、制御電圧の外部同期クロックに対する変化の傾向を計算により推測し、推測し計算した制御電圧を電圧制御発振器に供給する制御電圧とする。

(もっと読む)

PLL回路

【課題】帰還ループに遅延回路を挿入することなく、出力信号でのジッタの発生を抑制し得るPLL回路を提供する。

【解決手段】基準信号ref−CLKと帰還信号の位相を比較する位相比較器2と、チャージポンプ4と、ループフィルター5と、電圧電流変換器6と、電流制御発振器7aと、電流制御発振器の出力信号を分周して帰還信号を生成する分周器3とを備えた帰還ループにより、出力信号out−CLKの周波数を基準信号で設定される周波数に収束させるPLL回路であって、電流制御発振器7aから負荷回路8に出力される出力信号out−DLと位相比較器2に入力される基準信号の位相をずらす遅延回路11aを帰還ループ外に備えた。

(もっと読む)

PLL回路、位相制御方法、および、ICチップ

【課題】クロック周波数を上げることなく、受信精度を向上させる。

【解決手段】分周器131は、クロック信号f_clkを8分周することにより、PSK変調されたデジタル信号DATAとほぼ同じ周波数の互いにπ/2だけ位相が異なる信号sin(wt)、信号cos(wt)を生成する。ACT136は、信号sin(wt)および信号cos(wt)を仮想的に制御角Φだけ移相させた信号と信号DATAとの位相を比較した結果を示す信号ΣV11および信号ΣV12に基づいて、信号DATAと仮想の信号sin(wt+Φ)の位相を同期させるように、cosΦに対応するパラメータcos_paraおよびsinΦに対応するパラメータsin_paraの値を制御する。また、ACT136は、信号ΣV11およびΣV12に基づいて、CPUが信号DATAからデータを読み出すタイミングを制御する。本発明は、非接触ICチップに適用できる。

(もっと読む)

クロック位相シフト装置

【課題】PLL回路を使用してクロックの位相をずらすクロック位相シフト装置において、PLLロック外れを発生しにくくする。

【解決手段】水晶発振器100の出力クロックC100を入力する第1段のPLL回路201、およびこの第1段のPLL回路の出力クロックC201を入力する第2段のPLL回路202を備え、前記第2段のPLL回路の出力クロックC202が前記第1段のPLL回路に前記水晶発振器の出力クロックと比較する入力クロックとして入力され、前記第2段のPLL回路の出力クロックC202が外部への出力クロックとして取り出されるクロック位相シフト装置。

(もっと読む)

位相同期発振器及びその制御方法

【課題】VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られることを課題とする。

【解決手段】位相比較器と、ローパスフィルタと、主制御を行う制御部と、該制御部出力の制御電圧で駆動されるVCO回路と、その出力を分周する可変分周器とからなるPLLループを備える位相同期発振器であって、制御部は、PLLループを複数周波数でロックさせて各ロック時の制御電圧を測定し、該測定した各制御電圧に基づき、VCO回路のリニアリティー校正された変調感度を求めると共に、該PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための制御電圧信号を生成する。

(もっと読む)

位相同期回路および電子機器

【課題】位相同期回路において、発振回路の周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止する。

【解決手段】ゲイン特性情報取得部107Aは、判定基準周波数f1,f2を使って、初期電流Iini と各周波数で発振させるための周波数制御電流Iosciとを合成して電流制御発振部101Aに供給しながら、実動時の電流制御発振部101Aの周波数変換ゲインKcco を規定する判定基準周波数f1,f2の各発振制御信号Iosci_1,Iosci_2の差の情報(Iout_2 )を測定し、そのデータを周波数比較結果保持部172_2に記憶しておく。位相同期動作時には、周波数比較結果保持部172_2に記憶しておいた周波数比較結果fcompのデータD(f2)に基づく制御電流Icpcnt を補正信号として使って、周波数変換ゲインKcco のばらつきが相殺されるように駆動部104Zを制御する。

(もっと読む)

位相調整回路及びフェイズロックドループ回路

【課題】周波数の高いクロックを用いる事無く、小さな回路規模で実現でき、より細かい分解能で位相調整することができる位相調整回路及びフェイズロックドループ回路を提供する。

【解決手段】入力される水平同期信号SYNC_INは、位相シフト回路21により位相調整データCKPHASEの上位2Bitsの値に応じてシフトされ、その出力によりアップダウンカウンタ22はクロックNCKPをアップ及びダウンカウントして、逓倍回路32等経てラッチ回路23に出力し、ラッチ回路23は、データイネーブル用パルスENCKPによりラッチして、位相調整出力HD_SIGを出力する。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】DLL回路を備えた半導体記憶装置のチップを複数備えた半導体装置の消費電力の低減。

【解決手段】DLL(Delay Lock Loop)を備えた半導体記憶装置の積層モジュールまたは半導体記憶装置を複数有するマルチチップモジュール(MCM)において、DLLで遅延調整されたクロック信号(CLK)を、一の半導体記憶装置と他の半導体記憶装置間で共用するための専用パッド(PAD)を有し、一の半導体記憶装置のDLLを動作させ、他の半導体記憶装置ではDLLを動作させず、一の半導体記憶装置の前記専用パッドから、DLLで遅延調整されたクロック信号(CLK)から作られる、差動の外部クロック信号(CLK、CLKB)に同期した、フライングロッククロック信号を出力し、他の半導体記憶装置は、フライングロッククロック信号を、専用パッドから入力する。

(もっと読む)

ディレイ調整回路およびその制御方法

【課題】同一チップ上の半導体素子のばらつきによる遅延特性のばらつきを補正するディレイ調整回路を提供すること。

【解決手段】ディレイ調整回路は、9段のディレイ素子が直列接続されるディレイ部と、ディレイ部の7段目の信号の立ち上がりエッジである第1エッジが第1基準信号の立ち上がりエッジである第1基準信号エッジよりも進んでいるか否かを検知する第1カウンタ10と、ディレイ部の9段目の信号の立ち上がりエッジである第2エッジが第1基準信号エッジよりも遅れているか否かを検知する第2カウンタ11と、第1カウンタ10において第1エッジが第1基準信号エッジよりも進んでおり、かつ、第2カウンタ11において第2エッジが第1基準信号エッジよりも遅れるように、基準信号Vbを補正して、ディレイ部のディレイ素子の遅延時間を調整する出力電流Ib1を出力するディレイ素子調整部と、を備えている。

(もっと読む)

二重システム型基準周波数信号発生器

【課題】簡素な構造でありながら、切り替え時に基準周波数信号の位相ズレを殆ど生じない二重システム型基準周波数信号発生器を提供する。

【解決手段】現用機モードの基準信号発生部1Aは、GPS衛星1PPS信号S1PAに基づいて位相制御し、基準周波数信号SfAと基準1PPS信号S1PAを生成する。出力選択部2は、現用機モードの基準信号発生部1Aの基準周波数信号SfAと基準1PPS信号S1PAを後段のシステム機器100に出力する。予備機モードの基準信号発生部1Bは、現用機モードの基準信号発生部1Aの基準1PPS信号S1PAに基づいて位相制御し、基準周波数信号SfBと基準1PPS信号S1PBを生成する。このように、予備機モードの基準信号発生部1Bが現用機モード基準信号発生部1Aの出力に対して位相同期することで位相ズレが抑圧され、切り替わり時の位相不連続が抑制される。

(もっと読む)

CDR回路

【課題】入力データに含まれているジッタを削除した再生データを得る。

【解決手段】入力データのデータレート周波数と同じ周波数の参照クロックを入力データにより位相合わせして再生クロックを作成し、該再生クロックにより前記入力データをFIFO101に書き込む。該FIFO101からの読み出しには、前記再生クロックと同期関係にない前記参照クロック又は別のクロックを使用し、前記FIFO101から再生データを出力させる。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

位相ロック・ループにおいて単一イベントによる影響を軽減する方法

【課題】PLL回路において、位相差信号に対する放射イベントの影響を軽減する。

【解決手段】位相−周波数検出器12からの位相差信号は、チャージ・ポンプ24及び30、抵抗性の比例ループ・フィルタ26及び容量性の積分ループ・フィルタ32、バイアス発生器28及び34を介して、加算器40で加算され、VCO14,分周器16を介して検出器12にフィードバックされる。フィルタ26は、影響のスケーリング及びクリップを行って影響を位相差信号から排除し、フィルタ32は、容量性特性により影響を減衰させる。位相差信号が別個のフィルタ特性で処理されて結合されているので、突発的な影響によりPLL回路がロック状態から外れる可能性が低下する。

(もっと読む)

クロック供給装置

【課題】クロック供給ユニットを複数備え、これらクロック供給ユニットのいずれかを運用系ユニットとし、その他のユニットを待機系ユニットとする冗長構成を有するクロック供給装置において、運用系ユニットを切り替える際に生じる供給クロック信号の位相変動を低減することを目的とする。

【解決手段】自ユニット20が待機系ユニットであるとき、運用系ユニット10から入力される運用系ユニットのDPLL12からのクロック信号を基準として、自ユニット20のDPLL22の出力クロック信号を、運用系ユニット10のDPLL12の出力クロック信号に、所定の位相差を持って同期させるユニット間同期部21、37、39を、クロック供給ユニット10、20に備えて構成する。

(もっと読む)

61 - 80 / 130

[ Back to top ]