Fターム[5J106GG13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 計数(カウンタ)回路 (31)

Fターム[5J106GG13]に分類される特許

1 - 20 / 31

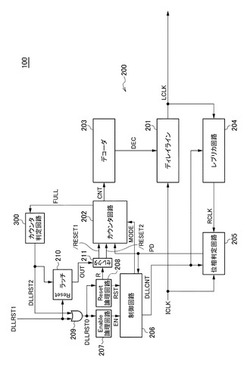

半導体装置

【課題】DLL回路がロックしないという現象の発生を防止する。

【解決手段】カウンタ回路202と、カウンタ回路202のカウント値CNTに応じた遅延量を内部クロック信号LCLKに与えるディレイライン201とを有する。まず、カウンタ回路202は第1のカウント値にセットされ、判定信号PDに基づいてそのカウント値CNTが周期的に更新される。その結果、内部クロック信号LCLKの位相が所望の位相に到達しなかった場合、カウンタ回路202は、第1のカウント値とは異なる第2のカウント値にセットされ、DLL回路200がリスタートされる。これにより、DLL回路がロックしなかった場合であっても自動的にリスタートされることから、DLL回路がロックしないという現象が防止される。

(もっと読む)

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

半導体装置

【課題】レプリカ回路の精度を抜本的に向上する。

【解決手段】半導体装置10は、少なくともフィードバッククロック信号RCLK1に基づいて外部クロック信号CK,/CKを遅延させてなる内部クロック信号RLCLKを出力するDLL回路70と、内部クロック信号RLCLKに同期してデータを出力する複数の出力バッファ64aと、出力バッファ64aのレプリカであり、内部クロック信号RLCLKに同期してフィードバッククロック信号RCLK1を生成し、DLL回路70に供給する出力レプリカ73と、DLL回路70から内部クロック信号RLCLKを受け、複数の出力バッファ64a及び出力レプリカ73に伝送するクロックツリー72とを備え、クロックツリー72は、それぞれDLL回路70から複数の出力バッファ64a及び出力レプリカ73に至る内部クロック信号RLCLKの複数の伝送経路の信号線負荷が互いに実質的に等しくなるよう構成される。

(もっと読む)

分周回路およびそれを備えたPLL回路並びに半導体集積回路

【課題】回路規模および消費電力を増大させることなく、回路全体の分周比の可変範囲をより拡大することのできる分周回路を実現する。

【解決手段】周期信号(s5)を2種類の分周比で分周して第1の分周信号(c1)を出力する可変分周器(2)と、第1の分周信号(c1)のサイクル数のカウント値(c2)を出力し、リセットされるとカウント動作を初期値から再開するカウンタ回路(3)と、カウント値(c2)が比較基準値(a)と一致する度にHighとLowとを反転させたパルス信号(s1)を、第2の分周信号として出力するとともに分周比の切替信号として可変分周器(2)に供給し、カウント値(c2)が比較基準値(a)と一致する度にカウンタ回路(3)にリセット信号(r)を出力する比較器(4)と、比較器(4)に比較基準値(a)を供給する制御回路(5)とを備えている。

(もっと読む)

位相同期回路および無線通信装置

【課題】周波数補正ミスをなくせ、電圧対周波数変換利得Kvcoを低く抑えることが可能で、PLL位相ノイズ設計を緩和できる位相同期回路および無線通信装置を提供する。

【解決手段】キャリブレーション部190は、電圧制御発振器184の出力発振信号の周波数をカウントするカウンタ回路191と、カウンタ回路のカウント結果を保持しておくための第1および第2の記憶回路193,194と、カウンタ回路とターゲット周波数を比較し大小を判定する比較回路195と、比較回路の結果を受けカウンタ回路のカウント結果と第1の記憶回路の保持結果を比較し、電圧制御発振器の容量バンクを制御する制御回路106と、電圧制御発振器にキャリブレーション電圧を生成し与える電圧生成回路197と、カウンタ回路のカウント結果と第1および第2の記憶回路の結果より演算を行い、演算結果に応じて電圧生成回路を制御する処理回路198と、を含む。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

原子発振器

【課題】τ秒平均時間の短い期間における短期安定度を向上させた原子発振器を提供する

。

【解決手段】周波数制御部2は、光検出器の出力信号をデジタル信号に変換するA/D変

換器12と、制御電圧を所定の周期又はデューティ比で間欠的に出力するタイミングを生

成するタイマ(制御周期生成手段)13と、タイマ13により生成されたタイミングに基

づいて出力された制御電圧Vcをアナログ電圧に変換するD/A変換器10と、タイマ1

3のタイミングに基づいて、パワーダウンする期間を指示した信号を出力するIO(パワ

ーダウン生成部)14と、全体の動作を制御するCPU11と、を備え、IO14は、少

なくとも周波数合成逓倍部4、又は/及び、原子共鳴部3をパワーダウンするように構成

されている。

(もっと読む)

基準信号発生装置

【課題】、目的周波数の基準信号の異常を、確実且つ正確に検出することができる基準信号発生装置を実現する。

【解決手段】基準信号発生装置1は、位相比較器11、ループフィルタ12、電圧制御発振器13、分周器14からなるPLL回路を備える。基準信号発生装置1の波数計測部15は、PLL回路の調整用タイミング信号に基づく期間での復調用基準周波数信号の波数をカウントし、期間毎のカウント値を異常発振検出部16へ出力する。異常発振検出部16は、調整用タイミング信号の元となる基準信号と復調用基準周波数信号との仕様周波数範囲の関係に基づいて設定される正常発振カウント値範囲を予め記憶している。異常発振検出部16は、波数計測部15から取得したカウント値が正常発振カウント値範囲内に無ければ異常発振として検出し、外部へ通知する。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

タイミング信号発生回路

【課題】 種々の時間間隔のタイミング信号を低コストで正確に発生させる。

【解決手段】 クロック回路と、クロック信号を入力するカウント回路と、外部から入力する基準タイミング信号を取得し、少なくとも2以上の基準タイミング信号を含む所定の2時点間のカウント回路のカウント値の増分と、該2時点間の時間とを対応させて記録する記憶回路と、カウント回路が所定の2時点間に対応するカウント値だけ増分した時点を中心とする所定の期間に基準タイミング信号を取得し、基準タイミング信号を受信した時点のカウント回路のカウント値を所定の2時点間に対応するカウント値として記録し、所定の2時点間の時間を周期とするタイミング信号をカウント回路のカウント値の増分を契機として発生させ、さらに基準タイミング信号を取得し、基準タイミング信号を取得した時点からカウント値の増分を計数し直す制御手段とを備える。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

ジッタ判定回路およびジッタ判定方法

【課題】従来のジッタを測定する回路では、簡単な回路構成で、正確にジッタの変動率を測定することが困難であった。

【解決手段】ジッタ判定回路は、発振回路と、PLL回路の出力クロックが与えられ、測定期間指定信号に基づいて、測定期間信号を出力する測定期間設定回路と、測定期間信号が出力されている間に発振回路の出力するクロック数をカウントするカウンタと、測定期間信号が出力されている間に発振回路の出力するクロック数の基準カウント値を設定する基準カウント値決定回路と、カウンタのカウントした最大カウント値、最小カウント値及び基準カウント値に基づいてPLL回路のジッタの誤差を判定する誤差判定回路とを有する。

(もっと読む)

CDR回路

【課題】カットオフ周波数をアダプティブに制御する。

【解決手段】CDR回路40には、位相検出器1、シリアル−パラレル変換器2、デジタルフィルタ3、位相制御器4、位相補間器5、積分器6、マルチプレクサ7、及びマルチプレクサ8が設けられる。積分器6は、デジタルフィルタ3で計算されたアーリィ(Early)信号[0:n]−レート(Late)信号[0:n]の符号の情報信号である出力信号SFを入力し、この信号を一定期間Mでモニターし、遅延要素と加算器とを用いて周波数ジッタとして積分する。CDR回路40は、デジタルフィルタの閾値と位相補間器の位相ステップを最適な値に変更して、カットオフ周波数をアダプティブに制御する。

(もっと読む)

DLL回路

【課題】 クロックの立ち上がり及び立ち下がりに同期した内部クロックを生成するDLL回路においては、高精度が要求されることから回路規模が大きくなるという問題がある。

【解決手段】 Rise用の遅延調整回路とFall用の遅延調整回路を備え、Fall用の遅延調整回路にはRise用の遅延調整回路でRise側を調整したクロックを入力する。入力されるクロックのRise側が調整されていることから、Fall側の遅延差は非常に小さくなる。そのため、Fall用の遅延調整回路、カウンタの回路規模が大幅に削減できる。その結果少ない回路規模で、高精度のDLL回路が得られる。

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

1 - 20 / 31

[ Back to top ]