Fターム[5J106JJ06]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 位相変換回路 (78)

Fターム[5J106JJ06]に分類される特許

1 - 20 / 78

半導体装置

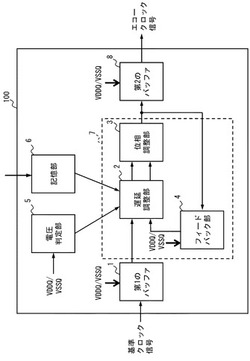

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

半導体装置

【課題】調整コードの変化に伴うジッタの発生が低減されたDLL回路を提供する。

【解決手段】内部クロック信号ECLKを受けるインバータ回路210〜217と、内部クロック信号OCLKを受けるインバータ回路220〜227とを有し、調整コードC0〜C7を受けて選択されたインバータ回路の出力を合成することによって、内部クロック信号LCLKの位相を16段階に調整する。インバータ回路210,220は内部クロック信号LCLKの位相を1段階変化させる能力を有し、インバータ回路211〜217,221〜227は内部クロック信号LCLKの位相を2段階変化させる能力を有する。このように、内部クロック信号LCLKの位相を調整するインバータ回路の最大能力が抑制されていることから、調整コードの変化に伴うジッタの発生が低減される。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

サンプリングクロック生成回路、画像読取装置及び電子機器

【課題】アパーチャディレイをより小さくするアパーチャディレイ調整機能を有するサンプリングクロック生成回路を提供する。

【解決手段】SSCG11からの出力クロック信号に対して所定の遅延量だけ遅延してサンプリングクロック信号を発生してサンプリングホールド回路に供給する、遅延回路21,22及びクロック発生器23からなるサンプリングクロック生成手段と、SSCG11の出力クロック信号に基づいて生成されたCCD駆動クロック信号と、上記サンプリングクロック信号とを位相比較して位相比較結果を出力する遅延型フリップフロップ24と、上記位相比較結果に基づいて、上記駆動クロック信号と上記サンプリングクロック信号との位相差が実質的にゼロとなるように上記サンプリングクロック生成手段の遅延量を制御する制御ロジック回路20とを備えた。

(もっと読む)

フラクショナルPLL回路

【課題】分周器の分周比を変化させることを動作原理としない新規なフラクショナルPLL回路を提供する。

【解決手段】フラクショナルPLL回路は、位相周波数比較器1、チャージポンプ2、ループフィルタ、電圧制御発振器4、位相コントローラ5、及び位相選択回路6を備える。位相選択回路6は、電圧制御発振器4からの出力クロック信号vco_ckのクロックの1周期を等分した位相のうちのいずれかを選択し、選択された位相に立ち上がりエッジを有する移相クロック信号pi_outを生成し、これを帰還信号として位相周波数比較器1に送る。位相コントローラ5は、移相クロック信号pi_outの周期を出力クロック信号vco_ckの周期から予め決められた移相量で変化させるように、位相選択回路6によって選択される移相クロック信号pi_outの立ち上がりエッジの位相を決定し、決定された位相を選択するように位相選択回路6を制御する。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

周波数シンセサイザおよび時間デジタル変換器

【課題】周波数シンセサイザにおいて、ループ帯域内位相ノイズの低減を小面積かつ低電流の構成で実現する。

【解決手段】周波数シンセサイザは、発振器1と、発振器1出力の分周信号CKVと参照信号Frefとの正規化された位相差を検出するTDC回路7とを備え、TDC回路7によって検出された正規化された位相差に基づいて発振器1の周波数を制御する。TDC回路7は、第2の発振器711と、第2の発振器711の出力信号OSC2の周期数をカウントするカウンタ712とを備え、カウンタ712の出力から、分周信号CKVの周期に相当するカウンタ値と、分周信号CKVと参照信号Frefとの位相差に相当するカウンタ値とを得て、これらのカウンタ値に基づいて、正規化された位相差を算出する。

(もっと読む)

半導体装置

【課題】再開トリガ信号を生成できないことによってリードデータの出力タイミングと外部クロック信号の同期が外れてしまうことを防止する。

【解決手段】DLL回路100には、当該DLL回路100を初期起動させるリセット信号RESETと、内部クロック信号LCLKの内部クロック信号ICLKに対する遅延量の制御を当該DLL回路100に再開させる再開トリガ信号RESTARTとが入力され、DLL回路100は、リセット信号RESET又は再開トリガ信号RESTARTが活性化されたことに応じて遅延量の制御を開始し、リセット信RESET号が活性化された後再開トリガ信号RESTARTが活性化される前には、当該DLL回路100のロック後にも遅延量の制御を継続し、再開トリガ信号RESTARTが活性化された後には、当該DLL回路100のロックに応じて遅延量の制御を停止する。

(もっと読む)

DLL回路

【課題】従来のDLL回路では、クロック信号の立ち上がりエッジと立ち下がりエッジとで遅延時間に差が生じる問題があった。

【解決手段】本発明のDLL回路は、入力クロック信号φinに制御電圧Vlfに応じた遅延量を与える遅延バッファBUF1〜BUF4と、入力クロック信号φinを反転させるインバータとINV1、INV2、を含み、入力クロック信号φinを遅延させた出力クロック信号φoutを生成するディレイライン10と、入力クロック信号φinと前記出力クロック信号φoutとの位相差に基づいて制御電圧Vlfを生成する制御電圧生成部とを有し、ディレイライン10は、インバータINV1と遅延バッファBUF1、BUF2とを含む第1の遅延部と、第1の遅延部の後段に設けられ、第1の遅延部と同数のインバータ及び遅延バッファ(INV2、BUF3、BUF4)を含む第2の遅延部と、を有する。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

多相クロック間の相間スキュー検出回路、相間スキュー調整回路、および半導体集積回路

【課題】N相クロックの相間スキューの検出を行なうための基準クロックを半導体集積回路内で生成する。

【解決手段】分周回路14は、N相(4相)クロックCLK1/CLK2/CLK3/CLK4をN+1個(6個)の分周クロックA4(−1)/A1(0)/A2(0)/A3(0)/A4(0)/A1(+1)に分周し、位相比較対象クロック生成回路12は、分周クロックA1(0)/A2(0)/A3(0)/A4(0)から位相比較対象クロックB1/B2/B3/B4を生成する。位相比較基準クロック生成回路13は、分周クロックA4(−1)/A1(0)/・・・/A1(+1)から所定の組み合わせと演算規則に従いN個(4個)の基準クロックC1/C2/C3/C4を生成する。そして、位相比較対象クロックB1/B2/B3/B4と基準クロックC1/C2/C3/C4のそれぞれの位相差を検出する。

(もっと読む)

位相調整装置及び方法

【課題】CCDを駆動するクロック信号を自動的に最適な位相に調整し、CCDからクロック信号成分が出力されない位相調整装置及び方法を提供する。

【解決手段】本発明の位相調整装置は、2相駆動型の電荷結合素子を用いたフィルタ回路に入力する第1の信号及び第2の信号の位相関係を調整する位相調整装置において、第1の信号に対して遅延を与える遅延付与手段と、遅延付与手段により遅延が与えられた第1の信号と、第2の信号とを加算又は減算する合成手段と、合成手段から出力する参照信号の電力値に基づいて、第1の信号と第2の信号とが逆位相となるように遅延付与手段の遅延設定量を制御する位相調整制御手段とを備えることを特徴とする。

(もっと読む)

信号発生装置および試験装置

【課題】ループ帯域より高い周波数のジッタを印加する。

【解決手段】指定された位相の出力信号を発生する信号発生装置であって、所定周期の基準信号と出力信号との位相差に応じた制御信号を出力する位相差検出部と、制御信号の高域成分を除去するループフィルタと、ループフィルタにより高域成分が除去された制御信号に応じた周波数の周期信号を発生する発振部と、指定された位相分、周期信号に対して位相がシフトされた出力信号を出力する位相シフト部と、を備える信号発生装置を提供する。

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

DLL回路

【課題】LPF出力の変化に対するロック周波数の変化量のゲイン設定のばらつきの抑制でジッタ精度をより向上できるDLL回路の提供。

【解決手段】遅延クロックを生成する遅延回路101と、遅延クロックと入力クロックの位相差信号を出力する位相比較回路10と、位相差信号対応の位相差電圧を出力するチャージポンプ回路20と、チャージポンプ回路出力の高周波成分を除去するローパスフィルタ回路30と、ローパスフィルタ回路の出力電圧を電流に変換する第1電圧−電流変換回路40及び基準電圧Vrefを電流に変換する第2電圧−電流変換回路50を含み、第1電圧−電流変換回路の出力電流から第2電圧−電流変換回路の出力電流を減算した結果を変換した電圧とオフセット電流Idを変換した電圧とを含み、位相差電圧が基準電圧より小の場合、オフセット電流を変換した電圧を制御電圧Vcontとして遅延回路に出力する遅延制御回路102と、を備える。

(もっと読む)

位相補償用クロック同期回路

【課題】短時間で精度よく位相調整を行うことが可能な位相補償用クロック同期回路を提供する。

【解決手段】DLLは、入力レシーバ1と、遅延チェーン回路2と、遅延複製器4と、位相比較器5と、リセットパルス発生器6と、粗調整期間発生器7と、分周器8と、単位可変カウンタ9と、を備えている。まず単位可変カウンタ9の増減単位を17または1(平均で16)として粗調整を行って粗くロックさせた後に、単位可変カウンタ9の増減単位を1として微調整を行って細かくロックさせるため、短い期間で確実にクロックINTCKXとクロックEXTCKXの位相を合わせることができる。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

情報システムおよび半導体装置とその制御方法

【課題】周期の小さいジッタに対する低減効果を向上する。

【解決手段】入力クロック信号CLKiを電圧制御遅延回路14を介して出力クロック信号CLKoとして出力すると共に、入力クロック信号CLKiと出力クロック信号CLKoとの位相比較結果に基づいて電圧制御遅延回路14における遅延量を制御する。位相補正回路21は、入力クロック信号CLKiおよび出力クロック信号CLKoを入力とし、DLL回路がロック状態に入った後に、入力クロック信号CLKiおよび出力クロック信号CLKoの位相がずれた場合に、出力クロック信号CLKoの位相に基づいて入力クロック信号CLKiの位相に補正を加え、電圧制御遅延回路14に出力する。

(もっと読む)

1 - 20 / 78

[ Back to top ]