Fターム[5J106JJ08]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | チャージポンプ回路 (109)

Fターム[5J106JJ08]に分類される特許

1 - 20 / 109

PLL回路

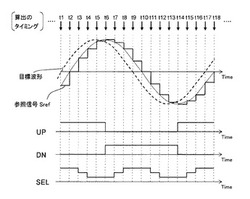

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

PLL回路

【課題】PLLのチャージポンプ回路からの出力電流ミスマッチにより、PLLの特性劣化に繋がるリファレンススプリアスが発生する問題がある。

【解決手段】基準信号とフィードバック信号との位相差に応じて第1、第2のパルス信号を出力する位相比較器と、第1の制御信号に応じて、前記第1、第2のパルス信号のパルス幅をそれぞれ調整した第3、第4のパルス信号を生成するパルス幅調整回路と、前記第3、第4のパルス信号に応じて出力電流を生成するチャージポンプと、前記チャージポンプの出力に接続され、電流を電圧に変換するループフィルタと、前記ループフィルタの変換した電圧を積分した検出結果を出力する検出回路と、前記検出結果に応じて、前記第1の制御信号を生成する制御回路と、を有するPLL回路。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

PLL回路

【課題】PLL回路のロック状態での定常位相誤差を抑制する。

【解決手段】PLL回路は,レファレンスクロックとフィードバッククロックの位相を比較し,当該位相の差を示す位相比較信号を出力する位相比較器と,位相比較信号が示す位相の差に応じた期間,第1のチャージポンプ電流と第2のチャージポンプ電流とを出力するチャージポンプ回路と,第1及び第2のチャージポンプ電流に基づく電荷を蓄積するキャパシタを有し,蓄積電荷による制御電圧を生成するループフィルタと,制御電圧に応じた周波数の出力クロックを生成する発振器と,出力クロックを分周して前記フィードバッククロックを出力する分周器とを有し,さらに,ロック状態のときに,位相比較信号が示す位相の差に応じて,当該位相の差が抑制されるように,第1または第2のチャージポンプ電流の電流値を調整するチャージポンプ調整回路とを有する。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

位相ロックループ回路

【課題】簡素な回路構成で、電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路1と、検出された位相差に応じた電流を容量に出力するチャージポンプ回路2と、容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路4とを有する位相ロックループ回路にて、制御電圧がロック状態時の電圧であった場合に電圧制御発振回路4の入力部に流れるリーク電流に等しい電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

チャージポンプ回路

【課題】充放電電流の立ち上がりを高速にし、かつ誤動作のおそれがないチャージポンプ回路を提供する。

【解決手段】ダイオード接続されたトランジスタMp1と、トランジスタMp2と、指令信号UPbで制御されてMp1,Mp2のゲート間を接続するトランジスタMp3とで第1のカレントミラー回路が構成されている。トランジスタMp2のゲート電極と電源VDDの間には指令信号UPbで制御されるトランジスタMp4が接続されている。また、ダイオード接続されたトランジスタMn1と、トランジスタMn2と、指令信号DNで制御されてMn1,Mn2のゲート間を接続するトランジスタMn3とで第2のカレントミラー回路が構成されている。Mn2のゲート電極と接地の間には、指令信号DNbで制御されるトランジスタMn4が接続されている。

(もっと読む)

PLL/DLL用の高出力インピーダンスチャージポンプ

【課題】チャージポンプにおけるスタティック位相誤差を最小限にする。

【解決手段】位相ロックループ/遅延ロックループで使用するためのチャージポンプは、プルアップ回路とプルダウン回路と演算増幅器とを含む。チャージポンプはプルアップおよびプルダウン回路の動作に関連したスタティック位相誤差を最小限にするように設計される。演算増幅器の使用はまた、低電源電圧の影響を軽減する。

(もっと読む)

チャージポンプ回路

【課題】後段のループフィルタの状態によらずに電流誤差を低減し、且つ、高速動作が可能なチャージポンプ回路を提供する。

【解決手段】VDDの端子とノードN1との間に接続される定電流源I1と、VSSの端子とノードN2との間に接続される定電流源I2と、入出力端子ICPとノードN1との間に接続され信号UPが入力するトランジスタMP1と、入出力端子ICPとノードN2との間に接続され信号DNが入力するトランジスタMN1と、入出力端子ICPに入力側が接続される電圧増幅器11と、ノードN1と電圧増幅器11の出力側に接続され信号UPの反転信号UPBが入力するトランジスタMP2と、ノードN2と電圧増幅器11の出力側に接続され信号DNの反転信号DNBが入力するトランジスタMN2とを備える。

(もっと読む)

チャージポンプ回路及びそれを用いるPLL回路

【課題】電流供給および吸入用の定電流源と、それらの定電流源の間に設けられる2つの直列に接続されたスイッチ素子から成り第1の出力端子を持つ主出力側電流路と、同様に2つのスイッチ素子から成り第2の出力端子を持つ副出力側電流路とを備え、位相比較器からの駆動信号に応答して、主出力側電流路のスイッチと副出力側電流路との各スイッチ素子が開閉し、第1の出力端子から正負の電流パルスが出力される差動スイッチング方式のチャージポンプ回路において、ダイ面積を縮小するとともに、消費電力を削減する。

【解決手段】主出力側電流路のスイッチ素子Q7,Q8間の電位と副出力側電流路のスイッチ素子Q5,Q6間の電位との差に起因して定電流源Q3,Q4の寄生容量の充放電に伴い発生する緩慢なグリッチを補償するために、コンパレータ37と、ラッチ回路38と、コンデンサC1と、充放電器Q9,Q10とを用いてグリッチ補償回路36を構成する。

(もっと読む)

PLL回路

【課題】基準周波数信号がPLL回路に入力されなくなった場合に、チャージポンプ回路にループフィルタから電流が流れ続けることを防止する。

【解決手段】PLL回路1は、入力された電圧に応じた周波数のVCO信号を出力するVCO20と、入力された電流に応じた電圧をVCO20に与えるループフィルタ18と、第一入力信号と第二入力信号との位相差に応じた幅の位相差パルスを出力する位相比較器14と、位相差パルスを受けて、ループフィルタ18への電流入力を行うチャージポンプ回路16と、REF信号(基準周波数信号)が入力されていない無入力状態において、チャージポンプ回路16への位相差パルスの入力を停止させる位相差パルス停止部30とを備える。なお、第一入力信号は、REF信号自身又はそれを分周した信号であり、第二入力信号は、VCO信号自身又はそれを分周した信号である。

(もっと読む)

PLL回路

【課題】ループフィルタの回路面積を削減すると共に、電圧制御発振器の動作の安定化やノイズ感度の低減が可能なPLL回路を提供することである。

【解決手段】本発明のPLL回路は、位相比較器3の出力信号に応じて出力電圧を制御する第1及び第2のチャージポンプ回路4、5と、第1のチャージポンプ回路4の出力に基づく信号から所定の周波数成分が除去された第1の電圧信号を出力する第1のフィルタ6と、第2のチャージポンプ回路5からの電流を入力し、所定の一定電圧を第2の電圧信号として出力する第2のフィルタ7と、第1のフィルタ6からの第1の電圧信号と基準電圧との比較結果に基づき第3の電圧信号を出力する電圧制御部30と、第1及び第2の電圧信号を低ゲイン入力、第3の電圧信号を高ゲイン入力とし、当該第1乃至第3の電圧信号に基づき発振周波数を生成する電圧制御発振器10を備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

PLL回路

【課題】温度変動による位相雑音の悪化を低減することが可能なPLL回路を提供することを目的とする。

【解決手段】電圧制御発振回路81と、分周器82と、基準信号REF-INと発振信号Outputとの互いの位相を比較し、位相差に応じたパルス幅のパルス信号UP、DOWNを出力する位相比較器と、パルス信号UP、DOWNのパルス幅に応じた大きさのCP電流ICPp、ICPnを出力する出力電流補正機能付きチャージポンプ1と、CP電流ICPp、ICPnに応じてVt電圧を制御するループフィルタ85と、温度変動に応じて遅延時間が変化する遅延回路8とを備えてPLL回路100を構成し、遅延回路8の遅延時間に基づいて、CP電流ICPpとCP電流ICPnとの差が小さくなるように、CP電流ICPp又はCP電流ICPnを補正する。

(もっと読む)

位相同期回路

【課題】位相誤差および周波数精度等の性能に優れ、かつ低価格で、広い制御電圧入力範囲を持つ電圧制御発振器を利用したPLL回路を提供する。

【解決手段】位相比較器11とチャージポンプ12は、低電圧トランジスタで構成され、電源電圧VLの可変電圧源16と電源電圧VDC(=VL+VCC1)の可変電圧源17から与えられる差の電圧VCC1(例えば、5V)で動作する。チャージポンプ12の出力電流をループフィルタ14で積分して生成された制御電圧VCは、0〜VCC2(例えば、16V)を制御電圧入力範囲とする電圧制御発振器15に与えられる。このとき、制御電圧VCの変化範囲は5V以下となるが、可変電圧源16,17の出力電圧VL,VDCを制御することで変化範囲を0〜16Vに拡大し、電圧制御発振器15から所望の周波数の出力信号OUTを出力させることができる。

(もっと読む)

放射線硬化チャージポンプ・トポロジ

【課題】シングル・イベント・アップセット(SEUs)により影響されにくいチャージポンプ回路を提供する。

【解決手段】第1のチャージポンプ出力を備えた第1のチャージポンプ30と、第2のチャージポンプ出力を備えた第2のチャージポンプ32と、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するように受け取り、第1の一致信号を出力するように生成する第1の一致検出器34と、第1の一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2:1マルチプレクサ36とを有する。

(もっと読む)

1 - 20 / 109

[ Back to top ]