Fターム[5J106LL06]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 図面 (361) | 可変分周回路、可変カウンタ (21)

Fターム[5J106LL06]に分類される特許

1 - 20 / 21

周波数シンセサイザ

【課題】少数点逓倍の精度を向上させ、累積ジッタを低減した周波数シンセサイザを提供する。

【解決手段】位相比較器1と、チャージポンプ2と、ローパスフィルタ3と、電圧制御発振器4と、該電圧制御発振器の出力クロック信号を小数点分周して前記帰還クロック信号を生成する帰還回路とを備える。帰還回路は、電圧制御発振器4の出力クロック信号を分周する可変分周器5と、電圧制御発振器4の8相のクロック信号から1つの位相のクロック信号を選択するマルチプレクサ7と、マルチプレクサ7で選択した特定の位相のクロック信号により可変分周器5のクロック信号をリタイミングするリタイミング回路(DFF回路8,9とアンド回路10)とを備える。

(もっと読む)

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

PLL回路

【課題】温度変化により電圧制御発振器を制御する制御電圧に変動が発生しても位相同期回路のロックが外れることを最小限の電圧制御発振器により防止する位相同期回路を提供する。

【解決手段】発振周波数帯域の異なる複数の電圧制御発振器を備えるPLL回路であって、ループフィルタから出力される電圧制御発振器制御電圧の温度特性と正の相関関係にある基準電圧を出力する基準電圧源回路と、電圧制御発振器制御電圧と基準電圧とを比較して判定する判定回路と、判定回路の出力信号により複数の電圧制御発振器から1つの電圧制御発振器を選択する選択回路と、を備えるPLL回路である。

(もっと読む)

PLL回路

【課題】PLL回路のロックアップ時間を短縮することである。

【解決手段】VCO・電流切替回路15は、外部から与えられる分周データに基づいて、複数のVCO22a〜22nの内の1つを選択するVCO選択信号を出力する。また、VCOを切り替える際に、可変チャージポンプ20の出力電流を通常(ロック時)より大きな値に変更する切替信号を出力する。VCO・電流切替回路15は、VCOの切り替えが終了したなら、可変チャージポンプ20の出力電流を通常時の小さい値に切り替える切替信号を出力する。

(もっと読む)

位相同期ループ回路

【課題】出力周波数レンジの広いPLL回路を提供すること。

【解決手段】本発明の一態様は、入力パルス信号と出力側からフィードバックされたフィードバックパルス信号との位相差に基づいて生成された電圧を、制御電流Icへ変換する電圧電流変換回路104と、制御電流Icに応じた周波数のパルス信号を生成する電流制御発振器105と、制御電流Icを検出する電流検出部108と、検出された前記制御電流に基づいて、電流制御発振器105から発振される出力パルス信号の周波数レンジを切り替える周波数レンジ切替回路106と、を備えた位相同期ループ回路である。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

信号発生回路

【課題】広帯域の信号を発生させる場合において、消費電力を低減することが可能な信号発生回路を提供することを目的とする。

【解決手段】基準信号aを出力する基準信号源51と、基準信号aと出力信号cとの位相差に対応する電圧を出力する位相比較器53と、位相比較器53から出力される電圧に基づく発振信号bを出力する電圧制御発振器55と、発振信号bを分周して出力信号cを出力する分周回路3と、ロック検出器56と、基準信号aと出力信号cとの位相差がゼロであることを示すフラグ信号fがロック検出器56から出力されている間、分周回路3に流れる電流を所定量ずつ下げ続け、その後、ロック検出器56からフラグ信号fが出力されなくなると、分周回路3に流れる電流を少なくとも上記所定量上げて再度上記位相差をゼロにさせる制御回路2とを備えて信号発生回路1を構成する。

(もっと読む)

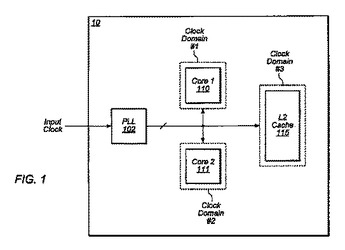

クロックサイクルスチールのための方法および装置

複数のクロック信号を生成するための方法。前記方法は、位相ロックループ(PLL)を使用して基準クロック信号を生成するステップを有する。前記基準クロックが、複数のクロック分周器ユニットのそれぞれに供給され、前記複数のクロック分周器ユニットのそれぞれが、前記受信基準クロック信号を分周して、対応する分周クロック信号を生成する。前記方法は、前記対応する受信分周クロック信号の周波数と、除去するサイクル数とに基づいて、それぞれが有効周波数を有する複数のドメインクロック信号を生成するために、(所定の数のサイクルにつき)1以上のクロックサイクルを除去する。  (もっと読む)

(もっと読む)

PLL回路

【課題】エクステンダ部の動作遅延時間を短縮して、分周比切り替え動作の誤動作に対するマージン時間を十分に確保し得るプリスケーラを提供する。

【解決手段】プリスケーラ21bは、分周比切り替え信号に基づいて、分周比を切り替えながら入力信号fvcoを分周する分周切り替え部Cと、分周切り替え部の出力信号を所定の分周比で分周するエクステンダ部Eとを備える。分周切り替え部Cは複数段のフリップフロップFF1〜FF3を有し、エクステンダ部Eの少なくとも一部を同期型カウンタで構成するとともに、少なくとも一部を非同期型カウンタで構成する。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

時間デジタル変換装置およびデジタル位相同期ループ装置、受信機

【課題】広帯域の周波数範囲に対応可能で、量子化ノイズ成分を増大させることなく低消費電力化を図る。

【解決手段】時間デジタル変換器104は、発振周波数を制御する周波数制御信号16を用いて、入力周波数に応じて動作する遅延回路10−1〜10−nの段数を切り替えるスイッチング素子12−1〜12−nを備えている。入力周波数の周期に応じて必要な段数の遅延回路だけが動作することとなるため、広帯域の周波数範囲に対応しながらも系全体の低消費電力化を図ることが可能となり、特に高い入力周波数において低消費電力化を図ることができる。

(もっと読む)

シグマデルタ変調器およびフラクショナル周波数シンセサイザ

【課題】出力信号の増加および減少の振幅を小さくする。

【解決手段】入力信号をシグマデルタ変調した出力信号を出力するシグマデルタ変調器であって、直列に接続された複数の累算器と、それぞれの累算器が出力する比較結果信号に基づいて、出力信号を生成する出力信号生成部とを備え、それぞれの累算器は、入力される信号の値を積分し、積分値が基準値以上となった場合に、所定の値の比較結果信号を出力すると共に、積分値から比較結果信号の値を減算し、初段の累算器には、入力信号の値が入力され、他の累算器には、前段の累算器の積分値が入力され、少なくとも一つの累算器は、積分値の波形の所定の高周波成分を除去するローパスフィルタを有するシグマデルタ変調器を提供する。

(もっと読む)

半導体集積回路

【課題】フラクショナル−N PLL回路のサイクルトゥサイクルジッターを低減すること。

【解決手段】フラクショナル−N PLL回路は、位相周波数比較器PFD、チャージポンプ回路Ch_Pmp、ループフィルタLp_Flt、電圧制御発振器VCO、フラクショナル分周器DIV、ΣΔ変調器ΣΔModを含む。基準クロック信号RCLKと出力帰還信号VCLKとの位相差の検出動作に基づくループフィルタLp_Fltの出力電圧VCNTの電圧生成動作が時間差を有する複数の動作により実行されるように位相周波数比較器とチャージポンプ回路との一方が構成されている。

(もっと読む)

マルチモードの移動通信装置のための構成可能なマルチモジュラス分周器

移動通信装置(例えば、携帯電話)内部には、局部発振器がある。局部発振器は、新規な構成可能なマルチモジュラスディバイダ(CMMD)を含む新規な分周器、を含む。分周器は、同期および非同期回路の異なる組み合わせを伴う複数の構成のうちの選択可能な1つ、に構成可能である。各構成において、分周器は、ある雑音量を発生させ、ある電力量を消費する。電力消費が最大のモードは最小の雑音量を生じさせ、その逆も同様であるというように、電力消費は、発生される雑音に対してゆるく逆に関連付けられる。移動通信装置は、複数の異なる通信規格(例えば、GSM、CDMA1X、およびWCDMA)のうちの1つで動作可能である。異なる通信規格は、分周器に対して異なる雑音要件を課す。使用される規格の雑音要件を満たす最も低電力な構成を使用することによって、携帯電話の電力消費が軽減される。  (もっと読む)

(もっと読む)

PLL周波数シンセサイザ、半導体集積回路および通信装置

【課題】 消費電力を低減することが可能な、動作の安定性が高いPLL周波数シンセサイザ、半導体集積回路および通信装置を提供する。

【解決手段】 可変分周器は、複数段のD−FF21,22,23,・・・で構成される。D−FF21において、スイッチ回路SW1〜SW5がオフ状態のとき、トランジスタTr1,Tr3によってバイアス電流I1,I3が流れる。スイッチ回路SW1〜SW5がオン状態のとき、トランジスタTr1〜Tr4によってバイアス電流I1〜I4が流れる。また、Q端子36およびQX端子37から出力される信号の電圧振幅は、常に(Ibias×RL)/2となる。したがって、可変分周器の消費電力を低減することが可能になる。

(もっと読む)

分周器

【課題】低消費電力で高周波動作可能な、分周器を実現する。

【解決手段】図1に示すように、分周器の単位要素となるラッチ回路を、負荷としてインダクタンスL1、L2が設けられたECLロジック回路で構成し、前記ラッチ回路の出力を、前記インダクタンスL1、L2との組み合わせで、使用周波数において回路出力のインピーダンス整合が最適となるように値を選択した、キャパシタC1、C2を介して次段回路に接続して分周器を構成する。分周器を構成する各ラッチ回路の段間インピーダンス整合をとることができるので、トランジスタの持っている性能が最大限に引き出され、従来のECLロジック分周器よりも少ない消費電流で高速分周動作をさせることが可能となる。

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

シグマデルタベースのフェーズロックループ

位相周波数検出器(PFD)と、チャージポンプと、電圧制御発振器とを含むシグマデルタベースのフェーズロックループ・デバイスが提供される。PDFは、基準信号とフィードバック信号とを受信し、基準信号とフィードバック信号との比較に基づく信号を出力する。チャージポンプは、PFDからの出力信号に基づくチャージを出力する。チャージポンプは、固定量の電流を流す第1の電流源と、可変量の電流を流す第2の電流源とを含む。電源制御発振器は、チャージポンプからの受け取ったチャージに基づくクロック信号を出力する。  (もっと読む)

(もっと読む)

通信用半導体集積回路

【課題】 使用周波数帯を決定するまでに要する時間が長くならないとともに回路の占有面積を小さくすることができ、また、リセット信号等の遅延により誤った周波数帯が選択されない自動バンド選択回路を備えたPLL回路を内蔵した高周波ICを提供する。

【解決手段】 VCO11の発振周波数を制御するPLLループにおいて、所定の周波数の基準信号に対する可変分周回路12の出力の位相の進みまたは遅れを判別する判別回路22と、該判別回路の出力に基づいてVCOの周波数帯を切り替える信号を生成する自動バンド選択回路20と、信号の遅延に基づく位相判別におけるずれを測定しそれを補償するような遅延を固定分周回路14で分周された信号に与える遅延補償回路25とを設け、2分探査方式でVCOの周波数帯を切り替えながら最適な周波数帯を見つけて使用周波数帯を決定するようにした。

(もっと読む)

1 - 20 / 21

[ Back to top ]