Fターム[5J106SS05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 細部の構成 (94) | その他の部分の具体的回路が示されたもの (23)

Fターム[5J106SS05]に分類される特許

1 - 20 / 23

PLL回路

【課題】短時間でかつ正確に、所望の周波数の発振信号にロック可能なPLL回路を提供する。

【解決手段】PLL回路は、粗調整ループ部と微調整ループ部を有する。前記粗調整ループ部は、前記複数の第1切替部の切替情報を記憶する切替情報記憶部と、複数の第1切替部の新たな切替情報を設定する切替情報設定部と、切替情報設定部で設定した複数の第1切替部の切替情報に基づいて調整した電圧制御型発振器の発振信号を分周した分周信号を生成する分周器と、分周信号の周波数と基準信号の周波数とを比較した結果に基づいて、切替情報設定部に対して切替情報の再設定を指示する発振周波数調整部と、切替情報設定部で設定した切替情報と、切替情報記憶部に記憶されている切替情報と、の差分情報を生成し、該差分情報が所定の閾値範囲内であれば、ループ制御部に粗調整の終了を報知し、差分情報が閾値範囲外の場合には、切替情報設定部に対して切替情報の再設定を指示する比較器と、を有する。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

信号処理回路

【課題】内部回路の内部クロックと内部回路の入力信号との位相関係により内部回路の出力が変動する場合であっても、安定した回路動作とすることができる信号処理回路を得る。

【解決手段】入力信号と位相制御信号とを受け、前記入力信号及び前記位相制御信号の位相差に基づき位相比較信号を出力する位相比較手段と、前記位相比較信号を受け、前記位相比較信号に基づく周波数で発振する発振信号を出力する発振手段と、前記発振信号を受け、前記位相制御信号を出力する位相制御信号発生手段とを備え、同時に前記位相制御信号を出力信号とし、該位相制御信号を内部クロックとして供給することを特徴とする位相差制御回路である信号処理回路等を提供する。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

半導体装置

【課題】フラクショナルN−PLL回路における出力クロック信号でのスプリアスの発生を抑制する。

【解決手段】出力クロック信号を出力する電圧制御発振器と、出力クロック信号を分周して分周クロック信号を生成し、基準クロック信号と分周クロック信号とを比較し、比較結果に基づき出力信号を出力するN個の制御ユニットと、各制御ユニットからの出力信号を加算する加算器と、加算器の出力をフィルタ処理し電圧制御発振器に出力するローパスフィルタとを備え、分周クロック信号に同期して所定の順序で巡回させ供給するN個のデータからなる分周比に係る設定情報を、各制御ユニットに対して初期値を互いに異ならせて供給し分周動作及び比較動作を行わせるようにして、N個の制御ユニットにより移動平均フィルタを形成し量子化ノイズを低減し、出力クロック信号でのスプリアスの発生を抑制できるようにする。

(もっと読む)

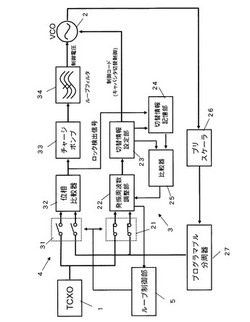

2点FSK変調を用いる周波数シンセサイザのための自己較正方法

【課題】2点FSK変調を用いる周波数シンセサイザの自己較正方法の提供。

【解決手段】周波数シンセサイザ1が、第1の位相ロック・ループおよび高周波アクセス部を備え、高周波アクセス部は、電圧制御発振器の第2の入力に接続されたデジタル/アナログ変換器20を備える。較正動作のために、高周波アクセス部に、第1の位相ロック・ループ内の位相比較器3に接続された第2の電荷ポンプ14および第2のループ・フィルタ15を備える。第2の電荷ポンプ14が、オンに切り替えられると、第2の位相ロック・ループを形成する。デジタル/アナログ変換器20の利得を較正するために、決められた出力周波数に予めロックされた第2の位相ロック・ループの第2の電荷ポンプ14を切り離した後に、電圧比較器21が、デジタル/アナログ変換器20の出力電圧を、第2のループ・フィルタ内に蓄えられた電圧と比較する。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

ローカル信号生成回路

【課題】従来のローカル信号生成回路は、回路面積と消費電力が大きくなる問題があった。

【解決手段】本発明にかかるローカル信号生成回路は、基準信号と帰還信号の位相差を検出し、誤差信号を出力する位相比較器21aと、誤差信号を受け昇圧電圧を生成するチャージポンプ回路22aと、昇圧電圧を整形してチューニング電圧Vtuを生成するループフィルタ23aと、チューニング電圧Vtuに基づき所定の周波数を有する第1の出力信号(I_high、Q_high)を生成する電圧制御発振器24aと、第1の出力信号(I_high、Q_high)を所定の周波数に分周した第2の出力信号(I_low、Q_low)として出力すると共に、第1の出力信号(I_high、Q_high)を前記所定の周波数に分周した分周信号を帰還信号を生成する分周器26aに出力するプリスケーラ25aと、を有するものである。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

フィードフォワード分割器を有する適応帯域幅位相ロックループ

【課題】位相ロックループを提供する。

【解決手段】一部の実施形態では、チップは、第1及び第2の電圧制御式発振器(VCO)出力信号を供給するための第1及び第2のVCOと、第1及び第2VCO出力信号の第1及び第2の周波数を第1及び第2の分周率によって分割するための第1及び第2のフィードフォワード分割回路とを含む第1及び第2のサブ位相ロックループ(サブPLL)を含む。チップはまた、第1及び第2分周率を選択するための位相ロックループ制御回路を含む。他の実施形態も説明して特許請求する。

(もっと読む)

通信用半導体集積回路

【課題】送受信動作に使用する周波数シンサセイザとしてフラクショナルN PLL回路を含むRF通信用半導体集積回路において、PLL回路のチャージポンプ回路CPCのソース電流注入トランジスタとスィンク電流放出トランジスタとのミスマッチに起因する非線型性の影響を軽減する一方、PLL回路の位相ノイズを低減するための補償回路の回路規模を小さくして補償回路の制御も単純化すること。

【解決手段】受信動作と送信動作とに使用する周波数シンサセイザFrct_SynthとしてフラクショナルN PLL回路のクローズドループ帯域を、数十KHzのオーダーの狭帯域とする。チャージポンプ回路CPCの2つのトランジスタのミスマッチに起因する非線型性の影響の軽減を最も段純な方法であるオフセット回路MN2、MN3によるループフィルタLFCへのdc直流電流Ioffsetの注入もしくはLFCからのIoffsetの放出によって実現する。

(もっと読む)

PLL回路及びチャージポンプ回路の駆動方法

【課題】PLL回路のロック時のループフィルタの出力電圧の変動を抑えることである。

【解決手段】基準クロック信号と帰還クロック信号の位相が一致したとき、基準クロック信号と帰還クロック信号の立ち下がりのタイミングで、オン時間の短いUP信号とDOWN信号をチャージポンプ回路の2個のMOSトランジスタに供給する。これにより、チャージポンプ回路の貫通電流を少なくできるので、貫通電流によるループフィルタの出力電圧の変動を抑えることができる。

(もっと読む)

プリスケーラ及びバッファ

【課題】広帯域化を図ることができるプリスケーラを提供すること。

【解決手段】プリスケーラ33は、バッファ部41とカウンタ43とを備える。バッファ部41は、駆動能力が異なる複数のインバータ回路52a〜52cからなる初段回路52と、直列接続された複数のインバータ回路54a〜54dと、帰還回路55とを備える。初段回路52の各インバータ回路52a〜52cは、第1スイッチ部51と第2スイッチ部53とにより、何れか1つに信号fvが入力され、出力端子が後段のインバータ回路54aに接続され、初段回路52における駆動能力が可変される。帰還回路55は、電圧V1,V2により設定される抵抗として機能する。

(もっと読む)

通信用半導体集積回路

【課題】基準周波数発振器DCXOの発振出力信号をレベル変換器Lev_Convによりレベル変換する際に発生するDCXOの発振出力信号の高調波成分によるRF送信用電圧制御発振器TXVCOの発振出力信号の近傍への漏れ込みによる影響を低減すること。

【解決手段】レベル変換器Lev_ConvはDCXOの発振出力信号をレベル変換して、レベル変換信号をRF送信用電圧制御発振器TXVCOの発振周波数を制御するPLL・フラクショナルシンセサイザFrct_Synthの位相比較器PDCに供給する。このLev_Convは、基準周波数発振器DCXOの基準周波数信号を増幅する自己バイアス型電圧増幅器Self_Bias_Volt_Ampを含む。自己バイアス型電圧増幅器は、結合容量C1、増幅トランジスタQn5、負荷Qp5、バイアス素子R1を含み、外部電源電圧Vdd_extが変動しても、高調波成分のレベル変動を抑制する。

(もっと読む)

ディジタルPLL装置

【課題】入力信号の周波数が変動してもジッタを低減させることが可能なディジタルPLL装置を提供する。

【解決手段】本発明の一実施形態に係るディジタルPLL装置は、入力信号に対する再生クロックの位相遅れ、位相進みを検出する位相検出器と、位相検出器からの出力信号を積分し、積分値に応じて位相ずれ信号を発生するランダムウォークフィルタ部と、入力信号の周波数値に応じた値を有する周波数信号を生成する周波数検出器と、位相ずれ信号の値と周波数信号の値とを加算した値を有する制御信号を生成する加算器と、制御信号の値を分周比として、マスタークロックを分周した再生クロックを生成する制御分周部と、を備える。制御分周部における分周比の中心値N(Nは自然数)は、周波数信号の値によって定められることを特徴とする。

(もっと読む)

周波数シンセサイザ、通信機、及び周波数シンセサイズ方法

【課題】高精度のクロックを高速に切り換えることの出来る周波数シンセサイザ、通信機、及び周波数シンセサイズ方法を提供する。

【解決手段】高精度に生成された基準クロックを元に、デジタル的な演算とD/Aコンバータ、ローパスフィルタを用いて所望の周波数の正弦波信号を発生させ、その正弦波信号を元の基準クロックとミキシングし、適切なフィルタを通す事で所望の周波数の正弦波を生成する事ができる。また、ミキシング後のバンドパスフィルタの中心周波数や、上記正弦波信号を発生させる演算処理、あるいは出力部のセレクタを変化させる事で、基準クロックの周波数を変更する事無く周波数切り換えを行うので、高速な周波数切り換えを実現する事ができる。周波数生成に用いる正弦波信号はデジタル的な演算によって生成されるので、周波数制御を精度良く行う事ができる。

(もっと読む)

1 - 20 / 23

[ Back to top ]