Fターム[5J500AA13]の内容

Fターム[5J500AA13]に分類される特許

21 - 40 / 165

広帯域増幅器

【課題】RFで動作するシングルエンド出力であるフィードバック型の広帯域増幅器における二次歪み耐性を向上させる。

【解決手段】主増幅MOSトランジスタQ1を含むシングルエンド出力であるフィードバック型の主増幅器310における電圧−電流変換抵抗素子R1と並列に主増幅器310とは逆極性のMOSトランジスタで構成されたバイパス回路320を設け、このバイパス回路320の副増幅MOSトランジスタQ3へのバイアス値を所定値に合わせ込むことによって、主増幅器310に生じる二次歪成分のみに対し逆極性で且つ相似な特性を呈するバイパス作用信号を生成し、該バイパス作用信号で主増幅器310に生じる二次歪成分をバイパス回路320側に引き込むことによって、主増幅器310とバイパス回路320とを含む広帯域増幅器300の二次歪み耐性を向上させる。

(もっと読む)

金属検出システム作動方法及び金属検出システム

【課題】2つ以上の送信周波数を使用する金属検出システムを提供する。

【解決手段】少なくとも2つの送信周波数グループから選択される送信周波数を有する送信信号を生成する送信装置3と接続される送信コイル4と、受信装置5に含まれる少なくとも1つの増幅装置14,15の信号入力へ出力信号を提供し、出力信号が、システムが平衡状態にあるように相互に相殺する第1及び第2の受信コイル6,7とを備えた、平衡コイルシステムを含む金属検出システム1を作動させる。制御装置16が、少なくとも1つの増幅装置14,15の信号入力と接続される少なくとも1つの制御可能インピーダンス装置12,13の制御入力に提供される制御信号を送信装置3の送信周波数に従って生成し、送信周波数が増減されるとき、インピーダンス値が増減されるような方法で制御信号が、制御可能インピーダンス装置12,13のインピーダンス値を制御する。

(もっと読む)

広帯域増幅器

【課題】RF(Radio Frequency)で動作する、シングルエンド出力であるフィードバック型の広帯域増幅器において、特に二次歪み耐性に優れたフィードバック型の広帯域増幅器を実現する。

【解決手段】入力信号を電圧−電流変換して出力するMOSトランジスタQ1の出力電流を第1の抵抗素子R1によって出力電圧に変換し、該出力電圧をMOSトランジスタQ1の入力に第2の抵抗素子R2によってフィードバックする。さらに、第1のバイアス回路(VG1+R3)からMOSトランジスタQ1の入力へバイアスを供給する。そして、このバイアス値を、MOSトランジスタQ1のドレイン電流が流れるように、且つ、MOSトランジスタQ1のドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるように設定する。

(もっと読む)

パススルー付き増幅器

【課題】パススルーモード時の通過特性を向上できかつ低電源電圧化に対応できるパススルー付き増幅器を提供する。

【解決手段】パススルーモード時に、信号伝達用トランジスタ(M1)とともにバイアス制御用トランジスタ(M2)をオンさせて、出力端子OUTの電圧をバイアス制御用トランジスタ及び抵抗(R1)を介してグランド電位に維持させる。これにより、信号伝達用トランジスタの制御端子には電源電圧が印加され、信号伝達用トランジスタの一方の主端子はグランド電位に維持されるので、信号伝達用トランジスタのオン抵抗が最大限に減少する。

(もっと読む)

位相可変増幅器

【課題】回路規模が小型で低消費電流、出力信号の線形性に優れ、周波数特性が平坦であって、その上低ノイズの位相可変増幅器を提供する。

【解決手段】入力信号の位相を調整する移相部1、位相が調整された後の信号のゲインを増幅するゲイン可変増幅部2によって位相可変増幅器を構成する。そして、移相部1は、全域通過フィルタで構成される可変容量の容量素子103、容量素子103がエミッタとベースとの間に接続され、調整された入力信号の位相に対応する位相電流を生成するトランジスタ101を含み、可変ゲイン増幅部2は、移相電流がテール電流として供給されるトランジスタ108、トランジスタ109を含む差動対、トランジスタ109に流れる電流を電圧に変換する抵抗素子107、トランジスタ108、トランジスタ109に流れる電流を制御する制御信号を出力する制御回路106を含む。

(もっと読む)

CMOSオペアンプ、センサ装置

【課題】信号の信号レベルを増幅するに際し、十分な利得を得ながら、サーマルノイズとフリッカノイズとの両者を同時に低減することができるCMOSオペアンプ、及びセンサ装置を提供することを目的とする。

【解決手段】第1MOSFETQ1及びQ2が配置されており、互いに信号レベルが異なる2種類の信号の入力を受け付ける信号入力部10と、第2MOSFETQ4〜Q11が配置されており、信号入力部10により受け付けられた2種類の信号の差分を増幅して出力する信号出力部11と、を備える。第1MOSFETQ1及びQ2のゲート酸化膜の厚さは、第2MOSFETQ4〜Q11のゲート酸化膜の厚さよりも小さく、第2MOSFETQ4〜Q11のゲート酸化膜の厚さは、基準厚さを超える厚さとされており、基準厚さは、第2MOSFETQ4〜Q11が予め設定された利得を得ることができる基準電圧値のゲート電圧に耐える厚さとされている。

(もっと読む)

アクティブポストディストーション線形化を有する増幅器

【課題】アクティブ回路を線形化する。

【解決手段】第1、第2のトランジスタで構成される主信号経路は、主信号経路内の回路素子の非線形性に起因する歪みを生成する。第3及び第4のトランジスタで構成される補助信号経路は、主信号経路によって生成された歪み成分を除去するために用いられる歪み成分をアクティブに生成することによって、3次歪み成分を除去することが可能となる。前記第2及び第3のトランジスタのサイズは、前記増幅器に関する利得損失を低減させて優れた線形性を達成させるサイズが選択される。

(もっと読む)

半導体集積回路

【課題】より安定して動作することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第1の電流供給回路の他端にドレインが接続され、ダイオード接続された第1のMOSトランジスタと、第1のMOSトランジスタのソースにドレインが接続され、第1の電位と異なる第2の電位にソースが接続され、第1のMOSトランジスタのゲートにゲートが接続された第2のMOSトランジスタと、第2の電流供給回路の他端にドレインが接続され、第1のMOSトランジスタのソースにソースが接続され、ダイオード接続された第3のMOSトランジスタと、出力端子にドレインが接続され、第3のMOSトランジスタのドレインにゲートが接続された第4のMOSトランジスタと、第4のMOSトランジスタのソースにドレインが接続され、第2の電位にソースが接続され、予め設定された電圧がゲートに印加された第5のMOSトランジスタと、を備える。

(もっと読む)

増幅器

【課題】単相増幅器において、出力信号に含まれる2次歪み成分を除去する。

【解決手段】増幅器は、第1の導電型の半導体で形成され第1の出力電流ΔI1を出力する第1のMOSトランジスタNM12と、前記第1の導電型の半導体で形成される第2のMOSトランジスタNM13と、第2の導電型の半導体で形成され第2の出力電流ΔI2を出力する第3のMOSトランジスタPM12と、前記第1の出力電流ΔI1と前記第2の出力電流ΔI2との差電流により設定される負荷電流に応じて出力信号ΔIR1を生成する負荷抵抗RL1とを備える。

(もっと読む)

エラーアンプの位相補償回路

【課題】 ICチップ上のコンデンサ面積を小さくすることができる位相補償回路を提供する。

【解決手段】 エラーアンプの出力端子に容量と抵抗を直列接続し、容量に流れる電流を抵抗の両端に接続したトランスコンダクタンスアンプにより増幅してフィードバックすることにより、エラーアンプの周波数特性の主要極の周波数を低くする。

(もっと読む)

電力増幅器及びその製造方法

【課題】低耐圧のトランジスタを用いた高出力の電力増幅器を提供すること。

【解決手段】本発明に係る電力増幅器は、制御端子に第1の入力信号が入力される第1のトランジスタ6と、第1のトランジスタ6と縦列接続され、制御端子に第2の入力信号が入力される第2のトランジスタ10とを備え、第1の入力信号と第2の入力信号とが、同期し、かつ、同位相であるものである。これにより、出力電圧が、最大電圧振幅時に、第1のトランジスタ6と第2のトランジスタ10とに略均等に分割して印加される。

(もっと読む)

可変利得増幅器

【課題】利得を変化させた際の出力インピーダンスの変動を抑える可変利得増幅器を得る。

【解決手段】ゲートバイアスが供給されるゲートが入力端子1と接続され、入力された信号を増幅するソース接地型増幅素子3と、一端からドレインバイアスが印加される複数の並列抵抗63を有するとともに、並列抵抗63の他端間を結ぶ複数の直列抵抗62を有するラダー抵抗回路61と、ゲートバイアスが供給されるゲートが高周波的に接地され、ドレインがラダー抵抗回路61における各並列抵抗の他端と接続され、ソースがソース接地型増幅素子3のドレインと接続され、複数のゲート接地型増幅素子51〜5nと、複数のゲート接地型増幅素子のいずれかのドレインに接続された出力端子12と、複数のゲート接地型増幅素子のゲートと接続され、ゲートバイアスを選択的に供給するゲートバイアス制御回路6とを備える。

(もっと読む)

増幅回路

【課題】出力トランジスタに直列にトランジスタを接続し、このトランジスタに入力信号を入力すると共に、このトランジスタによって出力トランジスタをドライブするカスコード構成の増幅回路では、出力トランジスタのベース電位は固定されていた。このため、電源電圧が高くなると出力トランジスタの消費電力が増大し、その規格を越えてしまうという課題があった。本発明は、電源電圧が高くなっても出力トランジスタの消費電力が増大しない増幅回路を提供することを目的にする。

【解決手段】電源電圧が入力され、この電源電圧に基づいて出力トランジスタのベース電位を決定すると共に、電源電圧の変動に連動して、前記出力トランジスタのベース電位を変化させる電圧帰還回路を具備した。電源電圧が高くなると出力トランジスタのベース電位も高くなるので、出力トランジスタの消費電力を低減することができる。

(もっと読む)

カスコード回路

【課題】RF高効率高出力電力増幅とともに、低ひずみ化の可能性をも併せ持つカスコード回路を提供する。

【解決手段】カスコード回路の両FET(または両バイポーラトランジスタ)の接続部にバイアス電圧を印加することで、ソース接地FETにおけるゲートバイアス電圧(またはエミッタ接地バイポーラトランジスタにおけるベースバイアス電圧)と、RFゲート接地FETにおけるドレーンバイアス電圧(またはベース接地バイポーラトランジスタにおけるコレクタバイアス電圧)とを、独立に設定できる。特に、これらのバイアス電圧を、ソース接地FET(またはエミッタ接地バイポーラトランジスタ)がB級動作ないし深いAB級動作をし、かつ、交流ゲート接地FET(または交流ベース接地バイポーラトランジスタ)が浅いAB級動作ないしA級動作をする組み合わせに設定する。

(もっと読む)

半導体集積回路

【課題】回路設計の余裕を拡大すること。

【解決手段】半導体集積回路100は、トランジスタ124a,124bと、検出回路131と、バイアス生成回路132と、を備えている。トランジスタ124aおよびトランジスタ124bは、基板にバイアスが印加される。検出回路131は、トランジスタ124aおよびトランジスタ124bの閾値電圧を検出する。バイアス生成回路132は、検出回路131による検出結果に基づいてバイアスを生成する。

(もっと読む)

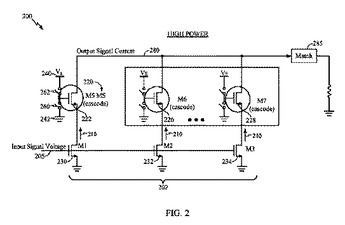

共通のバイアス電流をシェアする複数の増幅ステージを用いて信号を増幅するシステム及び方法

装置は、共通のDC電流によってバイアスされ、入力信号から増幅された出力信号を発生するように適応されたカスケードの増幅ステージを含む。第1の増幅ステージは、入力電圧信号を実質的に2倍にするルーティングネットワークと、入力電圧信号から第1の電流信号を発生する第1の相互コンダクタンスゲインステージとを含む。第2の増幅ステージは、第1の電流信号を第2の電圧信号に変換する共振器と、第1の電流信号から第2の電流信号を発生する第2の相互コンダクタンスステージとを含む。第3の増幅ステージは、第2の電流信号から第3の電流信号を発生する電流ゲインステージと、第3の電流信号が流れて出力信号を発生する負荷とを含む。  (もっと読む)

(もっと読む)

ダイオードベースバイアス有りスタックアンプ(stackedamplifier)

アンプの直線性を改善するための技術が述べられる。典型的な設計では、アンプ(例えば、パワーアンプ)は、スタック内に結合された複数のトランジスタと、少なくとも一つのダイオードを含む。前記複数のトランジスタでは、入力信号を受信して増幅する出力信号を提供する。少なくとも一つのダイオードがスタック内の少なくとも一つのトランジスタに動作可能なように結合される。各ダイオードは、スタック内の関連付けられたトランジスタに可変バイアス電圧を提供する。各ダイオードは、高入力パワーでダイオードの両端で電圧降下を有し、そして、高入力パワーで関連付けられているトランジスタに高バイアス電圧を提供する。少なくとも一つのトランジスタは、少なくとも一つのダイオードから高バイアス電圧に起因する高入力パワーで高ゲインを有する。高ゲインはアンプの直線性を改善する。  (もっと読む)

(もっと読む)

RF駆動増幅器送信機における利得制御の直線性

入力信号電圧を複数の入力信号電流に変換するための複数の電圧−電流トランスデューサとカスコード段とを備える例示的装置が開示される。カスコード段は、増幅器利得制御を実現するように電圧−電流トランスデューサに結合される。カスコード段は、薄ゲート酸化膜トランジスタと厚ゲート酸化膜トランジスタとを備える。  (もっと読む)

(もっと読む)

低雑音増幅器およびミキサ

パワー消費に対して制御可能な線形性および雑音指数を有する低雑音増幅器(LNA)システムが提供される。システムは、調節のために2つの制御入力を備える。一方の入力は、実効トランジスタ幅を制御し、他方の入力は、バイアス電流を制御する。実効トランジスタ幅に対する変化が、信号に与えられる利得を変更し、バイアス電流に対する変化が、システムのパワー消費を変更する。より厳密な信号仕様に関して、LNAのインピーダンス整合した誘導縮退変化が提供される。  (もっと読む)

(もっと読む)

差動増幅回路

【課題】相対精度のばらつきの増加が原因で生じる出力対の2つのトランジスタのオフセット電圧を低減させる。

【解決手段】入力信号INaをゲートに入力する第1のNchトランジスタMN1と、入力信号INbをゲートに入力するNchトランジスタMN2と、NchトランジスタMN1、MN2のソースを接続して電流源となるNchトランジスタMN3と、NchトランジスタMN1のドレインとPchトランジスタMP5のバックゲートとをソースに接続してドレインから出力信号OUTbを出力するPchトランジスタMP4と、NchトランジスタMN2のドレインとPchトランジスタMP4のバックゲートとをソースに接続してドレインから出力信号OUTaを出力するPchトランジスタMP5と、を備える。

(もっと読む)

21 - 40 / 165

[ Back to top ]