Fターム[5J500AA15]の内容

Fターム[5J500AA15]の下位に属するFターム

DEPP、平衡型PP (31)

SEPP (233)

Fターム[5J500AA15]に分類される特許

41 - 60 / 60

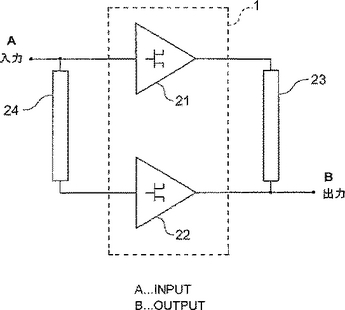

出力バッファ回路及び出力バッファシステム

【課題】出力回路のスイッチング素子の短絡による破壊を確実に防止することが可能な出力バッファ回路及びそれを複数備えた出力バッファシステムを提供する。

【解決手段】第1の上側スイッチング素子4の他方の主端子と第1の下側スイッチング素子5の一方の主端子とを接続する部分が外部への出力部6を構成する第1の出力回路2と、出力端子が第1の出力回路2の出力部6に接続された第2の出力回路22と、第1の出力回路2の出力部6の短絡を検出する短絡検出回路24と、を備え、その起動時に、第1の出力回路2を動作させる前に第2の出力回路22を動作させて短絡検出回路24を動作させ、出力部6の短絡が検出されなかった場合に第1の出力回路2を動作させ、出力部6の短絡が検出された場合には第1の出力回路2を動作させないよう構成されている。

(もっと読む)

D級増幅装置

【課題】 高速且つ均一なスイッチングを実現し、装置の小型化を図ることができるD級増幅装置を提供する。

【解決手段】 トランジスタQ10,Q11のオン/オフによって1次側中点を中心にプッシュプル動作を行うパルストランス24と、それによりスイッチングを行うパワートランジスタQ12,Q13と、プッシュプル動作の時間分、搬送波信号の出力タイミングを調整するタイミング調整手段30と、音声信号が入力されている場合に、タイミング調整手段30からの搬送波信号について逆位相の信号を生成する反転回路35及びAND回路37と、AND回路37から出力された、タイミング調整手段30からの搬送波信号に逆位相の矩形波でオン/オフするトランジスタQ14と、タイミング調整手段30からの搬送波信号に同位相の矩形波でオン/オフするトランジスタQ15とを備える。

(もっと読む)

分布型環状電力増幅器の構造

【課題】増幅されるRF信号の電力出力を効率的及び経済的に増加させる、分布型電力増幅器のトポロジー及びデバイスを提供する。

【解決手段】電力増幅器は、新規の環状で相互に接続された複数のプッシュプル増幅器を具えており、等しい大きさ及び逆相の入力信号で駆動される隣接する増幅デバイスの信号入力を有する能動素子の1次巻線として機能することが好ましい。また、そのトポロジーは、1次巻線の形状に適合する2次巻線150の使用と、個々の電力増幅器の電力を効率的に合成する働きをする変化に適応する変化を開示している。新規の構造は、RF、マイクロ波、ミリ波の周波数で低コストで、高集積で、ハイパワーである増幅器のデザインを可能としている。

(もっと読む)

増幅回路

【課題】複数の増幅部を並列接続して効率よく動作させることが可能な増幅回路を提供する。

【解決手段】同一構成の増幅部AR,ALにおいて、対応する内部ノード(例えば、出力段のトランジスタのゲートが接続される内部ノードpg,ng)間をスイッチ(S2,S3)を介して接続できるように構成する。増幅部AR,ALをステレオ・モードで動作させる時は、スイッチS2,S3をオフに設定する。モノラル・モードで動作させる時は、スイッチS2,S3をオンに設定し、2つの入力端子INR,INLを接続してモノラルのオーディオ信号Aを入力すると共に、2つの出力端子OUTR,OUTLを接続してモノラルのオーディオ出力信号を取り出す。

(もっと読む)

短絡検出回路

【課題】本発明は、コストアップや電力損失を招くことなく、プッシュプル回路の出力短絡を検出することが可能な短絡検出回路を提供することを目的とする。

【解決手段】本発明に係る短絡検出回路は、パルス信号Vxと同期したダミーパルス信号Vyを生成し、両信号間に所定の位相差が生じているか否かに応じて、OUT1P端子の短絡検出を行う構成とされている。

(もっと読む)

アンバランス−バランス変換回路

【課題】 アンバランス−バランス変換回路において、バランス変換された正相のオーディオ信号と逆相のオーディオ信号の相互の品質差をなくし、音質の劣化を防止する。

【解決手段】 アンバランス−バランス変換回路において、オーディオ信号の音量を調節する音量調節回路と、前記音量調節回路によって音量調節されたオーディオ信号を増幅する増幅回路と、前記増幅回路が増幅したオーディオ信号の位相を反転して前記増幅回路に帰還する位相反転回路とを備え、前記増幅回路の出力をオーディオ信号の正相成分として出力し、前記位相反転回路の出力をオーディオ信号の逆相成分として出力する。

(もっと読む)

分布型電力増幅器

【課題】高周波電力増幅器における渦電流損失を、回路占有面積を増大させることなく低減する。

【解決手段】2つのゲインブロック(3aa,3ab−3da,3db)が各々に接続される1次インダクティブパス(2a−2d,4a−4d)および1次インダクティブパスと磁気結合する2次インダクティブパスに屈曲部(5)を設け、この屈曲部が中心を向くように配置する。2次インダクティブパス(4a−4d)を、順次配線(11a−11c)により相互接続し、未接続の2次インダクティブパス端部を出力端(15a、15b)として利用する。

(もっと読む)

増幅回路

【課題】オーディオ等に使用される増幅回路において、貫通電流の発生を抑え、パワーアンプの過熱及び破壊を防止する。

【解決手段】本発明の増幅回路は、パワーアンプ1,過熱検出回路2,信号減衰回路3を備える。パワーアンプ1は、入力アナログ信号を増幅する第1及び第2のパワートランジスタTr1,Tr2を備える。過熱検出回路2は、第1及び第2のパワートランジスタTr1,Tr2の過熱を検出するサーミスタRtを備える。信号減衰回路3は、過熱検出回路2による過熱検出に基づいて、入力アナログ信号を減衰させる。

(もっと読む)

分布型電力増幅器

【課題】分布型環状増幅器の出力波形歪を低減する。

【解決手段】環状に配置されるプッシュプル増幅段(PAS0−PAS3)において、一次側スラブ型トランスとして確保された領域(1a,1b)と交差しないように二次側トランスから出力を取出す。

(もっと読む)

デジタル変調のためのシステム及び方法

【課題】電力増幅及び送信のためのシステム及び方法を提供する。

【解決手段】同じプロセスでベースバンド信号を搬送波周波数の信号にシフトするため、アップコンバータにより中心周波数を変更し合成される電力増幅を可能にするシステム及び方法。そして、デジタルにより実現し、電力効率がよく、線形性問題がほとんど、又は全く無く、シリコンチップ及び広帯域動作に適した技術である。それぞれの入力サンプルは、同じサンプリング間隔内のいくつかのサブサンプルと置き換えられ、サブサンプルの合計の重みは、置換されたサンプルに等しい。このサブサンプルへのプロセスは、サンプリング信号の周波数応答を変え、負荷ドライバの振幅ダイナミックレンジを減少させ、デジタルアナログ変換のためのフィルター要件を簡素化し、負荷ドライバの線形性要件を減少させる。このプロセスは、デジタル回路でもよく、広帯域動作をもたらす。

(もっと読む)

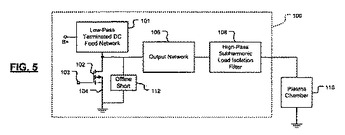

無線周波数電力増幅器安定化回路網

無線周波数(RF)電力をプラズマ室に印加するための無線周波数発生装置はDC電源(B+)を含む。無線周波数スイッチは中心周波数f0の上記RF電力を発生させる。低域通過散逸終端回路網はDC電源(B+)とスイッチとの間に接続され、第一遮断周波数にて作動する。スイッチはシステムの忠実度を向上させる出力回路網へ信号を出力する。出力回路網は所定周波数を超えるRF電力を通過させる高域通過サブ高調波負荷絶縁フィルターへ送られる出力信号を発生させる。低域高調波負荷絶縁フィルターが出力回路網と高域通過サブ高調波負荷絶縁フィルターとの間に挿入されてもよく、高調波終端回路網が出力回路網の出力に接続されてもよい。高域通過終端回路網は所定周波数を超える周波数のRF電力を散逸させる。オフラインショートまたは分路回路網はスイッチの出力と出力回路網の入力とに接続され、所定周波数にてスイッチの出力を短絡させてもよい。  (もっと読む)

(もっと読む)

電圧制御電流源回路

【課題】電圧制御電流源を提供する。

【解決手段】差動電圧生成回路110は入力電圧Vinを差動電圧V1とV2に変換して第1の可変電流源132と第2の可変電流源136にそれぞれ入力する。第1の可変電流源132は、第1の出力端子104と接地電圧の間に接続され、電圧V1に応じて出力電流を可変する。第1の可変電流源132と同じ構成を有する第2の可変電流源136は、第2の出力端子106と接地電圧の間に接続され、電圧V2に応じて出力電流I4を可変する。第1の定電流源122は電源VDDと第1の出力端子104の間に接続され、定電流I1を出力する。第2の定電流源126は電源VDDと第2の出力端子106との間に接続され、定電流I2を出力する。第1の出力端子104から、電流I1と電流I3の差電流を出力し、第2の出力端子106から、電流I2と電流I4の差電流を出力する。

(もっと読む)

高周波電力増幅回路

【課題】パルス動作により間歇的に高周波電力増幅を行う、高周波用のパワーMOS・FETを用いた高周波電力増幅回路において、ゲートパルスによるバイアス電圧の掛け方を工夫することで、パワーMOS・FETの出力パルス幅を拡げて、かつ安全性の高い動作を期待できる、経済的に有利な回路構成とした。

【解決手段】波形成形回路20は、ゲートパルス入力端21に入力されたゲートパルスGP(in)を出力電位が漸減する所定幅のゲートパルスGP(out)に成形して、増幅回路10のパワーMOS・FET12,13のゲート電極(G)に供給する。

(もっと読む)

アンプ装置

【課題】入力信号を受けてスピーカを駆動するアンプ部と、該アンプ部に出力電圧を供給する電源回路部とを備えたアンプ装置において、電源電圧の変動を小さくし、音の立ち上がりの歪みを小さくする。

【解決手段】入力信号を受けてスピーカ23を駆動するアンプ部26と、該アンプ部26に出力電圧を供給する電源回路部25とを備えたアンプ装置であって、前記アンプ部26は、前記入力信号をPWM信号に変換するPWM信号発生回路4と、前記PWM信号の時間差成分に比例する信号を出力するデューティ検出回路8とを備え、前記電源回路部25は、前記デューティ検出回路8からの信号が入力され、この信号に基いて出力電圧を制御するPWM制御回路15を備える。

(もっと読む)

パワーアンプシステム

【課題】パワーアンプシステムにおいて、パワーアンプICがGNDオープン地絡状態に誤接続された状態の場合でも、パワーアンプICの出力信号の音質を損ねることなく、プッシュ側出力トランジスタを破壊しないように確実に保護する。

【解決手段】電源端子11、接地端子12、出力端子13、リップル端子14および制御端子15と、電源端子と接地端子に接続されたパワーアンプ回路16と、出力端子に接続された負電位検出回路17と、制御端子入力と負電位検出回路出力とリップル端子の電位により制御され、バイアス起動信号を制御するバイアス起動回路18と、バイアス起動信号により起動制御され、パワーアンプバイアス電圧出力ノードがリップル端子に接続されたバイアス回路19とを有するパワーアンプIC10と、パワーアンプICのリップル端子に外付け接続されたリップルフィルタ用のコンデンサ23とを具備する。

(もっと読む)

電力増幅器および電力増幅器を動作させる方法

【課題】高増幅率を有する、一般的な電力増幅器を提供すること。

【解決手段】本発明により、高周波電力増幅器は、パワートランジスタがブレークダウン領域において動作されるように接続され、ブレークダウン内で生じる荷電担体を演算増幅器の出力から運び去るために用いられる制御ループが提供されるという点で特徴的である。また、制御ループは少なくとも1つのトランジスタを備える。さらに、制御ループのトランジスタは、パワートランジスタと並列に接続される。さらにまた、制御ループは、荷電担体増倍の時定数よりも大きい時定数を有し、少なくとも1つのダイオード(D1、D2)との組合せによってブレークダウン領域における動作信頼度が向上する。

(もっと読む)

増幅器

常に信号の増幅動作を行うキャリア増幅器と、高電力出力時のみに動作するピーク増幅器と、キャリア増幅器とピーク増幅器の出力を合成して出力する合成器と、入力信号をキャリア増幅器側とピーク増幅器側に分配する分配器とを含んで構成される。キャリア増幅器およびピーク増幅器は1個のパッケージ1(1パッケージトランジスタ)に内蔵される。  (もっと読む)

(もっと読む)

増幅器

【課題】適切な整合を取ることにより従来のドハチィ増幅器以上の性能を得る。

【解決手段】AB級で動作するキャリア増幅回路4と、BまたはC級で動作するピーク増幅回路5と、キャリア増幅回路4からインピーダンス変換器64を経由して増幅回路5の出力を合成する合成点62を有する。伝送線路の長さを0〜λ/2の範囲で最適化して設定する事により、増幅素子52が動作しない時の増幅素子42から見たインピーダンスを、ほぼ最大出力が得られる時のインピーダンスから、任意の値へ遷移させることができる。また、キャリア増幅回路4とピーク増幅回路5のそれぞれをプッシュプル構成にしてもよい。

(もっと読む)

EER変調増幅装置

【課題】 PWM制御により高周波信号の振幅増幅を行うとき、三角波クロック信号の周波数成分によって発生するスプリアスを抑制して高効率な線形増幅を行うこと。

【解決手段】 高周波信号はポーラ変調器2で振幅信号とRF位相変調信号とに分離される。振幅信号は振幅増幅器3aと振幅増幅器3bに入力され、RF位相変調信号は二合成増幅器4に入力される。PWM制御部5aが振幅信号と三角波クロックとによってパルス信号を生成し、パルス増幅部6aがそのパルス信号を増幅して高周波増幅器8aの電源端子へ供給する。PWM制御部5bが振幅信号とPWM制御部5aとは逆位相の三角波クロックとによってパルス信号を生成し、パルス増幅部6bがそのパルス信号を増幅して高周波増幅器8bの電源端子へ供給する。高周波増幅器8a,8bは個別にRF位相変調信号を増幅した後に合成して変調増幅信号を出力する。

(もっと読む)

高出力パワーアンプ

【課題】高出力パワーアンプにおいて、主基板の反りによる放熱悪化により、電流増や高周波特性劣化が発生してしまうことを抑制し、且つ、半導体の特性を最大限に引き出すことを可能とする高出力パワーアンプの提供を課題とする。

【解決手段】本発明の高出力パワーアンプ20は、Push-Pull構成の半導体信号線間に、両面若しくは片面に積層銅張り層21,22が設けられ、且つネジ孔23が設けられた整合用小型基板11が、ネジ12によって主基板4に押し付けられて取り付けられ、これにより、主基板4の反り防止と、半導体直近における整合回路の形成とを両立できる。

(もっと読む)

41 - 60 / 60

[ Back to top ]