Fターム[5J500AA47]の内容

Fターム[5J500AA47]に分類される特許

81 - 100 / 414

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、出力段の貫通電流を抑制可能とした出力回路を提供する。

【解決手段】差動増幅段50、出力増幅段30、増幅加速回路10、容量接続制御回路20を備え、出力増幅段30は出力端子2とトランジスタ101、102を備え、増幅加速回路10は、差動増幅段の第1、第2の出力3、4と出力端子2間に夫々接続されたスイッチSW1とトランジスタ103並びにトランジスタ104とスイッチSW2を備え、容量接続制御回路20は、一端が出力端子に接続された容量素子C1、C2と、C1の他端と第1の電圧供給端子NE1との間に接続されたスイッチSW21と、C1の他端と前記差動増幅段の第1の差動対の出力7の間に接続されたスイッチSW22と、C2の他端と第2の電圧供給端子NE2との間に接続されたスイッチSW23と、C2の他端と差動増幅段の第2の差動対の出力8の間に接続されたスイッチSW24と、を備える。

(もっと読む)

オペアンプ及びこれを用いた液晶駆動装置、並びに、パラメータ設定回路、半導体装置、電源装置

【課題】定常消費電流を大きくせずスルーレートを高速化したオペアンプを提供し、また、外部端子数を増大せず、閾値電圧などのパラメータを任意に設定することが可能なパラメータ設定回路、並びに、これを備えた半導体装置、電源装置を提供する。

【解決手段】オペアンプは、一対のトランジスタから成る差動対を用いて正相入力信号と逆相入力信号との電位差に応じた電圧信号を生成する少なくとも一の差動入力部10、20と、前記差動入力部で生成される前記電圧信号に応じた論理レベルの出力信号を生成して出力する出力部30と、前記正相入力信号または前記逆相入力信号が急峻に変動したことを検出して補助電流Id1、Id2を生成する少なくとも一の補助電流生成部40、50と、所定の基準電流Id0と前記補助電流Id1、Id2とを足し合わせて前記差動入力部の駆動電流Idを生成する駆動電流生成部60と、を有する。

(もっと読む)

演算増幅器、並びに、それを用いた表示パネルドライバ及び表示装置

【課題】出力端子の電位の変動が位相補償キャパシタを介して出力トランジスタのゲートの電位を変動させることによる貫通電流の発生を防ぐ。

【解決手段】演算増幅器1が、出力PMOSトランジスタMP6と、出力NMOSトランジスタMN6と、ノードN1と出力端子Voutの間に接続された位相補償キャパシタC1と、ノードN2と出力端子Voutの間に接続された位相補償キャパシタC2と、浮遊電流源6を構成しているPMOSトランジスタMP5A及びNMOSトランジスタMN5Aと、ノードN1と浮遊電流源6の間に接続されたPMOSトランジスタMP5Bと、浮遊電流源6とノードN2の間に接続されたNMOSトランジスタMN5Bとを備えている。PMOSトランジスタMP5A、MP5Bのゲートは共通に接続され、NMOSトランジスタMN5A、MN5Bのゲートは共通に接続されている。

(もっと読む)

演算増幅器

【課題】全ての位相補償容量に対して充放電の加速電流を供給することでスルーレートを増大させた演算増幅器を提供する。

【解決手段】ゲートが正転入力端子IN+に接続されたトランジスタ11a、ゲートが反転入力端子IN−に接続されたトランジスタ11b、トランジスタ11a,11bのソースに共通接続された電流源CS1、及びトランジスタ11a、11bのドレインに接続された負荷を有する第1の差動回路11と、該第1の差動回路11の正転出力信号を増幅する1又は2段以上縦続接続された増幅器121〜12nと、増幅器121〜12nの入力側と出力端子OUTの間に接続された位相補償容量CC1〜CCnとを備えた演算増幅器において、正転入力端子IN+の電圧が反転入力端子IN-の電圧よりもVdif1より高くなると位相補償容量CC1〜CCnに対し放電電流を追加し、Vdif3より低くなると充電電流を追加する電流制御部13を備えた。

(もっと読む)

差動増幅回路、2段増幅回路およびそれらを用いたA/D変換回路

【課題】2組のプシュプル型CMOS反転増幅器を有する差動増幅回路において、同相入力電圧変動に対する出力動作点の変動を抑制するとともに、電源電圧除去比も高くする。

【解決手段】差動入力端子Vip,Vimに与えられる入力信号が直接または容量を介してゲートに与えられるpMOSトランジスタペア1と、容量C1,C2と、それらを介して入力信号が与えられるnMOSトランジスタペア2と、nMOSトランジスタペア2のゲート・ドレイン間に設けられたスイッチS1,S2と、で構成される2組のプシュプル型CMOS反転増幅器による差動増幅回路において、nMOSトランジスタペア2の共通ソースとGNDの間にゲートが出力端子Vom,Vopに接続されたnMOSトランジスタM5,M6を設ける。

(もっと読む)

半導体集積回路装置及びその温度補正方法

【課題】簡単な構成で基準信号の温度補正を行うことができる半導体集積回路装置及びその温度補正方法を提供することを目的とする。

【解決手段】少なくとも3つの異なる温度で半導体集積回路の信号発生手段21,22の出力する基準信号の値を測定し、測定した基準信号の値を目標値とするため信号発生手段のトリミング手段に与える補正制御データを求め、3つの温度で得た信号発生手段のトリミング手段に与える補正制御データから半導体集積回路の使用温度範囲における各温度の補正制御データを算出し、各温度の補正制御データを温度と対応付けて格納手段56に格納し、半導体集積回路の温度検出手段23で検出した温度に応じて格納手段から信号発生手段のトリミング手段に与える補正制御データを読み出して信号発生手段のトリミング手段に設定し、信号発生手段が出力する基準信号の温度補正を行う。

(もっと読む)

高パワー広帯域増幅器及び方法

【解決手段】実施形態によれば、高い供給電圧源と、低い供給電圧源と、2つの並列信号パスとを具備する増幅器を提供する。それぞれの信号パスは、前記高い供給電圧源及び前記低い供給電圧源に接続され、第1増幅器と第2増幅器とを具備する。前記2つの信号パスは共通の入力ノード及び共通の出力ノードでのみ互いに接続され、その結果前記それぞれの第1増幅器は互いに独立に動作する。前記第1増幅器は、入力電圧信号の少なくとも一部を信号電流へ変換する。複数の前記信号パスは、使用中の前記信号電流がそれぞれの前記第2増幅手段を駆動して増幅された出力電流を前記共通の出力ノードへ提供する。 (もっと読む)

信号処理回路

【課題】歪を抑制しつつ音量感を向上させる。

【解決手段】 入力信号Vinのレベルの絶対値が所定の入力範囲では、小さな利得を付与することにより波形整形した第1信号V1を生成する波形整形部1Aと、第1信号V1を増幅しつつ振幅を調整して出力信号Voutを生成する可変利得部20と、出力信号Voutにクリップが発生しないように可変利得部20の利得を制御する制御回路23とを備え、制御回路23が出力信号Voutにクリップが発生しないように可変利得部20の利得を下げるように制御する第1信号V1の所定範囲は、所定の入力範囲の入力信号Vinのレベルに対応する第1信号V1のレベルの範囲を含む。

(もっと読む)

差動入力段回路、差動入力段回路を備えた演算増幅器及び電圧レギュレータ回路

【課題】出力インピーダンスが大きい信号源を接続した場合でも大きなバイパスコンデンサを必要とせず、かつ電源電圧変動除去特性の良い差動入力段回路を提供する。

【解決手段】差動入力段回路を、差動入力部を構成し、ソースが結合されたトランジスタM1,M2と、トランジスタM1,M2とグランドとの間に接続された定電流源Icと、カレントミラー段を構成し、ソースが電源に接続されたトランジスタM3,M4と、トランジスタM3のドレーンにドレーンが接続され、トランジスタのドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM1と同一の導電型のトランジスタM5と、トランジスタM4のドレーンにドレーンが接続され、トランジスタM2のドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM2と同一の導電型のトランジスタM6と、で構成する。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

オペアンプ回路

【課題】差動入力信号の伝達遅延時間を小さくすることができるオペアンプ回路を提供することである。

【解決手段】本発明にかかるオペアンプ回路10は、第1の差動対を構成するトランジスタ11、12を備える第1の差動入力部1と、第1の差動対を構成するトランジスタ11、12よりもトランジスタサイズが大きい第2の差動対を構成するトランジスタ21、22を備える第2の差動入力部2と、第1および第2の差動入力部1、2からの出力に応じて信号を生成する中間段3と、中間段3で生成された信号に応じて出力信号を生成する出力段トランジスタMP1、MN1を備えた出力段8と、中間段3で生成された信号に応じて、第1の差動入力部1を使用する場合または第1の差動入力部1および第2の差動入力部2を使用する場合のいずれかを選択する差動入力部選択回路と、を有する。

(もっと読む)

出力回路

【課題】構成素子数を最小限に抑えて消費電流の増加を抑え、且つ過渡応答時のクロスオーバー歪を改善する。

【解決手段】NチャネルMOSトランジスタM1,M2,M6と、PチャネルMOSトランジスタM3,M4,M5を備える出力回路において、ドレインとゲートがMOSトランジスタM2のドレインおよびトランジスタM5のゲートに接続され、ソースがMOSトランジスタM4のドレインに接続されたMOSトランジスタM7を設けた。

(もっと読む)

半導体集積回路およびそれを搭載した無線通信端末

【課題】受信回路のチャンネル選択フィルタの信号帯域幅を低い値に設定する際、帰還容量の容量値の増加を軽減して雑音特性の劣化を軽減する。

【解決手段】半導体集積回路は、RF受信信号を受信する受信回路とチャンネル選択フィルタとを具備する。チャンネル選択フィルタは、第1段と第2段のフィルタの従属接続によって構成される。第1段フィルタは、第1段演算増幅器OPA2と、第1入力抵抗R1と、第1帰還容量Cを含む完全積分器によって構成される。第2段フィルタは、第2段演算増幅器OPA1と、第2入力抵抗R1と、第2帰還容量Cと可変帰還抵抗R3との並列接続を含む不完全積分器によって構成される。低カットオフ周波数に設定される際の抵抗値の比(Q=R3/R1)は、高カットオフ周波数に設定される際の抵抗値の比より小さな値に設定される。

(もっと読む)

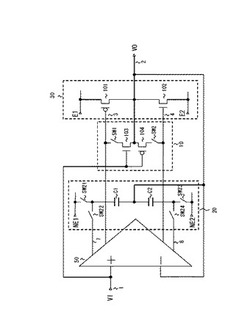

可変利得増幅回路

【課題】入出力範囲を電源電圧まで可能とする。

【解決手段】入力段に第1の演算増幅器51が、出力段に第2の演算増幅器52が、それぞれ配されると共に、第1の演算増幅器51の帰還路に第1のトランスコンダクタンス増幅器53が、第1及び第2の演算増幅器51,52の間に、第2のトランスコンダクタンス増幅器54が、それぞれ配されてなり、第1の演算増幅器51には第1の抵抗器61を介して入力信号を印加可能とし、その第1の抵抗器51に流れる電流と、第1の演算増幅器51の負帰還電流を等しくする一方、第2の演算増幅器52の入出力端子間に第2の抵抗器62を設けると共に、第2の演算増幅器52には、その終段がフルスイング可能に構成されたものを用い、第2の抵抗器62に流れる電流と第2のトランスコンダクタンス増幅器54の出力電流を等しくすることで、入出力範囲が電源電圧まで広げられたものとなっている。

(もっと読む)

可変利得増幅回路、撮像装置

【課題】チップ間の特性ばらつきを抑え、消費電力を低減することが可能な小型の対数増幅回路を提供する。

【解決手段】

増幅器30と、

可変利得増幅回路の入力端子VI(N)と増幅器30の入力端子AMP_IN(N)との間に接続された入力容量3Nと、入力端子AMP_IN(N)と増幅器30の出力端子VO(N)との間に接続された帰還容量2Nとを備え、入力容量3N及び帰還容量2Nは、入力端子AMP_IN(N)と入力端子VI(N)との間に接続された第一の容量(容量73a)と、入力端子AMP_IN(N)と出力端子VO(N)との間に第一の容量に対して並列に接続された第二の容量(72a)と、入力端子VI(N)及び出力端子VO(N)の各々と前記第二の容量との間に設けられ、前記第二の容量と入力端子VI(N)とを接続した状態及び前記第二の容量と出力端子VO(N)とを接続した状態を切り替えるスイッチ(S1)とを含む容量可変用ブロック70aを少なくとも1つ有するラダー容量で構成されている。

(もっと読む)

演算増幅器および演算増幅装置

【課題】低消費電流でかつ十分な位相余裕を有して、高速動作することが可能な演算増幅器を提供する。

【解決手段】演算増幅器に、差動増幅器203の出力電圧に応じた抵抗を有する抵抗用MOSトランジスタ17を設ける。そして、抵抗用MOSトランジスタ17の抵抗値を、制御回路20によって調整する。さらに、制御回路20を、抵抗用MOSトランジスタ17と同じ抵抗値を有する制御用MOSトランジスタ201に接続される反転入力端子と、リファレンス信号が印加される非反転入力端子、抵抗用MOSトランジスタ17のゲート及び制御用MOSトランジスタ201のゲートに接続される出力端子とを有する差動増幅器203、図1のMOSトランジスタ16のトランスコンダクタンス値に比例したトランスコンダクタンス値を有し、差動増幅器203の反転入力端子に出力信号を供給するトランスコンダクタンスアンプ202によって構成する。

(もっと読む)

増幅回路

【課題】利得の変化量を大きくさせ得る増幅回路を提供する。

【解決手段】演算増幅器2の反転入力端子に一端が接続された入力抵抗3と、非反転入力端子に一端が接続され、他端が入力抵抗3の他端に接続された入力抵抗4と、演算増幅器2の反転入力端子と出力端子との間に接続された抵抗5と、演算増幅器2の反転入力端子にドレイン端子が接続され、かつゲート端子およびソース端子がグランド電位GNDに規定されたFET6と、演算増幅器2の非反転入力端子にドレイン端子が接続され、ソース端子がグランド電位GNDに規定されたFET6と同型のFET7とを備え、各入力抵抗3,4が各FET6,7の作動時のドレイン・ソース間の抵抗値RFETよりも大きな抵抗値に規定され、FET7のゲート端子に増幅率制御用の制御電圧Vcが入力される。

(もっと読む)

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

オペアンプ

【課題】入力端子に接続される素子のオフセット電圧を補正することができるオペアンプを提供する。

【解決手段】入力端子を共通に接続したメインアンプとオフセット補正用アンプとを備えたオペアンプであって、メインアンプは、測定用の第1トランスコンダクタンスアンプとオフセット補正用の第2トランスコンダクタンスアンプと第2トランスコンダクタンスアンプの入力端子に接続された第1の容量とを備え、オフセット補正用アンプは、測定用の第3トランスコンダクタンスアンプとオフセット補正用の第4トランスコンダクタンスアンプと第4トランスコンダクタンスアンプの一方の入力端子に接続された第2の容量とを備え、オフセット補正用アンプは第4トランスコンダクタンスアンプの他方の入力端子にオフセット電圧調整回路を設けた。

(もっと読む)

演算増幅器

【課題】応用範囲が広く、かつ、静的なオフセット電圧の補正が可能であり出力電圧の時間変動が小さい演算増幅器を提供する。

【解決手段】演算増幅器1は、差動入力回路3と、電流−電圧変換部5と、オフセット調整回路7とを備える。差動入力回路3は、ソース同士が接続され各ゲートが入力端子となる入力用トランジスタM2,M3を有している。オフセット調整回路7は、ソース同士が接続された調整用トランジスタM5,M6と、調整用トランジスタM5,M6のゲートに接続されたデジタル−アナログ変換部7aとを有する。調整用トランジスタM5と入力用トランジスタM2とはドレイン同士が接続され、調整用トランジスタM6と入力用トランジスタM2とはドレイン同士が接続されている。デジタル−アナログ変換部7aの出力に基づいたオフセット電圧分に対応する電流が調整用トランジスタM5,M6に流れる。これにより、オフセット電圧が調整される。

(もっと読む)

81 - 100 / 414

[ Back to top ]