Fターム[5J500AC54]の内容

Fターム[5J500AC54]に分類される特許

1 - 20 / 146

電力増幅器

【課題】本実施例の一側面における電力増幅器はトランジスタの入力側と出力側の両方に高調波処理を行う整合回路を設けた場合でも発振が生じるのを抑止し、電力増幅器の安定動作を可能とすることを目的とする。

【解決手段】本実施例の一側面における電力増幅器は、基本波と高調波を含む入力信号を入力ノードで受けとり、入力信号の電力を増幅することにより出力信号を生成し、生成された出力信号を出力ノードから出力する増幅回路と、増幅回路の入力ノードに接続され、入力信号の高調波処理を行う入力整合回路と、増幅回路の出力ノードに接続され、出力信号の高調波処理を行う出力整合回路を含む。増幅回路は、入力信号の電力が所定値より大きい値からその所定値より小さい値に低下したとき、生成される出力信号に含まれる高調波の整合点における出力インピーダンスの位相を回転させる。

(もっと読む)

高周波増幅器

【課題】ユニットセルの組み合わせで形成されるすべてのループ発振を抑制することができる高周波増幅器を提供する。

【解決手段】実施の形態に係る高周波増幅器は、入力された信号を分配する分配回路と、分配回路が分配した信号を増幅するFETセルと、分配回路とFETセルのゲート端子との間に直列に接続され、キャパシタと抵抗との並列回路から構成される安定化回路と、FETセルが増幅した信号を合成する合成回路とを備え、安定化回路をFETセルごとに配置する。

(もっと読む)

半導体集積回路、それを備えた受信装置及び無線通信端末

【課題】増幅回路を速やかに正常動作に復帰させることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、容量素子C1T,C1Bを介してそれぞれ供給される第1及び第2電圧信号の電位差を増幅し、第1及び第2増幅信号を出力する全差動増幅回路OPA1と、第1増幅信号を全差動増幅回路OPA1の反転入力端子に帰還する抵抗素子RFBTと、第2増幅信号を全差動増幅回路OPA1の非反転入力端子に帰還する抵抗素子RFBBと、所定電圧VBを生成する電圧生成部50と、電圧生成部50によって生成された所定電圧VBを、全差動増幅回路OPA1のそれぞれの入力端子に伝達する抵抗素子RBT,RBBと、を備える。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

高周波増幅器

【課題】安定化を図りながらソース接地FET素子が本来持つ最大有能利得を十分に生かせる高周波増幅器を提供する。

【解決手段】高周波増幅器は、ソース端子が接地される増幅用ソース接地FET素子と、増幅用FET素子のゲート端子に接続され、増幅用ソース接地FET素子のドレイン端子の印加電圧が増えるに応じてインピーダンスが高くなるように変化する安定化回路と、を備える。安定化回路は、例えば、増幅用ソース接地FET素子のゲート端子に接続するコンデンサと、コンデンサにドレイン端子が接続し、ゲート端子が接地し、ソース端子が増幅用FET素子のドレイン端子に接続するインピーダンス調整用FET素子と、インピーダンス調整用FET素子のソース端子に接続され、接地される抵抗と、この抵抗に接続し、接地されるコンデンサと、を備える。

(もっと読む)

高周波増幅器

【課題】発振抑制が高精度かつ短時間で行える高周波増幅回路を提供すること。

【解決手段】実施形態の高周波増幅器は、複数の領域に区分された増幅素子と、前記増幅素子の区分数の入力整合回路と、前記区分数の出力整合回路と、隣接する前記入力整合回路間を接続する一つ以上の除去可能な抵抗を含む第1の抵抗群と、隣接する前記出力整合回路間を接続する一つ以上の除去可能な抵抗を含む第2の抵抗群と、を有する。

(もっと読む)

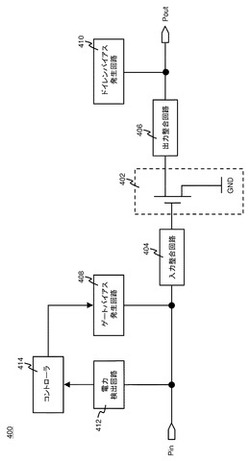

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

半導体電力増幅器

【課題】ビアホールの数を少なくしてもループ発振などの特性劣化が生じにくい半導体電力増幅器を提供する。

【解決手段】半導体電力増幅器は、ゲート電極Gと、ドレイン電極Dと、前記ゲートフィンガー電極に対向して配置されるソースフィンガー電極横手方向の両サイドに引き出される2つのソース電極Sと、を有するユニットFETと、前記ユニットFETが、前記ソース電極間を結ぶ略直線方向に複数個並列配置され、隣り合うユニットFET間に存在する2つのソース電極の両方を共通して高周波グランド面と接続する第1の接地インダクタンス値を有する第1のビアホール18Kと、隣り合うユニットFETが存在しない側のソース電極上に配置され、接地インダクタンスを等しくするために前記高周波グランド面に接続する第2の接地インダクタンス値を有する第2のビアホール18Dと、を有する。

(もっと読む)

トランスインピーダンスアンプ

【課題】利得周波数特性の広帯域化と群遅延平坦特性とを両立させる。

【解決手段】ソース接地トランジスタM1、ゲート接地トランジスタM2、および負荷抵抗RLからカスコード接続回路11を構成し、ソース接地トランジスタM1のドレイン端子とゲート接地トランジスタM2のソース端子と間に第1のインダクタL1を設ける。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

マイクロ波回路

【課題】高利得の増幅器の発振を防止することができるようにする。

【解決手段】キャビティ2,3の外側に配置されており、一方の端子が増幅器5のバイアス端子5cと接続され、他方の端子6aが増幅器4の入力端子4aと同じ側に配置されているローパスフィルタ6と、パッケージ1の接地面1bと接続されている状態で、パッケージ1及びローパスフィルタ6の周囲を覆っている導電性ケース7と、パッケージ1の上面1aに配置され、パッケージ1の接地面1bと電気的に接続されている導電性のキャップ8と、導電性ケース7の上面7aと導電性のキャップ8を接続している導電性の弾性体9とを備える。

(もっと読む)

多段増幅器

【課題】低周波数帯域の利得を効果的に抑圧して発振の発生を抑制すると共に、回路の高密度実装を可能とする多段増幅器を提供する。

【解決手段】FET1,2に、ゲートバイアス電圧を印加する入力整合回路3,5と、FET1,2に、ドレインバイアス電圧を印加する出力整合回路4,6と、出力整合回路4と入力整合回路5との間に直列接続されたコンデンサ15,16、および、一端がコンデンサ15,16間の接続点に接続され他端が接地された誘導性の線路17を含み構成されたハイパスフィルタ18と、を備え、コンデンサ15,16のキャパシタンス値および線路17のインダクタンス値は、増幅素子の動作周波数よりも低い周波数帯域において、出力整合回路6と出力整合回路4とハイパスフィルタ18とを介して形成されるドレインバイアスループ11の損失が、FET2の利得よりも大きくなるように設定する。

(もっと読む)

アンプ回路とそれを備える充電または放電制御回路とその制御方法

【課題】制御開始のタイムラグを低減したアンプ回路とそれを備える充電または放電制御回路とその制御方法とを提供することを目的とする。

【解決手段】誤差アンプと、誤差アンプの出力にベースが接続されたトランジスタと、トランジスタのコレクタとエミッタとの間に接続された負荷と、誤差アンプの出力と誤差アンプのマイナス側入力との間に接続された位相補償コンデンサと、を備えるアンプ回路において、位相補償コンデンサと直列に接続されたフォトモススイッチを備え、フォトモススイッチは、トランジスタのベース電流の有無に対応してオン・オフが制御されるアンプ回路とする。

(もっと読む)

ボルテージレギュレータ

【課題】正確な出力電圧を得る事ができる位相補償回路を有するボルテージレギュレータを提供する。

【解決手段】位相補償回路を出力トランジスタのゲートに接続される第一の定電流回路と、ドレインが出力トランジスタのゲートに接続された第一のトランジスタと、ドレインが第一のトランジスタのゲート及び第二の定電流回路及び抵抗に接続され、ゲートが抵抗及び第一の容量に接続される第二のトランジスタと、もう一方が出力端子に接続される第一の容量で構成する。こうすることで、差動増幅回路の出力端子から第一のトランジスタのドレインへ電流が流れる事を防止することができ、差動増幅回路の入力トランジスタに発生するオフセット電圧が低減され、正確な出力電圧を得ることできる。

(もっと読む)

電力増幅器

【課題】チップサイズを増加させることなく、使用する経路に応じてフィードバック経路の接続・未接続を切替えることができる電力増幅器を得る。

【解決手段】スイッチSW1は、制御信号に従って入力端子Tin1を出力端子Tout1と出力端子Tout2の何れかに接続する1入力多出力のスイッチである。スイッチSW1の入力端子Tin1は、トランジスタTr1のコレクタ(出力端子)に接続されている。フィードバック経路12は、スイッチSW1の出力端子Tour1をトランジスタTr1のベース(入力端子)に接続させる。

(もっと読む)

高周波処理回路

【課題】発振抑制用の抵抗を備えながら高周波処理による高効率化を図る。

【解決手段】分配された高周波信号を伝送線路14a,14bの一端の入力部13a,13bに供給し、伝送線路14aは直列接続された伝送線路15aを介して被増幅用高周波信号として出力部16aから次段の増幅用トランジスタに供給する。伝送線路14bは直列接続された伝送線路15bを介して被増幅用高周波信号として出力部16bから次段の増幅用トランジスタに供給する。伝送線路14a,15aの接続点Paに一端を接続したスタブ19aと伝送線路14b,15bの接続点Pbに一端を接続したスタブ19bとの間に発振抑制用の抵抗R1を介挿接続した。接続点Pa,Pbの電位差がない場合は、抵抗R1が見えない状態となり、スタブ19a,19bは高周波信号処理の効率化に寄与し、抵抗R1はセルA,B間のループ発振の抑制させることが可能となる。

(もっと読む)

連続時間回路のためのオフセットキャンセレーション

【課題】高速シリアルインターフェイスおよび他の用途のために等化器および他の連続時間回路を改善すること。

【解決手段】マルチステージ増幅器チェーンであって、該マルチステージ増幅器チェーンは、該チェーン内に第1の増幅器ステージと最後の増幅器ステージとを含む、マルチステージ増幅器チェーンと、該最後の増幅器ステージの出力を受信することと、オフセット補正電圧信号を該第1の増幅器ステージに提供することとを行うように構成されているオフセットキャンセレーションループとを備えている、回路。

(もっと読む)

高周波回路

【課題】最小ループと2セルループのオッドモード発振を共に抑制する高周波回路を提供する。

【解決手段】半導体基板上に並列に配列された複数のトランジスタと、第1の絶縁基板上に配置され、複数のトランジスタのゲート端子電極にそれぞれ接続された複数の入力整合回路と、第1の絶縁基板上に配置され、入力整合回路に隣接して配置された入力側第4発振抑制抵抗と、入力側第4発振抑制抵抗に直列接続された入力側第1キャパシタと、隣接する入力整合回路間を繋ぐ伝送線路上の点と入力側第1キャパシタ間に接続された入力側第1インダクタとを有する入力側発振抑制回路とを備え、入力側第1インダクタのインダクタンス値をL1、入力側第1キャパシタのキャパシタンス値をC1とすると、1/{2π(L1×C1)1/2}で表される入力側第1インダクタと入力側第1キャパシタの共振周波数が、2セルループの発振周波数fosc2に等しい高周波回路。

(もっと読む)

1 - 20 / 146

[ Back to top ]