Fターム[5J500AF16]の内容

Fターム[5J500AF16]に分類される特許

21 - 40 / 331

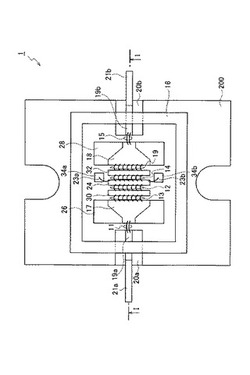

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

高周波増幅器

【課題】熱抵抗が下がり高周波増幅器全体の放熱性能が向上する高周波増幅器を提供する。

【解決手段】高周波増幅器10は、複数のトランジスタセル1a−1gで構成され、平面上に配置されている複数のトランジスタセル1a−1gのうち隣接している2つの各トランジスタセルにおけるx軸方向の各中心はy軸方向にずれている。

(もっと読む)

電力増幅器

【課題】MMICとMMIC外部回路とを接続するボンディングワイヤの影響を比較的簡単な構成で低減し、かつ省スペース化された電力増幅器を提供する。

【解決手段】MMIC基板と、MMIC基板上に配置された高周波プローブパッドと、MMIC基板上に高周波プローブパッドに隣接して配置され、MMIC外部回路とのボンディングワイヤ接続用のメタルプレートとを備える。

(もっと読む)

トランスリニア回路

【課題】CMOSプロセスで製造される半導体装置においてトランスリニア回路を実現する。

【解決手段】トランスリニアループを形成するnpnトランジスタQ1〜Q4は、n型基板を共通のコレクタとする一方、それぞれに対応して形成されたpウェルをベースとし、nMOSのソース、ドレインと同様にpウェル内に形成されるn型領域をエミッタとする。入力トランジスタQ1〜Q3への入力電流の供給はエミッタに接続された電流源I1〜I3により行う。出力トランジスタQ4のエミッタにトランジスタM1を接続する。Q2,Q4のエミッタ間は、演算増幅器210により仮想短絡する。演算増幅器210の出力端子はM1のゲートに接続する。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に含まれる増幅回路における入出力特性の線形性が劣化するのを抑えるとともに、増幅器自体における入出力特性の線形性が劣化するのを抑えることができる半導体装置を提供する。

【解決手段】本発明は、外部と接続する複数の端子を有する配線基板72に、半導体チップ71を実装してパッケージングしてある半導体装置である。半導体装置は、半導体チップ上に形成してある、少なくとも一つの差動増幅器61と、平衡信号線路を差動増幅器61と接続し、半導体チップ71上に形成してある、少なくとも一つのバラン62とを備える。差動増幅器61の接地配線と、バラン62の接地配線とは、半導体チップ71上に分離して形成してあり、差動増幅器61の一つの接地配線と配線基板72とを接続するボンディングワイヤ77の数が、バラン62の一つの接地配線と配線基板72とを接続するボンディングワイヤの77数より多い。

(もっと読む)

マイクロ波回路

【課題】高利得の増幅器の発振を防止することができるようにする。

【解決手段】キャビティ2,3の外側に配置されており、一方の端子が増幅器5のバイアス端子5cと接続され、他方の端子6aが増幅器4の入力端子4aと同じ側に配置されているローパスフィルタ6と、パッケージ1の接地面1bと接続されている状態で、パッケージ1及びローパスフィルタ6の周囲を覆っている導電性ケース7と、パッケージ1の上面1aに配置され、パッケージ1の接地面1bと電気的に接続されている導電性のキャップ8と、導電性ケース7の上面7aと導電性のキャップ8を接続している導電性の弾性体9とを備える。

(もっと読む)

チャージアンプ

【課題】帰還抵抗の寄生容量による悪影響をなくして、半導体基板上で実用化が可能な、出力ノイズの小さいチャージアンプを提供する。

【課題の解決手段】チャージアンプ1は、非反転入力端子を増幅基準電圧6に接続し、反転入力端子に水晶振動子を有する振動型角速度センサ7から50KHzの周波数信号を入力するとともに、その出力端子は並列接続された帰還抵抗4,5及び帰還容量3を介して反転入力端子に接続したものであって、帰還抵抗4,5の反転入力端子側ほぼ半分に対応する寄生容量8の基板電極を反転入力端子に接続して、出力ノイズを低減したものである。

(もっと読む)

スピーカ接続検出機能付増幅器

【課題】多数の各種のスピーカが増幅器に接続する時でも、1つの検出素子により、ほぼ同時に、小電流を流すのみで、また回路に抵抗を設ける必要もなく、容易に、且つ正確にスピーカの接続検出を行うことができる「スピーカ接続検出機能付増幅器」とする。

【解決手段】複数のスピーカ毎のオーディオ信号入力ラインにテスト信号を入力する。スピーカ毎の出力ブロックからの出力ラインの内、プラス側配線またはマイナス側配線を集中させると共に、他の配線は電流による磁気の影響を与えない位置にずらして配置し、集中させて配置した配線部分において、各配線の電流による磁気を検出する位置に磁気センサを設け、テスト信号が流れる各配線の電流による磁気を検出する。接続判定部では、検出した磁気信号を電流に変換した電流値と、予め設定した上限と下限の閾値とを比較し、その範囲内にない時には接続不良、または短絡と判定する。

(もっと読む)

2段のマイクロ波のE級電力増幅器

【課題】より広い周波数範囲で同時的な高電力と高電力付加効率(PAE)をもたらす改良されたE級増幅器を提供する。

【解決手段】2段のE級の高電力増幅器100は駆動装置段102、E級段間整合ネットワーク(ISMN)104、負荷回路を使用する高電力段106を含んでいる。負荷回路はスイッチングモード回路の出力に結合されている直列の誘導性−容量性ネットワークと、スイッチングモード回路の出力に結合されているキャパシタンスを提供するための回路を含んでいる。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

高周波半導体モジュール

【課題】段間の整合状態を観測して整合回路の調整を行うことのできる高周波半導体モジュールを提供する。

【解決手段】複数の半導体増幅素子7、8を直列に接続して増幅を行う多段型の高周波半導体モジュールであって、パッケージ3内に配置される回路基板4、5,6に、半導体増幅素子7、8間の段間における高周波信号をモニタするためのモニタ回路を具備する。

(もっと読む)

光受信モジュールおよび光受信モジュールの製造方法

【課題】光受信モジュールにおいて、同一設計の受光素子を用いながら入力インピーダンスの異なるプリアンプを用いた場合にでも良好な周波数通過特性(S21)を実現する。

【解決手段】受光素子を搭載した半導体チップ6と、受光素子の出力信号を増幅するプリアンプ2と、受光素子を搭載する絶縁性キャリア基板3と、受光素子の出力信号がキャリア基板上の電極5を介してプリアンプに入力されるように接続し、受光素子を搭載しない状態でキャリア基板上の2電極間の容量値を40fF以上とした2電極4、5を有することより解決できる。

(もっと読む)

電力増幅器

【課題】 段間に減衰器を設けた構成において、利得切換前後での入力反射損失の劣化を抑制しつつ利得を切り換えることができる電力増幅器を提供する。また、段間に減衰器を設けた構成において、利得切換前後での通過位相差の増大を抑制しつつ利得を切り換えることができる電力増幅器を提供する。

【解決手段】 IN、OUTはRF入力・出力端子であり、Tr1、Tr2はHBT(ヘテロ接合バイポーラトランジスタ)である。Fa1、Fa2はFET(電界効果トランジスタ)である。Cc1、Cc2はデカップリング容量であり、Vc1、Vc2はパワー段Tr1、Tr2のコレクタ電源端子であり、Ra1、Ra2、Raa2、Rg1、Rg2は抵抗であり、Cs1は段間整合容量であり、Cp1は減衰器の並列容量であり、Vg1、Vg2は減衰器の制御端子である。抵抗Ra1に直列に容量Ca1が設けられている。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

高周波電力増幅装置

【課題】トークカレントの低減を実現可能な高周波電力増幅装置を提供する。

【解決手段】例えば、出力レベルに応じていずれか一方が活性化されるパワーアンプ回路PA2m,PA2sと、伝送線路LNmn,LNsubを備え、LNmn,LNsubが互いに近接配置された領域を持つ。LNsubの他端(PA2sの出力ノード)は、PA2sが活性化された際、NMOSトランジスタMNswのオンに伴い接地電源電圧GNDとの間に容量C3が接続され、PA2mが活性化された際、MNswのオフに伴い開放状態とされる。PA2sが活性化された際、LNmnとLNsubには同一方向の電流が流れるため、強め合う磁気結合が生じる。一方、PA2mが活性化された際、LNmnに流れる電流と、MNswのオフ容量に伴いLNsubに洩れる電流とは反対方向となり、LNmnとLNsubには弱め合う磁気結合が生じる。

(もっと読む)

音声増幅回路およびそれを具備する撮像装置または撮像装置の周辺機器

【課題】MIC増幅回路における雑音と歪とを低減する。

【課題を解決するための手段】基板実装型MICコネクタを実装した第一の基板に、電源重畳回路と信号入力結合回路と入力音声増幅回路とを、表面実装部品の第一の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記信号入力結合回路は、前記第一の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記第一の基板と接続された第二の基板に電源発生部と平衡出力音声増幅回路とを第二の演算増幅器とアナログスイッチICと金属皮膜抵抗と容量として実装し、前記第二の演算増幅器の正入力と接地間の抵抗と正入力と低電圧電源間の抵抗とが設置され、前記平衡出力音声増幅回路の共通帰還回路がタンタル電解コンデンサの逆極性の直列接続または低歪率セラミックコンデンサで容量結合されたことを特徴とする音声増幅回路。

(もっと読む)

整合回路及びこれを備えた電力増幅回路

【課題】小型化を図ることができる整合回路を提供する。

【解決手段】半導体装置1のインピーダンス整合を取るための整合回路であって、半導体装置1上に設けられた第1のボンディングパッド1A及び第2のボンディングパッド1Bと、半導体装置1の外部に設けられた外部電極1と、第1のボンディングパッド1Aと外部電極2とを接続する第1のワイヤ4Aと、第2のボンディングパッド1Bと外部電極2とを接続する第2のワイヤ4Bとによって形成されるインダクタを少なくとも1つ備える整合回路。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

21 - 40 / 331

[ Back to top ]