Fターム[5J500AF16]の内容

Fターム[5J500AF16]に分類される特許

41 - 60 / 331

電子回路

【課題】分布定数線路の長さの誤差または製造ばらつき等による特性変動を抑制すること。

【解決手段】制御端子と、第1端子と、第2端子と、を有する第1トランジスタT1と、制御端子に前記第1トランジスタの第2端子が接続し、第2端子に直流電源が接続される第2トランジスタT2と、前記第2トランジスタの第1端子から前記第1トランジスタの第2端子に直流電流を供給する、互いに独立した配線からなる複数の直流経路11、12と、前記複数の直流経路内にそれぞれ直列に設けられた分布定数線路L11、L12と、を具備する電子回路。

(もっと読む)

増幅器及び通信装置

【課題】増幅する信号が高周波数帯の信号であっても高効率動作が可能な増幅器を得る。

【解決手段】ドハティ増幅器5は、入力端子10と出力端子11間に2つの並列回路を有し、一方には第1のトランジスタ120を有するキャリア増幅器12、及び入力信号の略4分の1波長の電気長を有する導体線路14が直列に設けられ、他方には導体線路14の位相差に相当する電気長の導体線路15、及び第2のトランジスタ130を有するピーク増幅器13が設けられ、キャリア増幅器12とピーク増幅器13は、出力部124と出力部134が対向するよう配置され、トランジスタ120とトランジスタ130は、伝送する信号の出力方向ベクトルが180degとなるように配置されている。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

半導体集積回路装置

【課題】バイアス電流を配給する際のノイズ耐性を大幅に向上させる。

【解決手段】基準バイアス電流回路11は、基準バイアス電流Ipと該基準バイアス電流Ipと電流の極性が逆となる基準バイアス電流Inとを生成し、2本の配線を1ペアとしたバイアス電流用配線H1を介してバイアス電流回路2aに供給する。ペアの配線のうち、一方の配線は他方の線の近傍に平行してレイアウトされており、これら配線の配線長が略同じとしている。バイアス電流回路2aでは、基準バイアス電流Ipを反転させ、基準バイアス電流Inに加算した後、必要なバイアス電流となるように調整し、バイアス電流を生成する。

(もっと読む)

トランスインピーダンスアンプおよびトランスインピーダンスアンプ接続回路

【課題】群遅延特性の入力光パワー依存性を低減し、かつ、ESD耐性を有するトランスインピーダンスアンプを提供する。

【解決手段】入力端子から入力される入力電流のインピーダンス変換を行うトランスインピーダンスアンプTIAとして第一の電源端子VCCTIAと第二の電源端子VEETIAとを有し、第一の電源端子VCCTIAには第二の電源端子VEETIAよりも高い電圧が印加され、かつ、第一の電源端子VCCTIAと第二の電源端子VEETIAとの間に、トランスインピーダンスアンプTIAと並列の電流パスを形成する第一の回路素子が接続されている。該第一の回路素子は、第一のダイオードもしくはダイオード列からなっている。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器と方向性結合器を多層基板内に一体化した高周波モジュールであって、小型、低コスト、高性能な高周波モジュール及び、高周波モジュールを搭載することで、小型化、低コスト化が可能な無線装置を提供する。

【解決手段】多層基板と前記多層基板の上層部で構成された高周波電力増幅器と前記多層基板の内層の上下2層を用いた方向性結合器と、前記高周波電力増幅器と前記方向性結合器の間にある内層のグランドパターンと、前記内層のグランドパターンと裏面のグランドパターン間に設けられている前記高周波電力増幅器用の多数のサーマルビアが方向性結合器と同じ層にある前記高周波電力増幅器用のバイアスラインとの間に設けられている高周波モジュールとする。このことによって小型、低コスト、高性能な高周波モジュールが実現出来る。

(もっと読む)

寄生振動を低減したトランジスタ増幅器

【課題】寄生振動、すなわちパラメータ発振を低減したトランジスタ増幅器を提供する。

【解決手段】複数のトランジスタセル15”を有するトランジスタデバイス12”は複数のフィルタ18”が設けられる。フィルタのそれぞれ1つは、入力ノード20”と、複数のトランジスタセルの制御電極17のうちの対応する1つとの間に結合されている。半導体によって、複数のトランジスタセルの共通活性領域が提供される。フィルタのそれぞれ1つは、導電層と、導電層上に配置された誘電層と、誘電層の上に配置された抵抗層と、抵抗層の第1の部分に電気的に接触するように配置され入力ノードを提供する導電電極と、抵抗層の第1の部分から離れた抵抗層の第2の部分と電気的に接触するコネクタであって、誘電体を通り第1の導体と電気的に接触するコネクタとを含む。

(もっと読む)

定電流回路

【課題】面積の小さい定電流回路を提供する。

【解決手段】高い抵抗値の抵抗によらず、強反転領域・非飽和領域で動作するNMOSトランジスタ23の高い抵抗値のオン抵抗により、定電流回路の定電流I1が少なくなる。よって、NMOSトランジスタ23の面積はこのトランジスタのオン抵抗の抵抗値と同じ抵抗値の抵抗の面積よりも小さいので、定電流回路の面積が小さくなる。

(もっと読む)

カレントミラー回路、電流生成回路及び発光装置

【課題】負荷に供給する電流を精度よく出力する。

【解決手段】ゲート電極とドレイン電極が短絡されている第1トランジスタTr1と、第1トランジスタTr1のゲート電極に、ゲート電極が接続された第2トランジスタTr2と、を備えるカレントミラー回路10において、第1トランジスタTr1と第2トランジスタTr2は、絶縁膜12を介してゲート電極1の上部に設けられてチャネル領域が形成される半導体膜2と、半導体膜2上のチャネル領域を覆う領域に設けられる保護膜3と、半導体膜2のチャネル領域を挟む一対の端部に離間して設けられるとともに保護膜3の一部に重なって設けられソース電極6及びドレイン電極7とをそれぞれ有するとともに、少なくとも第2トランジスタTr2は、ソース電極6の保護膜3に対するチャネル長方向への重なり長がドレイン電極7の保護膜3に対する重なり長より長い構造を有する。

(もっと読む)

電力増幅器

【課題】チップ面積やコストを増加させることなく、リーク電流を抑制することができる電力増幅器を得る。

【解決手段】バイアス回路B1,B2は、リファレンス電圧発生回路VGから供給されたリファレンス電圧に基づいてバイアス電圧を生成し、増幅トランジスタA1,A2にバイアス電圧を供給する。インバータINVは、イネーブル電圧を昇圧して出力する。リファレンス電圧発生回路VGは、インバータINVの出力電圧に応じてON又はOFFする。インバータINVは、イネーブル端子Venと、電源端子Vcbと、トランジスタTri1と、FET抵抗Fdi2とを有する。トランジスタTri1のベースはイネーブル端子Venに接続され、コレクタは電源端子Vcbに接続され、エミッタは接地されている。FET抵抗Fdi2はトランジスタTri1のコレクタと電源端子Vcbとの間に接続され、FET抵抗Fdi2のゲート電極はオープンである。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

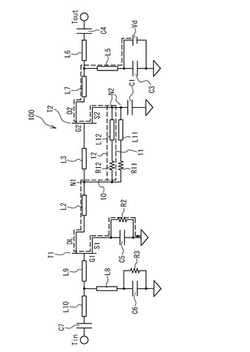

音声切換出力装置

【課題】 BTL方式を使用して音声信号を出力するか否かを切換可能であり、かつ、コモンモードチョークコイルを備える場合に、信号経路ではないコモンモードチョークコイルが音声信号に悪影響を与えることを防止すること。

【解決手段】 BTL方式を使用しない場合、スイッチSW1、スイッチSW2をオン状態に制御し、スイッチSW3、スイッチSW4をオフ状態に制御する。従って、音声信号の電流がコモンモードチョークコイルL3に流れることがなく、音声信号に歪みが生じることが防止される。BTL方式を使用する場合、スイッチSW1、スイッチSW2をオフ状態に制御し、スイッチSW3、スイッチSW4をオン状態に制御する。従って、音声信号の電流がコモンモードチョークコイルL4、L5に流れることがなく、音声信号に歪みが生じることが防止される。

(もっと読む)

安定化回路網を有する電力増幅器

【課題】出力トランジスタの出力キャパシタンスと、電源供給インダクタンスによって増幅器の電源装置端子に現れる高Q値の直列共振を防止した高周波電力増幅器を提供する。

【解決手段】電位不安定の原因を生み出し増幅器が振動する(oscillate)のを防止するために、安定化回路530が、電力増幅器トランジスタ502の出力に接続される。この安定化回路530は、基本的に、コンデンサ534と直列に接続された抵抗器536を含む。また、この安定化回路は、コンデンサと抵抗器とに直列に接続されたインダクタ532を含んでもよい。このインダクタは、プリント導電線及び/又はボンディング・ワイヤによって部分的に、又は完全に実現されることができる。この安定化回路は、動作周波数の範囲全体にわたって、トランジスタ出力において低インピーダンスをもたらす。

(もっと読む)

CMOSオペアンプ、センサ装置

【課題】信号の信号レベルを増幅するに際し、十分な利得を得ながら、サーマルノイズとフリッカノイズとの両者を同時に低減することができるCMOSオペアンプ、及びセンサ装置を提供することを目的とする。

【解決手段】第1MOSFETQ1及びQ2が配置されており、互いに信号レベルが異なる2種類の信号の入力を受け付ける信号入力部10と、第2MOSFETQ4〜Q11が配置されており、信号入力部10により受け付けられた2種類の信号の差分を増幅して出力する信号出力部11と、を備える。第1MOSFETQ1及びQ2のゲート酸化膜の厚さは、第2MOSFETQ4〜Q11のゲート酸化膜の厚さよりも小さく、第2MOSFETQ4〜Q11のゲート酸化膜の厚さは、基準厚さを超える厚さとされており、基準厚さは、第2MOSFETQ4〜Q11が予め設定された利得を得ることができる基準電圧値のゲート電圧に耐える厚さとされている。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電力合成分配器および電力合成分配器を用いた送信機

【課題】複数の増幅器のうちの一部が故障しても、電力合成分配器の分配損、合成損を最小とする。

【解決手段】複数の並列接続された第1の分岐側端子(113、114)と1つの第1の合成側端子(115)が第1の電力合成点(116)を介して接続された第1の分岐回路(127)と、複数の並列接続された第2の分岐側端子(133、134)と1つの第2の合成側端子(135)が第2の電力合成点(136)を介して接続された第2の分岐回路(137)とを有し、第1の合成側端子と複数の第2の分岐側端子が接続された電力合成あるいは電力分配を行う電力合成分配器において、第1の電力合成点から第2の電力合成点までの長さが1/2波長の整数倍である。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

シングルサプライD級アンプ

積層二重インダクタ構造

41 - 60 / 331

[ Back to top ]