Fターム[5J500AF16]の内容

Fターム[5J500AF16]に分類される特許

81 - 100 / 331

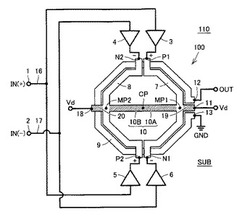

電力増幅装置

【課題】トランスを用いて複数の増幅器対の出力を合成する電力増幅装置において、各増幅器対の差動動作のずれによって生じる出力の低下を抑制する。

【解決手段】電力増幅装置110は、基板上に全体で環状に設けられた複数の一次インダクタ7,8と、複数の増幅器対3〜6と、二次インダクタ9と、接続配線10とを備える。各増幅器対は、対応の一次インダクタの両端に接続され、差動入力信号として与えられた一対の第1および第2の信号IN(+),IN(−)をそれぞれ増幅して対応の一次インダクタに出力する。二次インダクタ9は、複数の一次インダクタ7,8に隣接して環状に設けられ、各一次インダクタで合成された第1および第2の信号の合成信号をさらに合成して出力する。接続配線10は、基板上で複数の一次インダクタ7,8の内側に設けられ、各一次インダクタの中点MP1,MP2を互いに電気的に接続する。

(もっと読む)

カレントミラー回路

【課題】低電圧での動作を可能とし、アーリー効果による電流比の悪化を抑圧可能とする。

【解決手段】

NPN型の第1及び第2のトランジスタ1,2のベース、第1のトランジスタ1のコレクタ、及び、デプレッション型のNチャンネルMOSトランジスタである第3のトランジスタ3のゲートが相互に接続されると共に、定電流源4に接続される一方、第1及び第2のトランジスタ1,2のエミッタは、共にグランドに接続され、第2のトランジスタ2のコレクタは、第3のトランジスタ3のソースに接続されて、この第3のトランジスタ3のドレインに出力可能に構成されてなり、低電圧での動作を可能とし、アーリー効果による電流比の悪化が抑圧可能となっている。

(もっと読む)

高周波増幅器

【課題】回路面積を増加させることなく、動作状態のトランジスタからの発熱を抑制することによって、小型化及び低コスト化を図ることができる高周波増幅器を提供する。

【解決手段】複数の単位トランジスタ3が並列に接続されたトランジスタ列からなり、高周波を増幅する増幅素子と、トランジスタ列の隣り合った単位トランジスタ3のフィンガ間にそれぞれ形成された出力整合回路の回路素子2とを備える。

(もっと読む)

高周波電力増幅器

【課題】マルチバンド、かつ各バンドにおいてマルチモードで動作するアイソレーションの高い高周波電力増幅器を提供する。

【解決手段】本発明に係る高周波電力増幅器は、第1周波数帯域内の第1高周波信号を線形動作により増幅する電力増幅器AMP1と、第1周波数帯域よりも低い第2周波数帯域内の第2高周波信号を線形動作により増幅する電力増幅器AMP2と、第1周波数帯域内の第3高周波信号を非線形動作により増幅する電力増幅器AMP3と、第2周波数帯域内の第4高周波信号を非線形動作により増幅する電力増幅器AMP4とを有し、電力増幅器AMP1〜AMP4の入力配線は、半導体基板120及び130において互いに交差せず、電力増幅器AMP1〜AMP4の出力配線は、半導体基板120及び130において互いに交差しない。

(もっと読む)

高周波電力増幅器

【課題】マルチバンド、かつ各バンドにおいてマルチモードで動作するアイソレーションの高い高周波電力増幅器を提供する。

【解決手段】本発明に係る高周波電力増幅器は、第1電力増幅回路1と、第2電力増幅回路2と、第3電力増幅回路3と、第4電力増幅回路4とを有し、第1〜第4電力増幅回路1〜4は、それぞれ半導体基板に形成されたワイヤーボンディング用の入力パッド101〜104と、入力配線L11〜L14と、電力増幅器AMP1〜AMP4と、出力配線L21〜L24と、出力パッド111〜114とを有し、入力配線L11〜L14は、チップ200および201において互いに交差せず、電力増幅器AMP1〜AMP4の出力配線L21〜L24は、チップ200および201において互いに交差しない。

(もっと読む)

高周波電力増幅器

【課題】高周波電力増幅器の入力端子と増幅回路の入力端子の間で発生するループ発振を抑止することができる高周波電力増幅器を提供する

【解決手段】入力端子20と入力端子20により入力された入力信号を分配する複数の分岐端子21〜24を有する導体パターン19を備える分配回路基板4と、各分岐端子からの入力信号をそれぞれ増幅する増幅回路基板5と、増幅回路基板5からの入力信号を合成する合成回路基板6と、を備え、分配回路基板4の導体パターン19は、絶縁基板に形成された第1導電層19Aと、第1導電層19A上に形成された第2導電層19Bと、第2導電層19B上に形成された第3導電層19Cを有し、分配回路基板の導体パターン19には、入力端子20から分岐端子21〜24が分岐された位置に、第1導電層19Aと第2導電層19Bのみからなる抵抗パターン部41〜44が形成されている。

(もっと読む)

デュアルRFチャンネル用リニアライザ・チャンネル増幅器装置及びその装置を備える通信衛星

通信衛星上に設置されるように設計されたデュアルRFチャンネル用リニアライザ・チャンネル増幅器装置は、各々が無線周波数信号通信チャネルに対応し、かつ、チャンネル増幅器モジュール(10、20)を備える2つの独立した無線周波数チャンネル(RF1、RF2)を備え、2つの無線周波数チャンネル(RF1、RF2)は、2つのチャンネル増幅器モジュール(10、20)の各々専用の遠隔制御信号をルーティングしかつ管理し、かつ、2つのチャンネル増幅器モジュール(10、20)により生成された遠隔測定結果を管理するように設計されたまったく同一の遠隔制御遠隔測定モジュール(30)に接続される。顕著に衛星通信の分野、及び、特に、衛星中継器の無線周波数伝送システムに適用される。 (もっと読む)

広帯域増幅器

【課題】広帯域にわたって良好なインピーダンス整合を与えることができ、高調波処理を高い効率で可能とする広帯域増幅器を得る。

【解決手段】高周波信号を増幅するトランジスタ1と、トランジスタ1の出力端子に一端が直列接続された直列インダクタ6と、直列インダクタ6の他端に一端が並列接続されたショートスタブ2と、ショートスタブ2の他端を高周波短絡するためのキャパシタ3と、直列インダクタ6の他端に一端が並列接続されたオープンスタブ7と、ショートスタブ2の一端及びオープンスタブ7の一端の接続点に一端が接続されたインピーダンス変成器4とを備え、インピーダンス変成器4は、使用周波数の1/4波長の長さの線路であり、トランジスタ1の効率最適負荷インピーダンスは、50Ωより低く、容量性の領域にあり、前記接続点とインピーダンス変成器4の間のインピーダンスは、効率最適負荷インピーダンスと50Ωの間である。

(もっと読む)

高周波電力増幅装置

【課題】高周波電力増幅装置を小型化すること。

【解決手段】増幅回路11、温度補償用回路13、出力検波回路12をパッケージ内に有する高周波電力増幅装置であって、増幅回路11の入力端子19はパッケージ側面に設けられたRF入力端子15に接続されるとともに、温度補償用回路13の入力端子25も、第1のACカット抵抗26を介してRF入力端子15に接続される。また、増幅回路11の出力端子20はパッケージ側面に設けられたRF出力端子16に接続されるとともに、出力検波回路12のバイアス入力端子30も、第2のACカット抵抗31を介してRF出力端子16に接続される。

(もっと読む)

差動増幅器回路、並びに、それを用いたデータ線ドライバ及び液晶表示装置

【課題】液晶表示パネルを駆動するデータ線ドライバの差動増幅器回路に望ましい振幅差偏差特性を実現する。

【解決手段】差動増幅器回路1が、正転入力端子9及び反転入力端子10にそれぞれに接続された一対のノンドープ型NMOSトランジスタMN1、MN2で構成されたNMOSトランジスタ対2と、正転入力端子9及び反転入力端子10にそれぞれに接続された一対のPMOSトランジスタMP1、MP2で構成されたPMOSトランジスタ対3と、ノンドープ型NMOSトランジスタMN1、MN2のドレインに接続されたフォールディッドカスコード型のカレントミラー4を含み、且つ、ノンドープ型NMOSトランジスタMN1、MN2及びPMOSトランジスタMP1、MP2を流れる電流に応答して出力電圧VOUTを生成する出力回路部(4、5、6、MP8、MN8)とを備えている。

(もっと読む)

高周波回路

【課題】出力される高周波信号の特性の劣化を抑制することができる高周波回路を提供すること。

【解決手段】基板12上に形成され、一端が外部と接続される入力線路16に接続された入力パッド13と、基板12上に形成され、一端が外部と接続される出力線路17に接続された出力パッド14と、入力パッド13と出力パッド14との間の基板12上に配列され、入力パッド13および出力パッド14と、それぞれ入出力用ワイヤ18、19により接続された複数のFET15と、を具備し、入力パッド13と複数の入力用ワイヤ18との接触点20および、出力パッド14と複数の出力用ワイヤ19との接触点21を、それぞれ、入出力パッド上13、14における直径がλ/16である円の内部の領域に集中させる。

(もっと読む)

高周波回路チップを実装した電子装置

【課題】広帯域に渡りインピーダンス整合する接続構造を実現すること。

【解決手段】高周波回路チップ100と伝送線路Fとの間に、高周波回路チップに対してワイヤボンディングされ、誘電体上に形成された第1信号線路61Lと、誘電体上において第1信号線路の両側に形成され、誘電体の裏面全体に形成された裏面接地導体と接続された、表面導体50Lの第1部分51Lから成る第1コプレーナ部Aと、第1コプレーナ部の第1信号線路に接続され、信号の伝送方向に沿った2辺に沿って、裏面接地導体と電気的に接続する複数のビアホールから成る側壁導体と、第1信号線路と連続する表面導体の第2部分と、裏面接地導体と、から成る集積導波管とを有する。第1信号線路と第2部分との接続点を、側壁導体間の幅の中点からずれた位置にすることで、この接続点から高周波回路チップ側を見たインピーダンスと集積導波管側を見たインピーダンスを等しくした。

(もっと読む)

半導体装置

【課題】本発明は、増幅回路を小型化できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、第1の信号入力端子、第1の信号出力端子及び第1の接地端子を有する第1のトランジスタと、第1の給電端子と、前記第1の給電端子と前記第1の信号入力端子の間に接続された第1の抵抗と、前記第1の給電端子と接地点の間に接続された第1のキャパシタと、を備え、前記第1のトランジスタ、前記第1の給電端子、前記第1の抵抗、及び前記第1のキャパシタは、同一のチップに設けられたことを特徴とする。

(もっと読む)

負荷インダクタがICダイの下に配置される集積電力増幅器

コンパクトな集積電力増幅器について、本明細書に述べられる。例示的な設計では、装置が、(i)電力増幅器用の少なくとも1つのトランジスタを有する集積回路(IC)ダイと、(ii)電力増幅器用の負荷インダクタを有するICパッケージとを含む。ICダイは、トランジスタ(複数可)が負荷インダクタの上に配置される状態でICパッケージ上に取り付けられる。例示的な設計では、ICダイは、ICパッケージ上の負荷インダクタの上に置かれるトランジスタマニホールドを含む。トランジスタ(複数可)は、トランジスタマニホールド内に作製され、トランジスタマニホールドの中心にドレイン接続を有し、トランジスタマニホールドの両側にソース接続を有する。ICダイおよびICパッケージは、1つまたは複数の追加の増幅器を含んでよい。各電力増幅器用のトランジスタ(複数可)は、その電力増幅器用の負荷インダクタの上に配置することができる。  (もっと読む)

(もっと読む)

マイクロ波電力増幅器

【課題】各電力増幅素子から見込んだインピーダンス整合回路のインピーダンス偏差を低減して、信号の合成効率および出力電力を向上可能なマイクロ波電力増幅器を得る。

【解決手段】同一構造の単位トランジスタ22a〜22dが3つ以上並列に配置されたトランジスタチップ20と、トランジスタチップ20の入力側に設けられた入力側インピーダンス整合回路12と、トランジスタチップ20の出力側に設けられた出力側インピーダンス整合回路32と、単位トランジスタ22a〜22dを、入力側インピーダンス整合回路12および出力側インピーダンス整合回路32とそれぞれ接続するボンディングワイヤ41a〜41d、42a〜42dとを備えたマイクロ波電力増幅器であって、ボンディングワイヤ41a〜41d、42a〜42dの自己インダクタンスと相互インダクタンスとの和が、全ての単位トランジスタ22a〜22dについて互いに等しくされている。

(もっと読む)

増幅器および発振器

【課題】MOSトランジスタの高周波領域におけるトランスコンダクタンスの劣化を招くことなく、低消費電力化を図ることが可能な増幅器などの提供。

【解決手段】この発明は、MOSトランジスタQ1などを含む増幅器である。MOSトランジスタQ1のゲートには第1の入力信号が入力され、MOSトランジスタQ1のバルクには第2の入力信号が入力され、MOSトランジスタQ1のソースから出力信号が出力される。そして、第1の入力信号と第2の入力信号とは同相の信号である。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

電圧変換回路および無線通信装置

【課題】差動信号を伝送することを可能としつつ、差動信号のコモン電位を調整する。

【解決手段】電流源GoP、GoNにてそれぞれ生成された差動電流IoP、IoNを差動電圧VoP、VoNに変換する負荷インピーダンスZLP、ZLNに共通抵抗RC1を接続し、電流源Gcにて生成された一定の電流Icを共通抵抗RC1に供給することで、共通抵抗RC1に同相電圧を発生させコモン電位Vcmを設定させる。

(もっと読む)

差動分布回路

【課題】接続線路のようなレイアウト寄生成分による帯域劣化を抑制する。

【解決手段】差動分布回路は、入力コプレナー線路CPW1P,CPW1Nおよび出力コプレナー線路CPW2P,CPW2Nに沿って配置された複数の差動増幅器とを備える。各差動増幅器は、電流源ISと、トランジスタQ1Pを含む差動半回路DPと、トランジスタQ1Nを含む差動半回路DNと、一端がトランジスタQ1Pのエミッタに接続され、他端が電流源ISに接続された接続線路ME1Pと、一端がトランジスタQ1Nのエミッタに接続され、他端が電流源ISに接続された接続線路ME1Nとから構成される。接続線路ME1P,ME1Nは、キャパシタンス成分がインダクタンス成分よりも大きい線路である。

(もっと読む)

増幅器

【課題】複数の増幅部(例えばキャリア増幅器及びピーク増幅器等)を有する増幅器を小型化することを目的としている。

【解決手段】入力信号が入力される入力部3と、入力信号を複数の信号に分岐させる分岐部4と、分岐部4で分岐された信号を増幅させる第一及び第二増幅部5、6と、第一及び第二増幅部5、6からそれぞれ出力されて合成された信号を出力する出力部9と、第一及び第二増幅部5、6が実装された基板2と、を備えており、第一増幅部5は、基板2の一方の主面2aに設けられ、第二増幅部6は、基板2の他方の主面2bに設けられている。

(もっと読む)

81 - 100 / 331

[ Back to top ]