Fターム[5J500AH17]の内容

Fターム[5J500AH17]に分類される特許

141 - 160 / 774

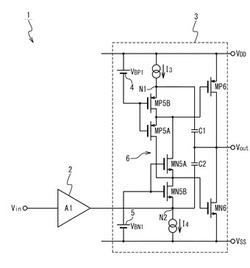

演算増幅器、並びに、それを用いた表示パネルドライバ及び表示装置

【課題】出力端子の電位の変動が位相補償キャパシタを介して出力トランジスタのゲートの電位を変動させることによる貫通電流の発生を防ぐ。

【解決手段】演算増幅器1が、出力PMOSトランジスタMP6と、出力NMOSトランジスタMN6と、ノードN1と出力端子Voutの間に接続された位相補償キャパシタC1と、ノードN2と出力端子Voutの間に接続された位相補償キャパシタC2と、浮遊電流源6を構成しているPMOSトランジスタMP5A及びNMOSトランジスタMN5Aと、ノードN1と浮遊電流源6の間に接続されたPMOSトランジスタMP5Bと、浮遊電流源6とノードN2の間に接続されたNMOSトランジスタMN5Bとを備えている。PMOSトランジスタMP5A、MP5Bのゲートは共通に接続され、NMOSトランジスタMN5A、MN5Bのゲートは共通に接続されている。

(もっと読む)

差動増幅回路、2段増幅回路およびそれらを用いたA/D変換回路

【課題】2組のプシュプル型CMOS反転増幅器を有する差動増幅回路において、同相入力電圧変動に対する出力動作点の変動を抑制するとともに、電源電圧除去比も高くする。

【解決手段】差動入力端子Vip,Vimに与えられる入力信号が直接または容量を介してゲートに与えられるpMOSトランジスタペア1と、容量C1,C2と、それらを介して入力信号が与えられるnMOSトランジスタペア2と、nMOSトランジスタペア2のゲート・ドレイン間に設けられたスイッチS1,S2と、で構成される2組のプシュプル型CMOS反転増幅器による差動増幅回路において、nMOSトランジスタペア2の共通ソースとGNDの間にゲートが出力端子Vom,Vopに接続されたnMOSトランジスタM5,M6を設ける。

(もっと読む)

レベルシフト回路及びそれを用いた発振器

【課題】 出力波形の割れや抜けを無くし、回路の誤動作が防止される低電圧動作のレベルシフト回路を提供する。

【解決手段】 レベルシフト回路は、電源端子VDDにソースを接続した第1のPMOSトランジスタP1と、接地端子GNDにソースを接続したNMOSトランジスタN1と、PMOSP1のドレインとNMOSN1のドレインとの接続点に接続された出力端子OUTと、NMOSN1のゲートに接続された入力端子INと、電源端子VDDにソースを接続し、PMOSP1のゲートにドレイン及びゲートを接続し、このドレインを第2の抵抗R2を介して接地端子GNDに接続した第2のPMOSトランジスタP2とを有し、PMOSP1及びP2は、カレントミラー回路を構成している。レベルシフト回路の出力波形の割れや抜けが無くなって誤動作を防止することが可能になる。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

雑音除去を備える広帯域LNA

雑音除去を備える低雑音増幅器(LNA)を改善するための技術が説明される。LNAは、入力ステージ回路において生成された雑音を除去するために協働する第1及び第2の増幅器を含む。入力ステージ回路は、RF信号を受信し、第1のノード及び第2のノードによって特徴付けられる。第1の増幅器は、第1のノードにおける雑音電圧を、第1の増幅器の出力において第1の雑音電流に変換する。第2の増幅器は、第1の増幅器の出力に直接結合され、第2のノードにおける雑音電圧の関数として第2の増幅器によって生成された第2の雑音電流と第1の雑音電流とを加算することによって、雑音除去を提供する。提案された技術は、大きな交流結合コンデンサへのニーズを排除し、LNAによって占められるダイ・サイズを低減する。LNAの増幅ステージ間での交流結合コンデンサの排除によって、電流の再利用が可能になり、その結果電流の消費が低減される。  (もっと読む)

(もっと読む)

差動入力段回路、差動入力段回路を備えた演算増幅器及び電圧レギュレータ回路

【課題】出力インピーダンスが大きい信号源を接続した場合でも大きなバイパスコンデンサを必要とせず、かつ電源電圧変動除去特性の良い差動入力段回路を提供する。

【解決手段】差動入力段回路を、差動入力部を構成し、ソースが結合されたトランジスタM1,M2と、トランジスタM1,M2とグランドとの間に接続された定電流源Icと、カレントミラー段を構成し、ソースが電源に接続されたトランジスタM3,M4と、トランジスタM3のドレーンにドレーンが接続され、トランジスタのドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM1と同一の導電型のトランジスタM5と、トランジスタM4のドレーンにドレーンが接続され、トランジスタM2のドレーンにソースが接続され、ゲートが基準電圧源Vbiasに接続された、トランジスタM2と同一の導電型のトランジスタM6と、で構成する。

(もっと読む)

エラーアンプの位相補償回路

【課題】 ICチップ上のコンデンサ面積を小さくすることができる位相補償回路を提供する。

【解決手段】 エラーアンプの出力端子に容量と抵抗を直列接続し、容量に流れる電流を抵抗の両端に接続したトランスコンダクタンスアンプにより増幅してフィードバックすることにより、エラーアンプの周波数特性の主要極の周波数を低くする。

(もっと読む)

電流源回路及びそれを用いた遅延回路及び発振回路

【課題】簡単な構成でデプレッション型MOSトランジスタの温度特性を補償する電流源回路を提供する。

【解決手段】2つのエンハンスメント型MOSトランジスタQ2、Q3から構成されたカレントミラー回路と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のドレインに接続され、定電流源として機能するデプレッション型MOSトランジスタQ1と、前記カレントミラー回路の入力側の前記エンハンスメント型MOSトランジスタQ2のソースに接続された負の温度特性を有する抵抗と、を含むことを特徴とする。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

半導体装置、データ伝送システム、及び半導体装置の制御方法

【課題】小振幅信号を高速に増幅して出力し、かつ、消費電力の少ないアンプを備える半導体装置を提供する。

【解決手段】クロックに同期してデータが更新される小振幅信号を受信するアンプ部と、アンプ部の出力に接続された出力部と、を備え、アンプ部はクロックに同期して小振幅信号の論理レベルが遷移しうるタイミングで電流源の電流を増加し、遷移しないタイミングで電流を減少する。出力部はクロックに同期してアンプ部の出力データの論理レベルが遷移しうるタイミングで出力インピーダンスを低下させて高速に負荷を駆動すると共に、論理レベルが遷移しないタイミングで出力インピーダンスを増加させて貫通電流が流れることを防ぐ。

(もっと読む)

受信回路

【課題】増幅率を損ねることなく同相入力範囲を拡大することができる受信回路を提供する。

【解決手段】受信回路は、第1の抵抗R3と第2の抵抗R4との抵抗比に基づき差動信号の一方の信号BPを分圧した第1の入力信号を出力する第1の分圧回路10と、第3の抵抗R5と第4の抵抗R6との抵抗比に基づき差動信号の他方の信号BMを分圧した第2の入力信号を出力する第2の分圧回路11と、第1、第2の入力信号を増幅して出力する差動増幅器12と、差動信号の同相電圧Vcmを検出する同相電圧検出回路13と、同相電圧Vcmに基づきバイアス電圧Vbの電圧値を切り替えるバイアス電圧切替回路14と、を有する。

(もっと読む)

出力回路

【課題】プッシュ側出力トランジスタの駆動回路とプル側出力トランジスタの駆動回路との対称性に優れ、これら出力トランジスタの駆動時における伝達特性の対称性が良好な出力回路を提供する。

【解決手段】電源レールV1と出力端子TOUTとの間に接続されたトランジスタMP1と、出力端子TOUTと電源レールV2との間に接続されたトランジスタMN1と、入力端子に入力される信号と基準電圧との差を増幅するgmアンプAP1と、第1、第2の制御端子及び第1、第2の被制御端子を持ち、電源レールV1とgmアンプAP1の第1の出力端との間に縦積みに接続されたカレントミラー回路CMP1,CMP2と、第1、第2の制御端子及び第1、第2の被制御端子を持ち、電源レールV2とgmアンプAP1の第2の出力端との間に縦積みに接続されたカレントミラー回路CMP1,CMP2とを備える。

(もっと読む)

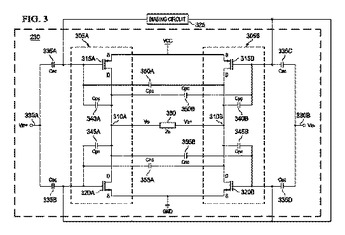

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

可変利得増幅回路

【課題】入出力範囲を電源電圧まで可能とする。

【解決手段】入力段に第1の演算増幅器51が、出力段に第2の演算増幅器52が、それぞれ配されると共に、第1の演算増幅器51の帰還路に第1のトランスコンダクタンス増幅器53が、第1及び第2の演算増幅器51,52の間に、第2のトランスコンダクタンス増幅器54が、それぞれ配されてなり、第1の演算増幅器51には第1の抵抗器61を介して入力信号を印加可能とし、その第1の抵抗器51に流れる電流と、第1の演算増幅器51の負帰還電流を等しくする一方、第2の演算増幅器52の入出力端子間に第2の抵抗器62を設けると共に、第2の演算増幅器52には、その終段がフルスイング可能に構成されたものを用い、第2の抵抗器62に流れる電流と第2のトランスコンダクタンス増幅器54の出力電流を等しくすることで、入出力範囲が電源電圧まで広げられたものとなっている。

(もっと読む)

電力増幅回路

【課題】 負荷駆動部の電源電圧を電界効果トランジスタの閾値電圧以下に低下させることが可能であり、消費電力を十分に低減させることができる電力増幅回路を提供する。

【解決手段】 Nチャネルトランジスタ705Aおよび705B並びに706Aおよび706Bは、高電位電源線701Pおよび低電位電源線701M間に直列に介挿され、負荷801および802を各々駆動する。プリドライバ703は、Lチャネル入力信号に基づきNチャネルトランジスタ705Aおよび705Bに対する各ゲート電圧を各々発生する。プリドライバ704は、Rチャネル入力信号に基づきNチャネルトランジスタ706Aおよび706Bに対する各ゲート電圧を各々発生する。可変電源701は、負荷801に対する出力信号OUTL、負荷802に対する出力信号OUTRが高電位電源線701Pおよび低電位電源線701M間の電源電圧の範囲内に収まるように同電源電圧を制御する。

(もっと読む)

演算増幅器

【課題】ジッタ特性に優れる演算増幅器を提供すること。

【解決手段】各ゲートに差動入力信号が入力される第1PMOSトランジスタ対PM6、PM7を有する第1差動増幅器PAと、各ゲートに差動入力信号が入力される第1NMOSトランジスタ対NM13、NM14を有する第2差動増幅器NAと、差動入力信号の同相成分を検出する同相成分検出部1と、同相成分から高周波成分を除去する高周波成分除去部2と、高周波成分が除去された同相成分に基づいて、差動入力信号のコモンモード電圧が第1基準電圧より高い場合、第1差動増幅器PAの動作を停止し、コモンモード電圧が第2基準電圧より低い場合(ただし、当該第2基準電圧は前記第1基準電圧より低い)、第2差動増幅器NAの動作を停止するための制御信号を発生する制御信号発生部3と、を備えた演算増幅器。

(もっと読む)

周波数変換回路

【課題】変換利得のばらつきを極めて小さく抑制された周波数変換回路を実現する。

【解決手段】入力電圧信号を電流信号に変換するGMアンプ10と、該変換して得られた電流信号をローカル信号でミキシングして周波数変換を行うスイッチング回路部(ミキサ)20と、該周波数変換によって得られた電流信号を電圧信号に変換するIV変換部(IV変換アンプ)30と、GMアンプ10へバイアス電圧を供給するバイアス回路(GM校正回路)40と、を備えGM校正回路40は、GMアンプ10に用いるトランジスタとそのサイズあたりの相互コンダクタンスを同一としたトランジスタを用いたレプリカアンプを内部に有し、該レプリカアンプに、抵抗と第1電流源からの電流との積に相当するDC電圧を入力し、該レプリカアンプからの電流出力が所定値になるように、該レプリカアンプの電圧バイアスを設定し、抵抗の分割点の電圧をGMアンプ10に供給する。

(もっと読む)

出力バッファ回路、入力バッファ回路、及び入出力バッファ回路

【課題】スルーレートを適切に調整可能なバッファ回路を提供する。

【解決手段】

CMOS出力バッファ回路は、バッファ回路Buffer[1]〜[4]を備えている。各バッファ回路は、電源電圧端子又は接地端子と出力端子との間にトランジスタPO及びNOを有している。各バッファ回路中の複数個のトランジスタPO及びNOは、外部からの制御信号に従い選択的に動作可能な状態とされる。各バッファ回路中の3個のトランジスタPOは、所定のサイズ比を有するように形成されている。

(もっと読む)

誤差増幅器

【課題】誤差増幅器における、受動素子の定数のばらつきに起因する帰還回路の定数のばらつきを抑制する。

【解決手段】誤差増幅器における帰還回路の定数が、受動素子の定数だけでなく、能動素子の利得にも依存して決定される構成にする。この誤差増幅器は、能動素子である電圧電流変換器20を含む構成である。また、第1の端子11、第2の端子13、オペアンプ16、第1の抵抗R1、第2の抵抗R2、第1乃至第5のトランジスタ、第1の電流源14および第2の電流源15を一体の集積回路とし、コンデンサC1を外付けしてもよい。

(もっと読む)

半導体集積回路

【課題】固定電位と入力信号を比較するカレントミラー型差動増幅器において、入力信号の立ち下り時に出力信号の遷移の遅れを改善して入力信号の立ち上がり時と立ち下がり時で出力信号の遷移時間差を少なくする。

【解決手段】カレントミラー型差動増幅器1-1 のミラートランジスタの共通ゲート端子のノードGPと定電流源回路TNCSの一端との間に、差動増幅器の出力信号OUTnをゲート入力とするトランジスタTNK1と、差動増幅回路の出力信号とは逆の論理の信号OUTpをゲート入力とするトランジスタTNK2とを直列に接続する。

(もっと読む)

141 - 160 / 774

[ Back to top ]