Fターム[5J500AH17]の内容

Fターム[5J500AH17]に分類される特許

121 - 140 / 774

D級増幅器

【課題】 デッドタイムが小さいD級増幅器を提供する。

【解決手段】 高電源電圧と低電源電圧と第1の中間電源電圧と第2の中間電源電圧を備えるD級増幅器の駆動回路において、出力段のロウサイドトランジスタが非導通のとき、ハイサイド制御信号に基づいて、第1の中間電源電圧に相当する電圧を生成する第1の電圧変換回路と、ハイサイドトランジスタが非導通のとき、ロウサイド制御信号に基づいて、第2の中間電源電圧に相当する電圧を生成する第2の電圧変換回路を備えることにより、ハイサイドトランジスタとロウサイドトランジスタが同時にオンするのを防ぐ。

(もっと読む)

スイッチング回路のノイズ低減装置

【課題】ノイズ低減効果が大きく、小型化が可能なスイッチング回路のノイズ低減装置を提供する。

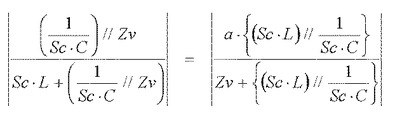

【解決手段】第1のスイッチングドライバの入力端に入力されるパルス信号と逆位相のパルス信号に基づいて動作する第2のスイッチングドライバと、一端が第2のスイッチングドライバの出力端に接続されるとともに他端がスイッチング回路の出力端子と接続されるインピーダンス素子とを具備し、インピーダンス素子のインピーダンス値Zvと、第1のコイルのインダクタンス値Lと、コンデンサの静電容量値Cと、第1及び第2のスイッチングドライバのスイッチング周波数fcとが、aを0以外の任意の定数として、(数3)の関係を満たす。 (もっと読む)

(もっと読む)

増幅回路、信号処理回路および半導体集積回路装置

【課題】回路面積を増大させることなく、シングルエンド出力構成と差動出力構成とを切り替える機能を有する増幅回路を提供する。

【解決手段】スイッチS1、S4がオフされ、スイッチS2がオンされると、負荷回路11が差動対7の能動負荷として機能するとともに出力端子12が内部で切り離される。これにより、増幅回路1は、入力端子8、9に入力された入力電圧Vinp、Vinmを差動増幅し、不平衡信号Voを出力端子13から出力するシングルエンド出力構成となる。スイッチS1、S4がオンされ、スイッチS2がオフされると、負荷回路11が差動対7の負荷として機能するとともに出力端子12が内部で接続される。これにより、増幅回路1は、入力端子8、9に入力された入力電圧Vinp、Vinmを差動増幅し、平衡信号Vom、Vopを出力端子12、13から出力する差動出力構成となる。

(もっと読む)

差動増幅回路

【課題】回路規模の小さい差動増幅回路を提供する。

【解決手段】差分電圧(Vinp−Vinn)が所定電圧よりも高いと、PMOSトランジスタ4がオンする。この時、電流源12は電流源11に並列接続され、電流源12は差動増幅回路10に駆動電流を供給する。つまり、電流源11だけでなくて電流源11〜12が、差動増幅回路10に合計電流(I11+I12)を駆動電流として供給する。よって、出力電圧Voutのスルーレートは大きくなる。また、出力電圧Voutのスルーレート制御のために、2つのPMOSトランジスタ及び電流源12が必要になるだけであるので、差動増幅回路10の回路規模が小さい。

(もっと読む)

表示装置、差動増幅回路、表示装置のデータ線駆動方法

【課題】パネルが大型化し、また、垂直同期周波数が高くなったとしても、画質の劣化を防止することが可能な表示装置を実現する。

【解決手段】表示装置の備える差動増幅器は、正電源と負電源との間に直列に接続された第1、第2トランジスタと、その各々のドレインを共通に接続された出力端子と、第1カレントミラー回路と出力端子との間に設けられた第1位相補償容量と、第2カレントミラー回路と出力端子との間に設けられた第2位相補償容量とを備える出力段回路と、加算回路と出力段回路との間に設けられて第1、第2トランジスタのバイアス制御を行うバイアス制御回路とを具備する。出力回路は、切り替え期間に第1、第2トランジスタの各々のゲートとソース間を短絡すると共に、第1位相補償容量及び前記第2位相補償容量を所定の電位へ充放電する。バイアス制御回路は、第1、第2トランジスタのゲート間の電流経路を遮断する。

(もっと読む)

可変電流増幅器、可変電流増幅装置、AGC回路

【課題】MOSトランジスタを用いた、高速動作が可能な可変電流増幅器を提供する。

【解決手段】入力電流が入力されるドレイン端子と、第1の制御電圧が供給されるゲート端子と、を有するMOSトランジスタ1、出力電流が出力されるドレイン端子を有するMOSトランジスタ4、第2の制御電圧が供給されるゲート端子を有するMOSトランジスタ2、MOSトランジスタ1のドレイン端子と接続される非反転入力端子3a、MOSトランジスタ2のゲート端子と接続される出力端子3c、MOSトランジスタ2のソース端子及びMOSトランジスタ3のドレイン端子が接続される反転入力端子3bを有する差動増幅器3とによって可変電流増幅器を構成し、第1の制御電圧または第2の制御電圧の少なくともいずれか一方の電圧値を可変に制御できるようにする。

(もっと読む)

電圧電流変換回路及びこれを備えたPLL回路

【課題】電源電圧依存性が小さい電圧電流変換回路及びこれを備えたPLL回路を提供する。

【解決手段】電圧電流変換回路は、第1電圧が供給される第1導電型のトランジスタで構成され、第1電流に基づいて第2電流を生成するカレントミラー回路と、前記第1電流が流れる第2導電型の第1のトランジスタと、一端が前記第1のトランジスタのソースに接続され、他端に第2電圧が供給され、入力された制御電圧に応じて抵抗値が変化する可変抵抗と、前記第2電流が流れ、ドレインとゲートとが前記第1のトランジスタのゲートに接続され、ソースに前記第2電圧が供給され、ゲート幅Wとゲート長Lとの比W/Lが前記第1のトランジスタの比W/Lより小さい第2導電型の第2のトランジスタと、前記第1電流または前記第2電流に基づいて出力電流を出力する電流出力部と、を備える。

(もっと読む)

レール・ツー・レール入力電圧範囲を有する差動増幅器

電圧出力装置

【課題】回路規模の増大を抑制することができ、特に液晶表示パネル等の表示装置の駆動回路への適用に適したオフセット補償機能を備えた電圧出力装置を提供する。

【解決手段】電圧出力装置は、反転入力端子および非反転入力端子を有するオペアンプと、反転入力端子の非反転入力端子への接続、非接続を切替える接続切換手段と、反転入力端子と非反転入力端子の接続時において、オペアンプの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を変化させる負荷抵抗変更手段と、反転入力端子と非反転入力端子を接続した状態において反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を順次変化させたときに、オペアンプの出力電圧が変化したときの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の抵抗値を維持させる負荷抵抗設定手段と、を含む。電圧出力装置は、反転入力端子と非反転入力端子の非接続時におけるオペアンプの出力電圧を出力する。

(もっと読む)

差動増幅器、及びソースドライバ

【課題】入出力間オフセットの電源電圧付近におけるリニアリティを改善することが可能な差動増幅器、及びソースドライバを提供すること。

【解決手段】本発明にかかる差動増幅器100は、入力対の一方が第1入力端子IN1をなす第1差動対111と、第1差動対111と並列に接続され、入力対の一方が第2入力端子IN2をなす、第1差動対111と同じ導電型の第2差動対112と、第1入力端子IN1に入力される第1入力電圧Vin1が第1差動対111の動作しきい値以上、かつ第2入力端子IN2に入力される第2入力電圧Vin2が第2差動対112の動作しきい値未満のときに、動作している第1差動対111の能力を低減する第1能力低減回路と、を備えるものである。

(もっと読む)

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

半導体装置及び電子機器

【課題】負荷(EL画素や信号線)に電流を供給するトランジスタにおいて、バラツキの影響を受けずに正確な電流を供給できる半導体装置を提供する。

【解決手段】増幅回路を使ったフィードバック回路を用いて、トランジスタの各端子の電圧を調節する。電流源回路から電流Idataをトランジスタに入力して、トランジスタが電流Idataを流すのに必要なゲート・ソース間電圧を、フィードバック回路を用いて設定する。フィードバック回路は、トランジスタが飽和領域で動作するように制御する。すると、電流Idataを流すのに必要なゲート電圧が設定される。そして、設定されたトランジスタを用いれば、正確な電流を負荷(EL画素や信号線)に供給できる。なお、必要なゲート電圧を設定するとき、増幅回路を用いるので、すばやく設定できる。

(もっと読む)

スイッチトキャパシタ回路

【課題】スイッチトキャパシタ回路におけるシングル/差動変換時の演算増幅器の同相入力変動を抑制し、低電源電圧での変換、または高速の変換にも対応することが可能なスイッチトキャパシタ回路を実現する。

【解決手段】サンプリングモード時とホールドモード時とで演算増幅器110の入力側のキャパシタC1〜C4をスイッチ回路SWで切り換えて単相入力信号を差動出力信号に変換するについて、サンプルモード時にサンプリング用キャパシタC1、C2、C3、C4の一端側に供給する第2の入力信号(電圧VH)を第1の信号入力電圧VIPと第1の参照信号電圧VINの中間の電圧とするような電圧生成部20を設けた。

(もっと読む)

コンパレータ回路

【課題】低消費電力動作を実現しつつ信号処理に向けた論理判定時間を格段に削減することができる。

【解決手段】入力電圧と参照電圧とを比較して論理判定結果の出力電圧を発生して差動増幅器を含むコンパレータ回路において、微小電流であるバイアス電流を発生して差動増幅器に供給する電流源と、差動増幅器からの差動電圧を反転して反転信号を出力する第1のインバータ回路と、電流源のバイアス電流を検出し、第1のインバータ回路の貫通電流を検出し、検出したバイアス電流及び検出した貫通電流に基づいて、差動増幅器が論理判定を行わない期間はバイアス電流で差動増幅器を動作させる一方、差動増幅器が論理判定する期間はバイアス電流を増加させてなる適応バイアス電流を用いて差動増幅器を動作させるように適応バイアス電流制御を行うための適応バイアス電流を発生して差動増幅器に供給する適応バイアス電流生成回路とを備える。

(もっと読む)

クラスAB増幅器

RFダウンコンバージョンミキサのための共通ゲート共通ソース相互コンダクタンスステージ

【課題】RFダウンコンバージョンミキサのための共通ゲート共通ソース相互コンダクタンスステージを提供する。

【解決手段】無線デバイス受信機チェーンは、共通ゲート共通ソース(CGCS)入力ステージ312を有するミキサ314を含む。チップ303外マッチングネットワーク308からの差動信号310、311は、ミキサのCGCS入力ステージに入力されることができて、ミキサは、信号をベースバンドあるいはいくつかの中間周波数にダウンコンバートする。入力ステージは、共通ゲート構成における1ペアのNMOSトランジスタと、共通ソース構成における1ペアのPMOSトランジスタと、を含む。存在するCGO相互コンダクタンス入力構成に対する、CGCS入力ステージの潜在的な利点は、PMOS差動ペアを通して、共通のソースステージを加えることによって、相互コンダクタンス利得が、高いQマッチングネットワークからデカップルされる。

(もっと読む)

A級プッシュプル増幅器

本発明は、入力(12)及び出力(14)を有する「プッシュプル」型の増幅器に関する。増幅器は、2つの電源間(V+及びV-)に反対に直列接続され、出力(14)が双方の間が接続される2つの増幅トランジスタ(18、20)を含む主増幅ブランチと、

増幅された信号を入力としてそれぞれ受信するように入力(12)に接続される増幅トランジスタ(18、20)それぞれのための制御回路(22、24)と、

を有する。主増幅ブランチは、トランジスタ(18、20)それぞれと出力(14)との間に、非線形の応答を有するユニット(38、40)と、トランジスタ(18、20)それぞの制御回路(22、24)の入力において、線形応答を有するユニット(38、40)に最小電流の流れを与えるのに適する非線形補償信号導入手段(30、32)とを含む。

(もっと読む)

増幅器

【課題】単相増幅器において、出力信号に含まれる2次歪み成分を除去する。

【解決手段】増幅器は、第1の導電型の半導体で形成され第1の出力電流ΔI1を出力する第1のMOSトランジスタNM12と、前記第1の導電型の半導体で形成される第2のMOSトランジスタNM13と、第2の導電型の半導体で形成され第2の出力電流ΔI2を出力する第3のMOSトランジスタPM12と、前記第1の出力電流ΔI1と前記第2の出力電流ΔI2との差電流により設定される負荷電流に応じて出力信号ΔIR1を生成する負荷抵抗RL1とを備える。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、出力段の貫通電流を抑制可能とした出力回路を提供する。

【解決手段】差動増幅段50、出力増幅段30、増幅加速回路10、容量接続制御回路20を備え、出力増幅段30は出力端子2とトランジスタ101、102を備え、増幅加速回路10は、差動増幅段の第1、第2の出力3、4と出力端子2間に夫々接続されたスイッチSW1とトランジスタ103並びにトランジスタ104とスイッチSW2を備え、容量接続制御回路20は、一端が出力端子に接続された容量素子C1、C2と、C1の他端と第1の電圧供給端子NE1との間に接続されたスイッチSW21と、C1の他端と前記差動増幅段の第1の差動対の出力7の間に接続されたスイッチSW22と、C2の他端と第2の電圧供給端子NE2との間に接続されたスイッチSW23と、C2の他端と差動増幅段の第2の差動対の出力8の間に接続されたスイッチSW24と、を備える。

(もっと読む)

オペアンプ及びこれを用いた液晶駆動装置、並びに、パラメータ設定回路、半導体装置、電源装置

【課題】定常消費電流を大きくせずスルーレートを高速化したオペアンプを提供し、また、外部端子数を増大せず、閾値電圧などのパラメータを任意に設定することが可能なパラメータ設定回路、並びに、これを備えた半導体装置、電源装置を提供する。

【解決手段】オペアンプは、一対のトランジスタから成る差動対を用いて正相入力信号と逆相入力信号との電位差に応じた電圧信号を生成する少なくとも一の差動入力部10、20と、前記差動入力部で生成される前記電圧信号に応じた論理レベルの出力信号を生成して出力する出力部30と、前記正相入力信号または前記逆相入力信号が急峻に変動したことを検出して補助電流Id1、Id2を生成する少なくとも一の補助電流生成部40、50と、所定の基準電流Id0と前記補助電流Id1、Id2とを足し合わせて前記差動入力部の駆動電流Idを生成する駆動電流生成部60と、を有する。

(もっと読む)

121 - 140 / 774

[ Back to top ]