Fターム[5J500AH17]の内容

Fターム[5J500AH17]に分類される特許

41 - 60 / 774

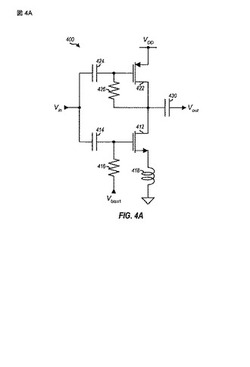

高線形性相補型増幅器

【課題】サブミクロンCMOSプロセスで製造されることができかつ良好な線形性および信頼性を有する相補型増幅器を提供する。

【解決手段】PMOSトランジスタ422とそれにスタック結合されたNMOSトランジスタ412で構成した相補型増幅器400で、NMOSトランジスタ412およびPMOSトランジスタ422は、別々のバイアス電圧を有し、それらのバイアス電圧は、各トランジスタの相互コンダクタンスの低高および高低遷移をオーバーラップさせるように選択され、各トランジスタの幅および長さ寸法は、中反転領域におけるNMOSトランジスタ412の入力容量の変化および相互コンダクタンスの変化を中反転領域におけるPMOSトランジスタ422の入力容量の変化および相互コンダクタンスの変化と整合させるように選択される。それによりほぼ一定の総入力容量およびほぼ一定の総相互コンダクタンスを有しうる。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置

【課題】レールツーレールDMOS増幅器の出力ステージにバイアスをかけるための方法及び装置を提供する。

【解決手段】本願発明は、増幅器であって、入力信号を受け取るための入力ステージと、前記入力ステージに連結されると共に、前記入力信号に応答して出力ドライバステージに対して駆動信号を提供する高利得ステージと、前記出力ドライバステージに連結された出力端子とを具備することを特徴とする。前記出力ドライバステージは、前記高利得ステージから第1の駆動信号“pdrive”を受け取る第1の端子、第1の電圧降下を通じてVDDに連結された第2の端子、及び、前記増幅器の前記出力端子に連結された第3の端子を有する高電位側ドライバ回路を備える。

(もっと読む)

完全差動型オペアンプ

【課題】完全差動型オペアンプの動作の安定度を向上し、高速動作を可能にする。

【解決手段】差動増幅部は、第1ステージの第1の差動増幅回路と、第2ステージの第2の差動増幅回路2から構成される。位相補償回路5は、第2の差動増幅回路2の差動入力端子と差動出力端子との間に接続されている。第1のCMFB回路3は、第1ステージの差動増幅回路1の差動出力電圧VP,VNの第1の同相電圧VC1が第1の基準電圧になるように、第1の差動増幅回路1をフィードバック制御する。第2のCMFB回路4は、第2の差動増幅回路2の差動出力電圧VOUTP,VOUTNの第2の同相電圧VC2が第2の基準電圧になるように、第2の差動増幅回路2をフィードバック制御する。

(もっと読む)

半導体集積回路

【課題】効果的に雑音レベルを低減した半導体集積回路を提供する。

【解決手段】差動入力トランジスタであるPチャネル型MOSトランジスタM1,M2は、雑音レベルを低減するために薄いゲート酸化膜を有している。これらのPチャネル型MOSトランジスタM1,M2を過電圧から保護する保護回路は、Pチャネル型MOSトランジスタM3,M4を含んで構成されている。Pチャネル型MOSトランジスタM3はPチャネル型MOSトランジスタM1を過電圧から保護する第1の保護トランジスタであり、Pチャネル型MOSトランジスタM1のドレイン側に直列に接続されている。Pチャネル型MOSトランジスタM4は、Pチャネル型MOSトランジスタM2を過電圧から保護する第2の保護トランジスタであり、Pチャネル型MOSトランジスタM2のドレイン側に直列に接続されている。

(もっと読む)

適応型バイアシングを用いた高スイング演算増幅器出力段

【課題】加工コストを増大させず、適応型バイアシング出力段を用いた高スイング演算増幅器を提供する。

【解決手段】出力段123は、VDDAノードと出力ノードとの間のプルアップ電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT3及びバイアシングトランジスタT4)を含み、前記出力ノードと接地ノードとの間のプルダウン電流経路内において直列に結合された2つのトランジスタ(スイッチングトランジスタT1及びバイアシングトランジスタT2)も含む。前記バイアシングトランジスタT4,T2を提供することは、前記トランジスタT3,T4において低下される最大電圧を低減させ、それによって前記トランジスタT1〜T4がVDDAよりも低い破壊電圧を有するのを可能にする。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶

縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、

しきい値電圧や移動度にバラツキが生じる。

【解決手段】本発明は、容量素子の両電極がある特定のトランジスタのゲート

・ソース間電圧を保持できるように配置した電気回路を提供する。そして本発明

は、容量素子の両電極間の電位差を定電流源を用いて設定できる機能を有する電

気回路を提供する。

(もっと読む)

増幅回路

【課題】簡易な構成で歪を抑制しつつ消費電流を低減する。

【解決手段】増幅回路100は、正入力端子T1と負入力端子T2とに供給される電圧の差分を増幅し差分電圧Vaを出力する差動増幅部10と、入力信号Vinの電圧を検出し検出電圧Vbを出力する入力電圧検出部20と、正電源電圧+Vccが供給される正電源端子T6と出力端子Toutとの間に設けられ、出力端子Toutから電流を吐き出すPMOS31と、負電源電圧−Vccが供給される負電源端子T7と出力端子Toutとの間に設けられ、出力端子Toutから電流を吸い込むNMOS32とを有する出力部30とを備える。

(もっと読む)

差動増幅回路

【課題】差動増幅回路における入力オフセット電圧の上昇を抑制しつつ、同相入力電圧範囲を拡張する。

【解決手段】本発明による差動増幅回路は、ソース及びバックゲートが第1電流源205に共通接続された差動対トランジスタ201、202を備える差動入力段回路111と、差動入力段回路111の出力端子に接続される出力段回路121と、第1電流源205と出力段回路121の第2電流源206のそれぞれの電流I1、I2を、差動入力段回路111への入力電圧VIN1、VIN2に応じた大きさに調整する電流制御回路101とを具備する。

(もっと読む)

増幅回路

【課題】追加プロセスなしに、コモンモード入力電圧が定格電源電圧の任意倍数の電圧でも耐えることができる高耐圧の入力段とすることが可能な増幅回路を提供する。

【解決手段】増幅回路の入力段は、入力端子IN1,IN2が接続された第1の差動対トランジスタ10と、N1VDDに接続された第1の入力段電流バイアス手段20と、第1の差動対トランジスタ10と第1の入力段電流バイアス手段20に接続された第1の入力段カスコードトランジスタ群30と、第1の差動対トランジスタ10に接続された第2の入力段カスコードトランジスタ群40と、0VからN1VDDまで変化するコモンモード入力電圧が入力されたときに、第1の差動対トランジスタ10、第1の入力段カスコードトランジスタ群30、第2の入力段カスコードトランジスタ群40のVGSとVGDの絶対値がVDD以内となるバイアス電圧に調整する入力段バイアス調整回路60を備えている。

(もっと読む)

電圧電流変換回路

【課題】差動入力部を有するとともに、出力部を構成するカレントミラー回路のミラー比を調整して入力オフセット電圧をもたせた電圧電流変換回路において、差動入力部および入力オフセット電圧の温度特性を平坦なものにする。

【解決手段】平坦な温度特性を有する第1の定電流Ib1に正の温度特性を有する第2の定電流Ib2を加えた電流をバイアス電流として、MP10及びMP11からなる差動入力部に供給することにより、差動入力部の温度特性とバイアス電流の温度特性とを相殺させて差動入力部の温度特性をゼロ(平坦なもの)にすることができる。また、電流吐き出し型の第1のカレントミラー回路の出力と、電流吸い込み型の第2のカレントミラー回路の出力との接続点を電圧電流変換回路の出力端子Out2とし、この接続点に第1の定電流Ib1に比例した電流を加える構成により、温度特性のない入力オフセット電圧も実現することができる。

(もっと読む)

容量性スピーカ駆動回路

【課題】高音の音声信号が所定のレベル以上で所定時間以上入力されたときに、利得を低減させて高音過電流が発生することを防止する。

【解決手段】出力ドライバのパワートランジスタに流れる電流が所定時間以上にわたって所定値を超えた場合に高音過電流検出信号を発生する高音過電流検出手段と、前記高音過電流検出信号が発生されると前記プリアンプの通過周波数帯域を低くさせる通過周波数帯域切替手段とを設けた。

(もっと読む)

電力増幅器

【課題】 オフセット補正後の電力増幅器の動作開始時に電力増幅器に接続されたスピーカからポップ音が発生するのを防止する。

【解決手段】 直流電圧発生回路170は、D級増幅器内の差動増幅器のオフセットキャンセルを行わせるためにD級増幅器の出力端子T21およびT22に直流電圧を供給する。この直流電圧発生回路170の出力端子T30と接地線との間には放電用抵抗RDISとNチャネルトランジスタ183が介挿されている。オフセットキャンセルが終わった後、D級増幅器の増幅動作が開始される前の安定期間に、Nチャネルトランジスタ183はONとされ、出力端子T21およびT22に接続された容量C1およびC2の充電電荷が放電用抵抗RDISおよびNチャネルトランジスタ183を介して放電される。これによりポップ音の発生を防止することができる。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】変調信号のオンデューティー比が上限付近の状態が継続しても、D級増幅器を正

常に動作させて駆動信号を出力が可能とする。

【解決手段】駆動波形信号から生成した変調信号を電力増幅した後、平滑化することによ

って駆動信号を生成する。変調信号を電力増幅するデジタル電力増幅器では、電源とグラ

ンドとの間で2つのNチャンネル(以下ch)MOSFETをプッシュ・プル接続し、更

に、電源側のNchMOSFETに対して並列にPchMOSFETを接続する。こうす

れば、電源側のNchMOSFETをONにするためのブートストラップコンデンサーに

蓄えられた電荷が不足してNchMOSFETをONにすることができない場合でも、P

chMOSFETをONにすることで電力増幅を行うことができ、駆動信号を出力するこ

とが可能となる。

(もっと読む)

オペアンプ

【課題】低い電源電圧に対応する生産プロセスで生産された製品に対して高い電源電圧を供給した場合にも、ホットキャリアに起因するオペアンプ特性の劣化を回避することができるオペアンプを提供する。

【解決手段】バイアス電源回路が、2つのカレントミラー回路の間に挿入された一対の抵抗部を有して定電流バイアス電位の他に付加バイアス電位を生成し、差動増幅器が、差動入力トランジスタ対と能動負荷トランジスタ対との間に挿入され且つ当該付加バイアス電位によってバイアスされる電圧降下用トランジスタ対を含むオペアンプ。

(もっと読む)

差動増幅回路

【課題】チップ面積を小さくする。

【解決手段】一端がグランド端子14に接続される定電流源13と、ソースが共通に定電流源13の他端に接続され、ゲートが入力端子A、Bにそれぞれ接続される第1および第2の差動対(Q11、Q12およびQ13、Q14に相当)と、第1の差動対のそれぞれのドレインにそれぞれのソースを接続するnMOSトランジスタQ15、Q16と、nMOSトランジスタQ15、Q16のそれぞれのドレインを出力端子C、Dとし、出力端子C、Dと電源端子11との間に接続される負荷部(図1のQ17、Q18に相当)と、を備え、第1の差動対のそれぞれのドレインを第2の差動対の逆相となるそれぞれのドレインに接続し、nMOSトランジスタQ15、Q16のそれぞれのゲートは、nMOSトランジスタQ15、Q16のドレインにそれぞれ接続する。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

差動増幅器及びアナログ/デジタル変換器

【課題】スイッチに流れるオフリーク電流の影響を抑制し、利得の発振を抑える。

【解決手段】差動増幅器16は、入力信号が入力される入力端子27,28と、前記入力信号が増幅された出力信号を出力する出力端子25,26と、を備える差動増幅器16であって、前記入力信号を増幅し前記出力信号を生成する増幅部21と、前記増幅部21と電源端子との間に接続され、第1導電型トランジスタT34,T35と、前記第1導電型トランジスタT34,T35のゲート端子をドレイン端子に接続するかまたは前記出力端子25,26に接続するかを切り替える切り替えスイッチ22と、を有する負荷回路23と、前記切り替えスイッチ22のオフリーク電流を低減するキャンセル電流を生成するリークキャンセルスイッチ30と、を備える。

(もっと読む)

41 - 60 / 774

[ Back to top ]