Fターム[5J500DP02]の内容

Fターム[5J500DP02]に分類される特許

201 - 220 / 395

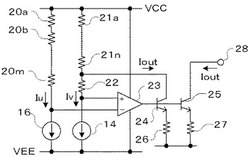

バイアス電流発生回路およびそれを用いた差動回路

【課題】半導体プロセスに起因する遅延時間および消費電力のばらつきを小さくすることができるバイアス電流発生回路およびそれを用いた差動回路を提供する。

【解決手段】バイアス電流発生回路は、半導体プロセスによって出力電流がばらつく第1の電流発生回路14と第2の抵抗21a〜21n、第3の抵抗22を直列接続し、半導体プロセスによって出力電流がばらつかない第2の電流発生回路16と第1の抵抗20a〜20mを直列接続して、第1の電流発生回路と第3の抵抗の接続点の電圧と、第1の抵抗と第2の電流発生回路の接続点の電圧を増幅器に入力して、この増幅器の出力によって第2の抵抗と第3の抵抗の接続点から電流を引き出すと共に、この電流に関連する電流を出力する。また、このバイアス電流発生回路の出力電流で差動回路の出力段の駆動電流を決める。

(もっと読む)

定電流源回路及び差動増幅装置

【課題】高周波領域でも、定電流源部の出力インピーダンスを確保して、差動増幅回路の同相信号除去比の低下を抑えることができる定電流源回路及び差動増幅装置を得ることを目的とする。

【解決手段】駆動用の電流を供給する基準電流源11と、その基準電流源11から供給された電流を折り返して、その電流を差動増幅回路2に供給するカレントミラー回路12とを備え、カレントミラー回路12と差動増幅回路2の間に抵抗R3を配置する。これにより、高周波領域でも、定電流源部12aの出力インピーダンスを確保して、差動増幅回路2の同相信号除去比CMRRの低下を抑えることができる。

(もっと読む)

高周波回路

【課題】広帯域にわたって平坦な利得を得たい。

【解決手段】トランジスタM6は、ソース端子の電位が固定され、ドレイン端子に負荷が接続され、入力信号をゲート端子で受ける。トランジスタのドレイン端子と負荷との接続点と、高周波回路の出力端子との間に、インダクタL2および容量C2が直列に接続された直列回路を設ける。トランジスタM6の出力インピーダンスを表す出力等価回路、負荷、および直列回路により、所定の特性を備えるバンドパスフィルタを構成する。

(もっと読む)

電力増幅回路

【課題】容量性の負荷を駆動する電力増幅回路において、損失を低減させる。

【解決手段】電力増幅回路は、入力信号Vin,Vipを増幅して出力信号を生成して容量性の負荷である圧電スピーカ120を駆動する前段増幅回路110およびBTL接続増幅回路140と、制御部130とを備える。制御部130は、入力信号又は出力信号の周波数を検出し、周波数の検出結果とコンパレータ132の出力信号に応じて、BTL接続増幅回路140に供給する電源電圧を制御する。

(もっと読む)

ミクサ回路

【課題】入力される信号が大信号でも信号入力用バイポーラトランジスタのコレクタ電流の降下を抑制し高飽和特性を実現するミクサ回路を提供する。

【解決手段】中間周波又は高周波の差動信号を入力する入力用トランジスタ対4a,4b、局部発振波の差動信号を用い入力用トランジスタ対により入力された中間周波又は高周波の差動信号を高周波又は中間周波の差動信号に変換する信号変換回路5a〜5d、入力用トランジスタ対のエミッタ端子に接続されたトランジスタ7、トランジスタ7とカレントミラーを構成するバイアス用トランジスタ8、信号変換回路の出力差動信号又は入力差動信号を入力電力としてモニタする電力モニタ用回路11、電力モニタ用回路の出力電流を基準電流とするP型カレントミラー回路10a,10bを備え、P型カレントミラー回路の出力電流がバイアス用バイポーラトランジスタの基準電流であるミクサ回路。

(もっと読む)

電力増幅回路

【課題】容量性の負荷を駆動する電力増幅回路において、損失を低減させる。

【解決手段】電力増幅回路は、入力信号Vin,Vipを増幅して出力信号を生成して容量性の負荷である圧電スピーカ120を駆動する前段増幅回路110およびBTL接続増幅回路140と、BTL接続増幅回路140の消費電流を検出する電流計測部131と、電流計測部131の検出結果とコンパレータ132の出力信号に応じて、BTL接続増幅回路140に供給する電源電圧を制御する制御部130とを備える。

(もっと読む)

集積回路の制御電圧決定方法、TEG回路のゲート電圧決定方法、TEG回路試験方法及び試験装置

【課題】集積回路において、トランジスタのしきい値電圧などの特性変動あるいはばらつきが与える回路動作への影響を受けにくい集積回路およびTEG回路を提供する。

【解決手段】1対の抵抗デバイスMP1,MP2と、1対のN型差動トランジスタMN1,MN2と、該1対のN型差動トランジスタに動作電流を供給する電流源トランジスタMLとを備えた電流モード動作回路において、その電流源トランジスタに流れる電流の制御電圧VLを、N型差動トランジスタのしきい値電圧などの特性変動に対して、集積回路の電圧利得が少なくとも1以上となるよう決定する。

(もっと読む)

差動増幅器

【課題】 負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】 差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

可変インピーダンス回路、それを用いた可変インピーダンスシステム、フィルタ回路、増幅器、通信システム

【課題】可変インピーダンス回路の歪を低減したい。

【解決手段】第1トランジスタM1は、差動入力信号の一方を受ける第1端子と、インピーダンスを変化させるための制御信号を受ける第2端子と、第2トランジスタと接続された第3端子と、基板に電位を供給するための第4端子とを含む。第2トランジスタM2は、差動入力信号の他方を受ける第5端子と、制御信号を受ける第6端子と、第1トランジスタと接続された第7端子と、基板に電位を供給するための第8端子とを含む。第3端子、第4端子、第7端子および第8端子が接続される。

(もっと読む)

スタック型差動信号送信回路

【課題】チャンネル当たりの電力散逸が減少されており、回路の複雑性が低く、内在的な帯域幅の制限が無く、データ又はクロックのエンコーディング無しで動作可能であり、信号受信器に関しての付加的な条件を課すことなしに動作可能であり、且つEMI及びその他のノイズ源に対しての高いロバストの耐久性を有する差動I/Oインタフェースを有する差動信号送信回路を実現する。

【解決手段】チャンネル間において信号電流を再使用することにより電力散逸を最小化させるために電源電極間においてスタック型関係で複数の差動信号送信回路が結合されている差動信号送信回路。

(もっと読む)

増幅器、および低ノイズ増幅器(LNA)の利得を制御する方法

【課題】同相モードのフィードバックおよび利得制御を有する差動低ノイズ増幅器(LN

A)。

【解決手段】低ノイズ増幅の方法、アルゴリズム、アーキテクチャ、回路、および/ある

いはシステムが開示される。一実施形態で、増幅器は差動信号を受信するよう構成される

第1差動入力、第1差動入力に連結される第1電流ソース、第1バイアス電圧を受け、入

力段を第1電源に連結する第1電流ロード、および第1電流ロードの出力に連結され第1

電流ソースへの電流を制限するよう構成される第1対の同相モードのフィードバック・ト

ランジスタを含むことができる。入力段は入力段に類似した構造を有し、増幅信号をさら

に増幅するよう構成される追加段に増幅信号を提供する。

(もっと読む)

トランスコンダクタ

【課題】高周波帯域でのゲインを損なわない位相補償器を備えたトランスコンダクタを提供する。

【解決手段】トランスコンダクタは、第1の入力信号が入力端Vin+へ入力される増幅器A1と、第2の入力信号が入力端Vin−へ入力される増幅器A2と、増幅器A1、A2の出力が入力される電圧電流変換器Gm1と、電圧電流変換器Gm1の出力端間に接続される抵抗R1と、増幅器A1の出力と増幅器A2の出力から同相信号を検出する同相信号検出器CMと、同相信号検出器CMの出力を入力とし、電圧電流変換器Gm1へ電流を出力する電圧電流変換器Gm2、Gm3と、同相信号検出器CMの出力端と増幅器A1の出力端との間に接続される位相補償器PC1と、同相信号検出器CMの出力端と増幅器A2の出力端との間に接続される位相補償器PC2と、増幅器A1の出力および増幅器A2の出力を入力とする第4の電圧電流変換器Gm4と、を具備する。

(もっと読む)

半導体回路

【課題】同相入力電位の変化により、出力電流が変化し動作速度の低下が問題となる。

【解決手段】本発明にかかる増幅回路は、差動出力段と差動入力段を有し、差動出力段は第1、第2電源間に接続され差動信号を出力する第1、第2電流経路を有し、第1電流経路は、第1電源と第1ノード間に第1抵抗素子、第1、第2ノード間に第1、第2トランジスタ、第2ノードと第2電源間に第2抵抗素子を有し、第2電流経路は、第1電源と第3ノード間に第3抵抗素子、第3、第4ノード間に第3、第4トランジスタ、第4ノードと第2の電源間に第4抵抗素子を有し、第1、第2、第3、第4トランジスタのゲートは、それぞれ第4、第3、第2、第1ノードと接続され、差動入力段の出力電流は、第1、第3ノードに接続されることを特徴とする。

(もっと読む)

D級アンプ

【課題】入力信号が微小レベル時のリニアリティを改善したフルブリッジ方式D級アンプを提供する。

【解決手段】4個のスイッチング素子22,24,26,28をフルブリッジ接続してスピーカ30を駆動する。スイッチング素子22,24をパルス信号PWM1で駆動し、スイッチング素子26,28をパルス信号PWM2で駆動する。パルス信号PWM1,PWM2は入力信号レベルに応じてパルス幅変調された信号である。パルス信号PWM1,PWM2の入力信号レベル対デューティ比特性は、通常の入力信号レベル対デューティ比特性に偶関数でオフセットを与えた特性である。これにより、入力信号が微小レベル時にスイッチング素子は細いパルスで駆動されなくなり、リニアリティが改善される。

(もっと読む)

振幅制限増幅回路

【課題】前段の基本増幅段への入力信号波形が充分に急峻でない場合にも、デューティ変動補正効果が得られるようにする。

【解決手段】入力データ信号の平均値を生成する平均値検出回路と、該平均値検出回路の出力を一方の入力端子に接続した差動型振幅制限増幅器とを有する基本増幅段を前後2段縦続接続した振幅制限増幅回路において、前段の基本増幅段10の出力データ信号の立上り時間と立下り時間を鈍らせるための波形調整回路30,40を前記前段の基本増幅段10と後段の基本増幅段20との間に接続する。

(もっと読む)

デジタル変調のためのシステム及び方法

【課題】電力増幅及び送信のためのシステム及び方法を提供する。

【解決手段】同じプロセスでベースバンド信号を搬送波周波数の信号にシフトするため、アップコンバータにより中心周波数を変更し合成される電力増幅を可能にするシステム及び方法。そして、デジタルにより実現し、電力効率がよく、線形性問題がほとんど、又は全く無く、シリコンチップ及び広帯域動作に適した技術である。それぞれの入力サンプルは、同じサンプリング間隔内のいくつかのサブサンプルと置き換えられ、サブサンプルの合計の重みは、置換されたサンプルに等しい。このサブサンプルへのプロセスは、サンプリング信号の周波数応答を変え、負荷ドライバの振幅ダイナミックレンジを減少させ、デジタルアナログ変換のためのフィルター要件を簡素化し、負荷ドライバの線形性要件を減少させる。このプロセスは、デジタル回路でもよく、広帯域動作をもたらす。

(もっと読む)

アクティブポストディストーション線形化を有する差動増幅器

優れた線形性および雑音性能を有する差動増幅器(300)は、第1(310),第2(320),第3(330),及び第4(340)のトランジスタ及び誘導子(350)を含む、第1の側面を含む。第1(310)及び第2(320)のトランジスタは、第1のカスケード対として結合され、第3(330)及び第4(340)のトランジスタは、第2のカスケード対として結合される。第3のトランジスタ(330)は、第2のトランジスタ(320)のソースに結合したゲートを有し、第4のトランジスタ(340)は、第2のトランジスタ(320)のドレインに結合したドレインを有する。第1のトランジスタ(310)は、信号増幅を提供する。第2のトランジスタ(320)は、負荷分離を提供し、第3のトランジスタ(330)に対して中間信号を生成する。第3のトランジスタ(330)は、第1のトランジスタ(310)によって生成される3次歪み成分を除去するのに用いられる歪み成分を生成する。誘導子(350)は、第1のトランジスタ(310)に対してソースディジェネレーションを提供し、歪み除去を向上させる。第2(320)及び第3(330)のトランジスタの大きさは、利得損失を低減させるために選択され、増幅器に関して優れた線形性を達成する。差動増幅器は、第1の側面と同様の機能を果す、第2の側面も含みうる。  (もっと読む)

(もっと読む)

半導体装置

【課題】電圧依存性のあるMOS容量を、例えばオペアンプの位相補償用回路素子として使用する際に、オペアンプの入力あるいは出力電圧が如何なる電圧領域でも、MOS容量値が減少して位相余裕が減少することがない構成を実現する。

【解決手段】半導体基板上に形成されたゲート電極と拡散層間に絶縁膜を有する構造のMOS容量を用いた位相補償用回路6を備え、位相補償用回路は第1および第2のMOS容量14、15により構成される。第1のMOS容量のゲート電極端子と、第2のMOS容量の拡散層側端子(ゲート電極端子とは反対の端子)が等価的に接続され、第1のMOS容量の拡散層側端子と第2のMOS容量のゲート電極端子の間に、電流が流れることにより電位差を発生する電位差発生素子16が接続される。

(もっと読む)

差動増幅回路

【課題】無調整で、より高精度で理想的なベース電流補償回路付きの差動増幅回路を実現する。

【解決手段】 トランジスタQ1〜Q4、電流源I1、負荷抵抗R1,R2、カレントミラー回路C1、C2を備えた差動増幅回路において、カレントミラー回路C1,C2に入力電流を与える電流源I2,I3とを設け、トランジスタQ1〜Q4の電流増幅率をβ、トランジスタQ3,Q4のコレクタ電流をIとするとき、電流源I2,I3の電流値をI/β2に設定する。

(もっと読む)

カスコード増幅器

【課題】 温度変動やプロセスのバラツキによる動作点及び特性の変動を抑えることが可能なカスコード増幅器を実現する。

【解決手段】 カスコード増幅器において、前段増幅回路の差動出力を増幅して出力するカスコード増幅回路と、バイアス電流に基づきカスコード増幅回路にバイアス電圧を供給すると共にバイアス電流及び前段増幅回路のバイアス電流を加算してカスコード電圧を決定しカスコード増幅回路のカスコードトランジスタのベースに印加するバイアス回路とを設ける。

(もっと読む)

201 - 220 / 395

[ Back to top ]