Fターム[5J500DP02]の内容

Fターム[5J500DP02]に分類される特許

61 - 80 / 395

利得可変回路

【課題】利得制御信号の分配配線を簡素化し、回路の高周波化・広帯域化を実現し、負方向の利得可変幅を増大させる。

【解決手段】利得可変回路は、入力信号Inを増幅する可変利得増幅器(VGA)1と、VGA1の出力信号Out1を増幅する固定利得増幅器(Amp)2と、Amp2の出力信号Out2の振幅を検出して、検出した振幅と予め設定された振幅設定値とが等しくなるようにVGA1の利得を制御する自動利得調整回路(AGC)3とを備える。VGA1は、ギルバートセル型の可変利得増幅器である。

(もっと読む)

可変利得増幅器

【課題】可変利得増幅器において、広帯域性と大きなダイナミックレンジを両立させる。

【解決手段】ベース端子が反転入力端子ICに接続され、コレクタ端子が反転出力端子OCに接続され、エミッタ端子が開放されているトランジスタ(第3のトランジスタ)Q21と、ベース端子が非反転入力端子ITに接続され、コレクタ端子が非反転出力端子に接続され、エミッタ端子が開放されているトランジスタ(第4のトランジスタ)Q22とを設ける。

(もっと読む)

差動増幅器

【課題】負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

ゲイン切り替え回路

【課題】信号の広帯域化を図る。

【解決手段】入力信号に対し、それぞれ所望の減衰量を設定可能なゲイン切り替え部GCk(k=1〜n、nは2以上の整数)と、ゲイン切り替え部GCkの出力をそれぞれ入力に接続し、出力を共通に接続する入力差動対TXkと、それぞれのゲイン切り替え部GCkの減衰量及びそれぞれの入力差動対TXkの活性化を制御するスイッチ制御回路103と、を備え、ゲイン切り替え部GCkは、入力信号を一端に受け、他端を入力差動対TXkの入力端に接続する抵抗素子RPkAと、スイッチ制御回路103によってオンオフが制御されるスイッチ素子SWPkj(j=1〜m、mは2以上の整数)と、一端を抵抗素子RPkAの他端に接続し、他端をそれぞれスイッチ素子SWPkjを介して基準電圧VREFに接続する抵抗素子群PRkと、を備える。

(もっと読む)

差動増幅回路及びA/D変換器

【課題】電源電圧が比較的小さい場合においても、性能劣化を起こさず、かつオーバードライブリカバリ可能な差動増幅回路を得る。

【解決手段】第1の出力部であるノードN1と電源Vddとの間にPMOSトランジスタMP1及びMP3が互いに並列に介挿され、第2の出力部であるノードN2と電源Vddとの間にPMOSトランジスタMP2及びMP4が互いに並列に介挿される。レプリカ回路4及びコンパレータ5によって、入力電圧Vinと基準電圧Vrefとの入力電位差が“0”のバランス状態時の出力電圧Voutp及びVoutnは共に基準出力コモン電圧Voutcm_idealに設定される。電源電圧Vddと出力コモン電圧Voutcmとの電位差がダイオード接続されたPMOSトランジスタMP1及びMP2の閾値電圧Vthよりも低い値となるように、レプリカ回路4の基準出力コモン電圧Voutcm_idealを設定する。

(もっと読む)

増幅器、及び通信装置

【課題】 少ない回路規模で位相特性を補償できる増幅器及び通信装置を提供する。

【解決手段】 正相入力信号を増幅して正相出力信号を生成し、逆相入力信号を増幅して逆相出力信号を生成する増幅器であって、正相入力信号を増幅して第1正相信号を生成し、逆相入力信号を増幅して第1逆相信号を生成する第1増幅回路と、正相入力信号を増幅して第2正相信号を生成し、逆相入力信号を増幅して第2逆相信号を生成する第1増幅部と、正相入力信号を増幅して第3正相信号を生成し、逆相入力信号を増幅して第3逆相信号を生成する第2増幅部を有する第2増幅回路と、を備え、正相出力信号が、第1正相信号と第2正相信号との和であり、逆相出力信号が第1逆相信号と第2逆相信号との和である、又は正相出力信号が、第1正相信号と第3逆相信号の和であり、逆相出力信号が第1逆相信号と第3正相信号との和であることを特徴とする増幅器を提供する。

(もっと読む)

スイッチトキャパシタ回路

【課題】スイッチトキャパシタ回路における全差動動作時の演算増幅器の同相入力変動を抑制し、低電源電圧での変換、または高速の変換にも対応することが可能なスイッチトキャパシタ回路を提供する。

【解決手段】スイッチトキャパシタ回路の出力段に設けられた第1の演算増幅器110の非反転入力端子(+)への入力信号を第2の演算増幅器120の反転入力端子(−)に供給するようにしてネガティブフィードバックを形成することによってVx(≒Vy)=VCMとなるように第2の参照電圧VCMaを調整することにより、入力信号の同相入力のレベルに依らず第1の演算増幅器110の同相入力を所定の定電圧VCMのレベルに保つ。また、第1の参照電圧VCMaの変動は差動回路でキャンセルされ、本来の全差動動作には影響を及ぼさない。

(もっと読む)

スイッチトキャパシタ回路

【課題】スイッチトキャパシタ回路におけるシングル/差動変換時の演算増幅器の同相入力変動を抑制し、低電源電圧での変換、または高速の変換にも対応することが可能なスイッチトキャパシタ回路を実現する。

【解決手段】サンプリングモード時とホールドモード時とで演算増幅器110の入力側のキャパシタC1〜C4をスイッチ回路SWで切り換えて単相入力信号を差動出力信号に変換するについて、サンプルモード時にサンプリング用キャパシタC1、C2、C3、C4の一端側に供給する第2の入力信号(電圧VH)を第1の信号入力電圧VIPと第1の参照信号電圧VINの中間の電圧とするような電圧生成部20を設けた。

(もっと読む)

差動信号受信回路及び半導体装置

【課題】寄生容量を少なくし、動作の高速性を妨げることなく、差動対間のインピーダンスを調整可能にした差動信号受信回路、及び差動信号受信回路を備える半導体装置を提供する。

【解決手段】一対の差動信号が入力する第1、第2の差動トランジスタと、第1、第2の差動トランジスタの出力端子にそれぞれ接続された負荷回路と、第1、第2の差動トランジスタの電源端子に接続された電流源回路と、第1の差動トランジスタの電源端子と前記第2の差動トランジスタの電源端子との間に接続されたインピーダンス調整回路及びスイッチトランジスタと、を備える差動信号受信回路であって、スイッチトランジスタは、差動信号受信回路に供給される電源電圧より高電圧になる信号が印加されて導通、非導通が制御される。

(もっと読む)

回路ユニット、回路ユニットを有するバイアス回路、並びに第1及び第2の回路ユニットを有する差動増幅回路

ヘテロ接合バイポーラトランジスタ及びロングゲート疑似格子整合高電子移動度トランジスタを備える回路ユニット(CU)。前記ロングゲート疑似格子整合高電子移動度トランジスタのソース(S)又はドレイン(D)が、前記ヘテロ接合バイポーラトランジスタのコレクタ(C)又はエミッタ(E)に電気的に結合される。 (もっと読む)

差動増幅回路、2段増幅回路およびそれらを用いたA/D変換回路

【課題】2組のプシュプル型CMOS反転増幅器を有する差動増幅回路において、同相入力電圧変動に対する出力動作点の変動を抑制するとともに、電源電圧除去比も高くする。

【解決手段】差動入力端子Vip,Vimに与えられる入力信号が直接または容量を介してゲートに与えられるpMOSトランジスタペア1と、容量C1,C2と、それらを介して入力信号が与えられるnMOSトランジスタペア2と、nMOSトランジスタペア2のゲート・ドレイン間に設けられたスイッチS1,S2と、で構成される2組のプシュプル型CMOS反転増幅器による差動増幅回路において、nMOSトランジスタペア2の共通ソースとGNDの間にゲートが出力端子Vom,Vopに接続されたnMOSトランジスタM5,M6を設ける。

(もっと読む)

増幅回路、集積回路装置及び電子機器

【課題】特性が安定し、増幅効率の良い増幅回路、集積回路装置及び電子機器等を提供すること。

【解決手段】増幅回路は、出力ノードNPに増幅信号VPを出力する増幅用トランジスター10と、インダクターLA及びキャパシターCA、CBにより構成され、インダクターのインダクタンス値及びキャパシターのキャパシタンス値の少なくとも一方が可変に設定されるLC負荷回路20と、増幅信号VPの電圧振幅を検出する振幅検出回路30と、振幅検出回路30の検出結果に基づいてインダクタンス値及びキャパシタンス値の少なくとも一方を設定し、増幅信号VPの電圧振幅値を極大値に近づける制御を行う制御回路40とを含む。

(もっと読む)

半導体装置及びオフセット補正方法

【課題】コンパレータの比較速度の悪化や消費電力の増加を抑えて入力信号に加わるオフセットを補正する。

【解決手段】比較回路部11において、比較対象の2つの差動入力信号VIP,VIMを入力するトランジスタNM1,NM2のバックゲートBG1,BG2のそれぞれに可変容量C1,C2と抵抗R1,R2を並列に接続し、可変容量C1,C2と抵抗R1,R2の少なくとも一方の値を可変することで差動入力信号VIP,VIMに加わるオフセットを補正する。

(もっと読む)

差動増幅回路

【課題】市販の差動アンプICを用いる差動増幅回路は、入力インピーダンスを高くするために前段にバッファが必要であり、また一端を基準電圧に固定すると入力信号に応じたコモンモード電圧が発生する。本発明は構成が簡単であり、かつコモンモード電圧が発生しない差動増幅回路を提供することを目的にする。

【解決手段】差動信号が入力され、差動出力信号を出力する差動入出力部41と、この差動入出力部41の出力電圧を分圧した電圧と基準電圧の差電圧を前記差動入出力部41に帰還する差動アンプ44を具備した。構成が簡単であり、かつコモンモード電圧が発生しない。

(もっと読む)

デューティサイクル補正を行う方法

【課題】不均一なデューティサイクルを有する入力信号のデューティサイクル補正を行う方法を提供する。

【解決手段】不均一なデューティサイクルを有する入力信号をコンデンサ・デジェネレイティング差動対回路に入力し、前記回路内の1つ以上のコンデンサの両端に、前記入力信号のデューティサイクルの正の部分と負の部分との継続時間の差を表わす直流電圧を形成し、差動対回路のスイッチング動作を通じてデューティサイクルを有する出力信号を形成し、それによって出力信号のデューティサイクルの正の部分と負の部分の継続時間が、入力信号とスイッチングレベルとの交差点により規定される。必要に応じて、出力信号のデューティサイクルが少なくとも実質的に均一になるまで、信号(およびスイッチングレベル)が調整される。

(もっと読む)

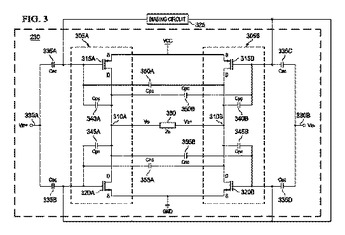

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

光受信器

【課題】帰還抵抗を極端に大きくすることなく、高感度に広帯域な動作を実現できる光受信器を提供する。

【解決手段】同一極性方向に直列接続された2個の受光素子より構成されたバランスドフォトダイオードと、このバランスドフォトダイオードの出力信号が入力されるチェリーホッパー型増幅部と、このチェリーホッパー型増幅部を構成している差動入力ペアトランジスタからのそれぞれの出力信号をレベルシフトするエミッタフォロワ部と、このエミッタフォロワ部の出力信号を前記チェリーホッパー型増幅部の各入力端子に帰還する経路に設けられた第1および第2の帰還抵抗と、この第2の帰還抵抗と前記チェリーホッパー型増幅部を構成している差動増幅回路の一方のトランジスタのベースに接続されている第1のコンデンサとを有することを特徴とする。

(もっと読む)

可変利得増幅回路、撮像装置

【課題】チップ間の特性ばらつきを抑え、消費電力を低減することが可能な小型の対数増幅回路を提供する。

【解決手段】

増幅器30と、

可変利得増幅回路の入力端子VI(N)と増幅器30の入力端子AMP_IN(N)との間に接続された入力容量3Nと、入力端子AMP_IN(N)と増幅器30の出力端子VO(N)との間に接続された帰還容量2Nとを備え、入力容量3N及び帰還容量2Nは、入力端子AMP_IN(N)と入力端子VI(N)との間に接続された第一の容量(容量73a)と、入力端子AMP_IN(N)と出力端子VO(N)との間に第一の容量に対して並列に接続された第二の容量(72a)と、入力端子VI(N)及び出力端子VO(N)の各々と前記第二の容量との間に設けられ、前記第二の容量と入力端子VI(N)とを接続した状態及び前記第二の容量と出力端子VO(N)とを接続した状態を切り替えるスイッチ(S1)とを含む容量可変用ブロック70aを少なくとも1つ有するラダー容量で構成されている。

(もっと読む)

差動増幅回路および無線受信機

【課題】消費電流の増大を抑制しつつ、差動増幅回路の線形性と利得の両立を図る。

【解決手段】差動信号Vin、Vinbの一方が入力されるソースフォロア回路を構成する電界効果トランジスタM11と、ソースフォロア回路に直列接続され、差動信号Vin、Vinbの他方が入力されるソース接地回路を構成する電界効果トランジスタM12とを備える。

(もっと読む)

半導体集積回路およびその調整方法

【課題】一対の信号線に差動の信号を出力する差動出力駆動回路を備える半導体集積回路において、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようにする。

【解決手段】一対の信号線4a,4bのそれぞれとGNDとの間に出力容量Ca,Cbを備えるとともに、それぞれの信号線4a,4bに直列に第1の抵抗R1a,R1bを介在し、かつ前記信号線4a,4bを第2の抵抗R2a,R2bによって電源電位にプルアップする。そして、該半導体集積回路1を基板に実装した後に測定された立ち上がり時間と立ち下がり時間とに応じて、抵抗値調整回路Aa,Abが、前記抵抗R1a,R2a;R1b,R2bの抵抗値をそれぞれ調整する。したがって、立ち上がり時間と立ち下がり時間とをそれぞれ独立に調整できるようになり、それらの対称性を維持しなければならないような規格に対しても対応可能となる。

(もっと読む)

61 - 80 / 395

[ Back to top ]