Fターム[5J500DP02]の内容

Fターム[5J500DP02]に分類される特許

21 - 40 / 395

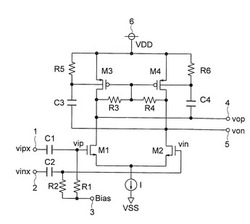

増幅回路

【課題】動作電流を減少させることが可能となり、低消費電力化が可能となる増幅回路の提供。

【解決手段】この発明は、差動対を構成し、互いに逆相の差動入力信号vipx、vinxが入力されるMOSトランジスM1、M2と、MOSトランジスタM1、M2のそれぞれの負荷となるMOSトランジスタM3、M4とを備えている。また、MOSトランジスタM3のバルクには、抵抗R5を介してバイアス電圧が印加されるととともに、キャパシタC3を介して反転出力信号vonが入力される。さらに、MOSトランジスタM4のバルクには、抵抗R6を介してバイアス電圧が印加されるととともに、キャパシタC4を介して出力信号vopが入力される。

(もっと読む)

差動信号発生回路および電圧制御ゲイン可変増幅器

【課題】電圧制御によりゲイン調整を行うゲイン可変増幅器制御用の制御電圧を、基準電圧を用いることなく生成し、電圧制御ゲイン可変増幅器全体の小型化および消費電力の削減を図る。

【解決手段】ゲイン可変増幅器制御回路を構成する差動対として、nチャネル型トランジスタTR11とpチャネル型トランジスタTR12とを用い、共通のゲイン制御電圧S1をこれらトランジスタTR11およびTR12のゲートに供給する。各トランジスタTR11、TR12を流れる電流は、ゲイン制御電圧S1が増加するにつれて一方は増加し、他方は減少する特性となり、基準電圧を用いたゲイン可変増幅器制御回路と同一特性のゲイン可変増幅器制御電圧を得ることができる。よって、基準電圧発生回路を設ける必要がないため、装置全体の小型化および消費電力の削減を図ることができる。

(もっと読む)

利得可変差動増幅回路

【課題】広いダイナミックレンジを確保しつつ利得を変化させることが可能な利得可変差動増幅回路を提供すること。

【解決手段】この利得可変差動増幅回路12は、差動対トランジスタQ1,Q2,Q3,Q4とそれらのトランジスタのそれぞれのコレクタに接続された負荷抵抗14,15,18,19とそれらのトランジスタのエミッタに共通に接続された電流源16,20とをそれぞれ含む差動増幅回路17,21を有し、次段差動増幅回路21の出力を、帰還トランジスタQ5,Q6を介して初段差動増幅回路17に帰還させる利得可変差動増幅回路において、該初段差動対トランジスタQ1,Q2を流れるべき電流を分岐させる電流分岐回路部12Cと、差動対トランジスタQ1,Q2に電流を供給する電流供給回路部12Bとを備える。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

差動出力バッファ

【課題】送信状態とスタンバイ状態との間の遷移時間の増大を抑制しつつ、電流の変動を低減する。

【解決手段】メインドライバ1は、差動信号PREP、PRENのレベル変換を行い、バイパス回路2は、メインドライバ1の動作状態とスタンバイ状態との間の遷移時に高電源電位VDDから低電源電位VSSに流れる電流I5の変化量が一定の範囲内に収まるようにメインドライバ1に流れる電流I5をバイパスさせる。

(もっと読む)

演算増幅回路

【課題】セトリング速度を向上させる。

【解決手段】差動入力信号を増幅する差動対(M1、M2、M19)と、差動対の一方および他方の出力端にそれぞれ接続される一方および他方のカスコード増幅器対(M9、M10)と、カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の一方および他方の出力端にそれぞれドレインを接続するソース接地の第1のMOSトランジスタ対(M11a、M12a)と、を備える。カスコード増幅器対の一方および他方の出力端にそれぞれゲートを接続し、差動対の他方および一方の出力端にそれぞれドレインを接続する、第1のMOSトランジスタ対と同一の導電型であるソース接地の第2のMOSトランジスタ対(M3a、M4a)をさらに備える。

(もっと読む)

受信回路並びにそれを備えた半導体装置及び情報処理システム

【課題】 本発明は、低速信号よりも高速信号を増幅し、かつ、消費電力を抑える受信回路並びにそれを備えた半導体装置及び情報処理システムを実現することを目的とする。

【解決手段】 本発明の受信回路並びにそれを備えた半導体装置及び情報処理システムは、第1の増幅器と、第1の増幅器よりもカットオフ周波数の低い第2の増幅器とを有し、第1の増幅器及び第2の増幅器に受信信号を入力し、第1の増幅器の出力から第2の増幅器の出力を減じて出力する。

(もっと読む)

集積フィルタを備えた増幅器

【課題】良好な雑音性能を有しかつ大きい干渉信号に対処できる増幅器を提供する。

【解決手段】集積フィルタを備えた増幅器320b(例えば,LNA)は利得ステージ330、フィルタ・ステージ340およびバッファ・ステージ350を含んでいてもよい。利得ステージは、入力信号に対して信号増幅を提供する。フィルタ・ステージは、入力信号に対してフィルタリングを提供する。バッファ・ステージは、フィルタ・ステージからのフィルタされた信号をバッファする。増幅器は、第2のフィルタ・ステージ360及び第2のバッファ・ステージ370をさらに含んでいてもよい。

(もっと読む)

演算増幅回路

【課題】電流源の誤差やカレントミラーのミラー精度の誤差による同相出力電圧の出力オフセット電圧を補正し、より正確に同相出力電圧を制御することができる演算増幅回路を提供する。

【解決手段】入力切替回路14がコモンモード参照電圧を選択してコモンモード基準電圧として出力したときの全差動増幅回路10の同相出力電圧をコモンモード検出回路11が検出した後、S/H回路12がコモンモード検出回路11の出力のサンプル及びホールドを行い、演算回路13がS/H回路12の出力とコモンモード参照電圧とのずれ量とコモンモード参照電圧とに基づく電圧を出力し、入力切替回路14が演算回路13の出力を選択してコモンモード基準電圧として出力する。

(もっと読む)

入れ子状のトランスインピーダンス増幅器

【課題】光ファイバ受信器やハードディスクドライブ向けに、大きい帯域幅及び高利得TIAを提供する。

【解決手段】入れ子状のトランスインピーダンス増幅器(TIA)回路は、入力及び出力を有する0次のTIAと、第1の演算増幅器(オペアンプ)と、を備えている。オペアンプは、0次のTIAの出力に接続する入力と、該入力によって駆動される第1のトランジスタと、第1のバイアス電圧によって駆動され且つ上記第1のトランジスタに接続する第2のトランジスタと、第2のトランジスタに接続する第1の電流源と、第1のトランジスタと第2のトランジスタの間のノードに存在する出力と、を備えている。

(もっと読む)

半導体スイッチ

【課題】端子切替時の応答特性を改善した半導体スイッチを提供する。

【解決手段】電源回路部は、正の電源電位よりも高い第1の電位と、負の第2の電位と、を生成する。駆動回路部は、前記電源回路部に接続され、端子切替信号に応じて前記第1の電位をハイレベルとし前記第2の電位をローレベルとする制御信号を出力する。スイッチ部は、制御信号を入力して端子間の接続を切り替える。前記駆動回路部は、第1と、第2のレベルシフタと、第1の回路と、を有する。前記第2のレベルシフタは、前記第1のレベルシフタの出力電位に応じて互いに排他的にオンする第2のハイサイドスイッチと第2のローサイドスイッチとを有し、前記制御信号を出力する。前記第1の回路は、前記端子切替信号に応じて、前記制御信号の電位の変化よりも前に前記第2のローサイドスイッチに前記電源電位を供給し、または前記ハイサイドスイッチに前記接地電位を供給する。

(もっと読む)

低歪み可変利得増幅器(VGA)

【課題】非対称な信号の非対称性を補正する。

【解決手段】第1抵抗は、増幅器の入力ノード及び出力ノードの間に接続され、入力ノードは非対称信号を受信する。第2抵抗は、増幅器の入力ノードに接続される。第2抵抗は、線形レジスタを含む。第3抵抗は、第2抵抗に接続される。出力ノードにおける非対称信号を補正するべく、増幅器によって提供される非対称補正量を調整するように第3抵抗を変化させる。非対称補正量は、第1抵抗及び第2抵抗と第3抵抗との組み合わせの関数である。

(もっと読む)

スイッチトキャパシタ積分および加算回路

【課題】単一の演算増幅器を使用して積分器と加算器の両方を実現するスイッチトキャパシタ回路を提供する。

【解決手段】1つの入力信号は、(1)1つまたは複数の積分ブランチと、(2)1つまたは複数の第1の加算ブランチとを介して演算増幅器の入力に送られる。第2の入力信号は、1つまたは複数の第2の加算ブランチを介して演算増幅器の入力に送られる。ブランチの各々は、キャパシタと、異なるクロック位相によって制御されるいくつかのスイッチとを含む。スイッチトキャパシタ回路はシングルエンドまたは差動とすることができる。

(もっと読む)

増幅回路

【課題】オフセットの環境変動を小さくする。

【解決手段】第1の温度特性を備えた第1の電圧信号を出力する第1の電圧源と、入力電圧信号を第1のバイアス信号に応じて増幅し、第2の電圧信号として出力するプリアンプと、前記プリアンプのレプリカ回路構成を備え、入力した所定の電圧を前記第1のバイアス信号に応じて増幅し、コモン電圧信号として出力するレプリカプリアンプと、前記第1の電圧信号と、前記コモン電圧信号との電圧差から前記第1のバイアス信号を生成する誤差アンプと、前記第2の電圧信号に応じた出力電圧信号を出力し、オフセット制御信号に応じて、前記出力電圧信号のオフセット電圧を調整する増幅器と、を有する増幅回路。

(もっと読む)

半導体集積回路

【課題】DCオフセットキャンセル回路の回路規模と消費電力とを低減する。

【解決手段】差動増幅器5の非反転出力端子と反転出力端子にDCオフセットキャンセル回路51の差動入力端子が接続され、キャンセル回路51の出力信号は差動増幅器5の出力DCオフセット電圧を低減する。回路51はオンチップローパスフィルタ51と直流制御増幅器512を有し、フィルタ511は第1定電流源CS1、差動対の第1と第2のトランジスタ素子Mp1、Mp2、オンチップ容量C1を含む。第1定電流源CS1は素子Mp1、Mp2の共通電極に接続され、回路51の差動入力端子Vinp、Viinは素子Mp1、Mp2の制御入力電極に接続される。オンチップ容量C1の一端と他端に素子Mp1、Mp2の出力電極とが接続され、直流制御増幅器512は容量C1の両端の電圧に直流的に応答する。

(もっと読む)

広帯域増幅器

【課題】高い周波数までの二次歪成分を除去し、出力電流信号の線形性を向上させることができ、二次歪耐性(IIP2)を向上させることができる広帯域増幅器を実現する。

【解決手段】第1及び第2のMOSトランジスタQ1,Q2による差動対が発生する二次歪成分電流と逆極性の電流信号を差動対の負荷電流源となる第3及び第4のMOSトランジスタQ3,Q4によって発生し、逆極性の二次歪電流を相互に打ち消し合うように作用させて線形性を向上させ、更に、第1及び第2のMOSトランジスタQ1,Q2の入力へのバイアスを設定する第1のバイアス回路を第1及び第2のMOSトランジスタのドレイン電流が流れるように、且つ、該ドレイン電流をゲート電圧で二回微分した成分の絶対値が極小となるようなバイアス値を得るようにし、且つ、第3及び第4のMOSトランジスタQ3,Q4のサイズを二次歪み成分が主成分である電流を生成するように設定する。

(もっと読む)

送信装置および送受信システム

【課題】受信装置の終端抵抗器の抵抗値がばらついている場合であっても安定した通信を行うことができる送信装置を提供する。

【解決手段】送信装置10Aは、第1トランジスタ11、第2トランジスタ12、電流源13、送信回路14、差演算部15および電流調整部16を備える。トランジスタ11,12は差動対を構成している。差演算部15は、トランジスタ11,12のうちの一方がオン状態で他方がオフ状態であるときの第1出力端10aおよび第2出力端10bそれぞれからの出力電圧値を入力して、これら2つの出力電圧値の差(対象電圧)を求める。電流調整部16は、この対象電圧を入力するとともに、参照電圧入力端10dに入力された参照電圧を入力して、参照電圧に基づいて対象電圧を評価し、その評価結果に基づいて、対象電圧が目標値または目標範囲内となるように電流源13の出力電流値を調整する。

(もっと読む)

スイッチトキャパシタ回路

【課題】エスティメートフェーズとレベルシフトフェーズとで、レベルシフト用コンデンサCca、Ccbを、全差動演算増幅器AMP2の出力のサンプルと全差動演算増幅器のAMP2位相補償とに兼用する方式のCLS技術を適用したスイッチトキャパシタ回路100において、入出力コモン電圧の変動を抑止するこれにより、同相入力レンジの大きさに関する要求水準を低減させて、十分な低電圧化が図られて消費電力が低減されたスイッチトキャパシタ回路を実現する。

【解決手段】エスティメートフェーズからレベルシフトフェーズへの移行に際して、複数の全差動演算増幅器AMP1、AMP2のうちの初段の全差動演算増幅器および最後段の全差動演算増幅器の各出力コモン電圧が等しくなるように保持する出力コモン電圧保持回路110を備えた。

(もっと読む)

金属検出システム作動方法及び金属検出システム

【課題】2つ以上の送信周波数を使用する金属検出システムを提供する。

【解決手段】少なくとも2つの送信周波数グループから選択される送信周波数を有する送信信号を生成する送信装置3と接続される送信コイル4と、受信装置5に含まれる少なくとも1つの増幅装置14,15の信号入力へ出力信号を提供し、出力信号が、システムが平衡状態にあるように相互に相殺する第1及び第2の受信コイル6,7とを備えた、平衡コイルシステムを含む金属検出システム1を作動させる。制御装置16が、少なくとも1つの増幅装置14,15の信号入力と接続される少なくとも1つの制御可能インピーダンス装置12,13の制御入力に提供される制御信号を送信装置3の送信周波数に従って生成し、送信周波数が増減されるとき、インピーダンス値が増減されるような方法で制御信号が、制御可能インピーダンス装置12,13のインピーダンス値を制御する。

(もっと読む)

21 - 40 / 395

[ Back to top ]