Fターム[5K047AA15]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 構成簡単化 (321)

Fターム[5K047AA15]の下位に属するFターム

回路規模の低減 (74)

Fターム[5K047AA15]に分類される特許

1 - 20 / 247

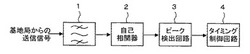

フレーム同期回路およびフレーム同期方法

【課題】ICH用トレーニングデータの影響を低減させることができるとともに、規模を小型化することができるフレーム同期回路を得る。

【解決手段】周波数が異なる複数のサブチャネルに別々に複数のPRUのそれぞれが重畳されたダウンリンク信号が基地局から定期的に送信され、複数のPRUの中からCCCH用トレーニングデータを用いてダウンリンク信号に同期するフレーム同期回路であって、ダウンリンク信号が入力され、CCCH用PRUが重畳されたサブチャネルの周波数のみを通過帯域とするバンドパスフィルタ1と、バンドパスフィルタ1を通過するダウンリンク信号を用いて自己相関演算を行う自己相関器2と、自己相関器2の出力が最大となるタイミングを検出して、このタイミングに追従するタイミング信号を生成するピーク検出回路3と、タイミング信号に同期するタイミング制御回路4とを備えている。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

PONシステムのCDR回路およびCDR回路におけるパルス幅歪自己検出方法とパルス幅歪自己補償方法

【課題】簡易な入力データパルス幅歪の自己検出、自己補償機能を備えたPONシステムのCDR回路を提供する。

【解決手段】CDR機能手段での入力データのエッジ位相の検出結果に対するエッジ位相ヒストグラムを作成する手段8、CDR機能手段でのN位相クロック生成結果をシステムクロック速度レベルまで分周したクロックをシステムクロックから生成したm位相クロックにてサンプリングし得られた結果から分周クロックのエッジ位相を検出してクロックヒストグラムを作成する手段11−13、クロックヒストグラムからN位相クロックのジッタ量を検出し、またエッジ位相ヒストグラムからクロックヒストグラムを減算し入力データに重畳するジッタ成分のみ抽出し重畳するジッタ成分から入力データの理想的な1ビットパルス幅とことなるピークをパルス幅歪量として判断し検出する検出手段9を含む。

(もっと読む)

マルチバンド無線通信システムおよび端末装置

【課題】時間フレーム同期処理に要する演算量を削減し、時間フレーム同期に要する時間を低減することが可能なマルチバンド無線通信システムを得ること。

【解決手段】不連続な複数の周波数帯を用いて通信を行う基地局装置および端末装置から構成されるマルチバンド無線通信システムであって、前記基地局装置は、所定の周波数帯の時間フレームと他の周波数帯の時間フレームとのタイミング差の情報を生成し、当該タイミング差の情報を当該所定の周波数帯を用いて前記端末装置に送信し、前記端末装置は、前記所定の周波数帯において前記基地局装置と時間フレームの同期を確立し、さらに、前記基地局装置から受信したタイミング差の情報に基づいて、前記他の周波数帯において前記基地局装置と時間フレームの同期を確立する。

(もっと読む)

通信方式、受信装置及び基地局装置

【課題】通信フレーム中の各スロットに位相だけが異なる既知データが含められた信号を通信する通信方式に関し、同期制御を簡易に行えるようにする技術を提案する。

【解決手段】スロット分割部1により、LTE上り信号の受信データを分割し、相関演算部2及び相関パワー算出部4により、前記分割によって得られる各スロットデータについて、基準データ保持部3に保持されている基準データとの相関(パワー)を算出し、ピーク位置検出部5により、前記検出した相関がピークとなる相関ピーク位置を検出し、ピーク位置比較部6及びスロット位置特定部8により、前記検出した各々の相関ピーク位置を理論ピーク位置保持部7に保持されている理論上の相関ピーク位置と比較して、各スロットデータの通信フレームにおけるスロット位置を特定し、同期調整部9により、前記特定したスロット位置に従って同期制御を行う。

(もっと読む)

非同期吸収回路、画像処理装置及びプログラム

【課題】画像1ライン分よりも少ない記憶容量の複数のシングルポートメモリを用いて非同期吸収を行うことができる非同期吸収回路、画像処理装置及びプログラムを提供することを課題とする。

【解決手段】少なくとも画像1ライン分よりも少ない記憶容量の複数の記憶手段への入力データの書き込み動作を行う書き込み動作手段と、記憶手段からの出力データの読み出し動作を行う読み出し動作手段と、書き込み及び読み出しの対象となる記憶手段を切り替える切り替え手段と、画像1ライン分の入力データを複数に分けたブロックデータが記憶手段に振り分けられるタイミングに基づき、切り替え手段による記憶手段の切り替えを制御する切り替え制御手段と、入力データのクロック信号と出力データのクロック信号との非同期吸収を行う非同期吸収手段とを有することにより上記課題を解決する。

(もっと読む)

音声信号中継回路および音声信号中継方法

【課題】音声信号生成回路をより安定して動作させることが可能な音声信号中継回路等を提供すること。

【解決手段】音声信号中継回路100が、イネーブル信号入力部110と、搬送クロックを入力する搬送クロック入力部150と、サンプリングレートクロックを入力するサンプリングレートクロック入力部160と、音声信号を入力する音声信号入力部170と、搬送クロックを音声信号生成回路30に出力する搬送クロック出力部150と、サンプリングレートクロックを音声信号生成回路30に出力するサンプリングレートクロック出力部161と、音声信号を音声信号再生回路50に出力する音声信号出力部171と、擬似搬送クロックを生成する擬似搬送クロック生成部130と、擬似サンプリングレートクロックを生成する擬似サンプリングレートクロック生成部140を含んで構成される。

(もっと読む)

遷移検出回路

【課題】

簡潔な構成でコード信号の遷移を検出する遷移検出回路を提供する。

【解決手段】

1ビットずつ遷移するグレイコードの遷移を検出する検出回路において、グレイコードのビットに含まれる1の個数が偶数であるか奇数であるかによって変化する信号を出力する組み合わせ論理回路と、組み合わせ論理回路の出力が変化したときに有効となる遷移検出信号を生成する比較回路とを備える。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

通信装置、制御信号生成方法、シャッターメガネ、及び通信システム

【課題】 受信データから得られる基準タイミングに基づいた表示装置等の被制御装置の制御を遅延なくかつ低消費電力で可能にする通信装置、その被制御装置を制御するための制御信号生成方法、受信データから得られる基準タイミングに基づいたシャッターの開閉を遅延なくかつ低消費電力で可能にするシャッターメガネ、及び基準タイミングを表すデータの送受信を遅延なくかつ低消費電力で可能にする通信システムを提供する。

【解決手段】 間欠的に到来するデータ内に所定の基準タイミング信号パターンが存在するか否かを識別するタイミング信号識別手段と、タイミング信号識別手段によって所定の基準タイミング信号パターンの存在が識別された場合に被制御装置に対する制御信号を生成する制御信号生成手段と、通信装置の制御を司る制御手段と、を備える。

(もっと読む)

同期制御システム

【課題】マスタとスレーブを有し時計により同期する同期システムを得る。

【解決手段】生成部と送受信時間の計測部を有するマスタ11、第1折返し部を含みリセットを受信すると第1時刻に動作する第1スレーブ12、第2折返し部を含みリセットを受信すると第2時刻に動作する第2スレーブ13、第1信号を第1スレーブへ送信する第1ケーブル、それと等長で第1信号をマスタへ送信する第2ケーブル、第2信号を第2スレーブへ送信する第3ケーブル、それと等長で第2信号をマスタへ送信する第4ケーブルを備え、計測部は第1信号が第1信号折返し部を経て受信される時間の半分の第1時間と第2信号が第2信号折返し部を経て受信される時間の半分の第2時間を算出し、生成部は到達時間の中で第2時間が最長の場合は第2時刻を0に第2時間と第1時間の差を第1時刻に設定し、第1時間が最長の場合は第1時刻を0に第1時間と第2時間の差を第2時刻に設定する。

(もっと読む)

データ転送回路

【課題】異なるクロックのデータ転送を行うときに、パルスストレッチ回路を用いることなく、不正な値が転送されないようにすることを目的とする。

【解決手段】クロックCLK−Aで動作する入力側回路部2とクロックCLK−Bで動作する出力側回路部3とを有し、データData−Aを出力データData−Bとして出力させる回路であって、入力側回路部2に設けられ、入力データData−Aを入力して中間データMidとして出力する入力側フリップフロップ4と、出力側回路3に設けられ、中間データMidを入力して出力データData−Bとして出力させる出力側フリップフロップ5と、出力側フリップフロップ5が中間データMidを入力するときには、中間データMidを固定値として出力するように入力側フリップフロップ4を制御する制御部6と、を備えたことを特徴とする。

(もっと読む)

CDR回路および受信回路

【課題】参照クロックが不要なインタポレータ方式のCDR回路を小面積で実現することができる技術を提供する。

【解決手段】CDR回路101において、再生クロックのエッジの近傍と遠方にある伝送データのエッジの個数を計測するデータエッジ位置計測回路117と、伝送データのエッジの近傍と遠方にある再生クロックのエッジの個数を計測するクロックエッジ位置計測回路118とを含み、データエッジ位置計測回路117の計測結果とクロックエッジ位置計測回路118の計測結果に応じて、再生クロックの周波数を調整する周波数調整回路116を有する。エッジの近傍と遠方の判定には、CCL回路の最小入力振幅を制御することで実現している。

(もっと読む)

位相調整装置

【課題】デジタル画像データとクロックとの位相を調整する場合に、投影画像による目視判断などを行わないで自動的に調整する。

【解決手段】データセレクタ104は、遅延回路101から並列に供給される互いに所定時間遅延時間の異なる複数の遅延クロックのうち、セレクト端子に供給されるnビットカウンタ値に応じた1種類の遅延時間の遅延クロックを選択する。ラッチ回路105は、デジタルデータをデータセレクタ104から出力された遅延クロックの立ち上がり及び立ち下りでラッチする。4段シフトレジスタ106は、ラッチ回路105からのデジタルデータを、データセレクタ104から出力された遅延クロックをシフトクロックとして4段シフトする。コンパレータ107は、4段シフトレジスタ106の入力デジタルデータと出力デジタルデータとを比較し、比較結果が一致する場合は、ラッチが正しくできていると判断する。

(もっと読む)

送信回路

【課題】出力するシリアルデータのビット位置を容易に特定することが可能な送信回路を得ること。

【解決手段】本発明にかかる送信回路は、シリアルクロックと当該シリアルクロックに同期したシリアルデータとを出力する送信回路1aであって、シリアルデータのビット位置を特定するためのパルス信号を、所定の間隔で生成し出力するシリアルデータ計数部3a、を備え、その回数を数えることにより、シリアルデータのビット位置を容易に特定可能な構成とした。

(もっと読む)

データ送信装置及びデータ転送装置並びにデータ転送方法

【課題】ビット欠けが発生せずデータ受信装置に適した周波数でシリアルデータ転送できるようにする。

【解決手段】転送の一区間を繰り返して示すデータ転送サイクル信号5を受け、このデータ転送サイクル信号5からストローブパルスを繰り返して発生しこのストローブパルスにより連続してデータを受信するデータ受信装置に向けて、送信クロックに同期させてデータ転送サイクル信号5を送信するとともに、このデータ転送サイクル信号5に同期させてデータを連続して送信するデータ送信装置1において、データ送信装置1は、制御部2により、データ受信装置の受信クロックの周波数情報に基づいて、データを転送する一区間を示すデータ転送サイクル内に予め定めた数以上の受信クロックのクロック数が入るようにデータ転送サイクル幅4を決定し、送信部3により、制御部2が決定したデータ転送サイクル幅4を有するデータ転送の一区間内で一のデータを送信する。

(もっと読む)

受信回路、送信回路、通信システム、及び通信システムの送信設定方法

【課題】信号遷移発生用の符号化を用いることなくデータとクロックとを1つの信号に纏めて送受信可能な送信回路及び受信回路を提供する。

【解決手段】送信回路は、データ信号とクロック信号とを重み付け加算することにより生成した信号を送信する。また受信回路は、受信した第1の信号の信号遷移からクロック信号を抽出するクロック抽出回路と、抽出されたクロック信号を第1の信号から減算することにより第2の信号を生成する減算回路と、抽出されたクロック信号に応じたタイミングにおいて第2の信号をデータ判定するデータ判定回路とを含む。

(もっと読む)

オーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法

【課題】主な目的は、消費電流を減少させることにあり、副次的な目的は、オーバーサンプリング間隔を切り替えることができるオーバーサンプリング回路及びそれを用いたシリアル通信装置及びシリアル通信方法を提供する。

【解決手段】シリアルデータを所定時間だけ遅延させた多相シリアルデータを生成する生成部と、その多相シリアルデータを多相クロックでオーバーサンプリングするオーバーサンプリング部と、を備えた。

(もっと読む)

クロックド・シリアル・インタフェース

【課題】様々な波形のコントロール信号を生成し出力できるクロックド・シリアル・インタフェース(CSI)を提供する。

【解決手段】コントロール信号の波形を決定するパターンデータが書換可能に格納される複数のシフトレジスタと、これらシフトレジスタ内のパターンデータに応じてコントロール信号を生成する生成手段と、を備える。具体的には、CSI60は、3つのシフトレジスタ81,82,83を有し、これらシフトレジスタ内のパターンデータに応じた波形のコントロール信号を生成し出力する。

(もっと読む)

1 - 20 / 247

[ Back to top ]