Fターム[5K047MM48]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | PLL (330) | デジタルPLL (20)

Fターム[5K047MM48]に分類される特許

1 - 20 / 20

CDR回路、受信装置、および送受信システム

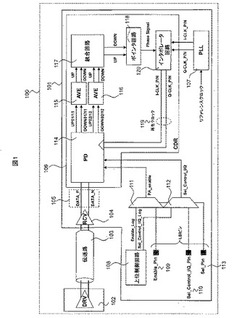

【課題】非線形位相比較器を用いたCDR回路、受信装置、および送受信システムの再生クロックの位相追従精度を向上させる。

【解決手段】CDR回路106、受信装置101、および送受信システム100は、受信データ105および再生クロック119が入力される非線形位相比較器の出力に、受信データに対する、再生クロックに対して位相差を有するクロックの遅れまたは進みに応じて重み付けをし、重み付けされた出力に基づいて再生クロックの位相を調整する。

(もっと読む)

シリアル・データ通信装置のDPLL回路

【課題】PLCで設計・構成するシリアル・データ通信の高速化を図ることができ、しかも受信データのジッタ許容範囲を明確にできる。

【解決手段】DPLL回路10のうち、データシフト回路DS1〜DS3は受信データからソースクロックCLKで同期を取った複数のシリアル・データを生成する。排他的論理和回路EX_ORは一対のシリアル・データから受信データの変化点を検出する。カウンタDPLCNTは、最大カウント値nが設定され、変化点から次の変化点までをソースクロックをカウントする。一致判定回路ANDはカウンタのカウント値が予め設定したカウント値n/2に一致したときに受信クロックとして出力する。ハイレベル・データ・リンク・コントローラ・モジュール(HDLC−IP)20は、受信クロックを使って受信データ(シリアル・データ)の転送制御を行う。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

DLLを共用してサンプリング位相設定を行うホストコントローラ

【課題】VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラにおいて、ピン数・消費電力を減らす。

【解決手段】ホストコントローラは、VDSモード及びFDSモードにて、受信データのサンプリングを行うホストコントローラであって、VDS時の位相シフト量を保持するVDS位相レジスタと、FDS時の位相シフト量を保持するFDS位相レジスタと、VDSとFDSのどちらのモードでデータサンプリングを行うかを示すモード設定部と、前記モード設定部の設定値に応じて、前記VDS位相設定レジスタ及びFDS位相設定レジスタの一方に設定されている位相シフト量を選択し、サンプリング位置として提供するサンプリング位置選択部と、前記サンプリング位置設定部から提供されるシフト量に応じて、入力クロック信号の位相をシフトしサンプリングクロックとして提供するクロック位相シフト部とを具備する。

(もっと読む)

瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

(もっと読む)

マルチブランチ受信機のためのシンボルタイミング回復技術

受信機のシンボルタイミング回復機能に対して、第1の受信信号(10)によって第1の受信ブランチと、及び、第2の受信信号(20)によって第2の受信ブランチと結合された信号コンバイナ(465)が提供される。信号コンバイナ(465)は、第1の受信信号(10)及び第2の受信信号(20)に基づいて合成信号(C)を生成する。さらに、共通タイミングエラー検出器(470C)が提供される。共通タイミングエラー検出器(470C)は信号コンバイナ(465)と結合されると共に、共通タイミングエラー信号(TEC)を合成信号に基づいて生成するように構成される。第1の受信信号(10)に対応する第1のデジタルシンボルタイミングと、第2の受信信号(20)に対応する第2のデジタルシンボルタイミングとが共通タイミングエラー信号(TEC)に基づいて回復される。  (もっと読む)

(もっと読む)

タイミング回復のためのサイクルスリップ検出

【課題】タイミング回復のためのサイクルスリップ検出の提供。

【解決手段】タイミング回復のために制御ループ中のループフィルタLFの出力信号を使用するステップと、前記フィルタ処理後のタイミング誤差信号から平均タイミング誤差値を生成するステップと、第1の閾値を超えるサンプルの隣接するブロックの平均タイミング誤差値の変化を累積するステップとを含む。第2の閾値を超える隣接するブロックの累積した平均タイミング誤差変化がサイクルスリップとして表明され、サイクルスリップの数が許容閾値である第3の閾値によって決定される。さらに、先入れ先出しメモリFIFOがサンプル挿入または削除のために設けられ、それは、サンプル挿入またはサンプル削除が向上した信頼性を伴ってサンプル領域で行われ、サイクルスリップ検出の改善された方法が雑音および不適切に選ばれたタイミングループパラメータに対する頑健性の増強のために推奨される。

(もっと読む)

映像信号処理装置

【課題】PLL回路での位相ロック可否を判断し、判断結果に応じて入力アナログ映像信号のサンプリングクロック生成に使用する回路をPLL回路とDLL回路で自動的に切り替え可能な映像信号処理装置を提供する。

【解決手段】アナログ映像信号をA/D変換するAD変換器2と、AD変換器2にクロック信号を供給するクロック信号生成回路8を備え、クロック信号生成回路8は、アナログ映像信号から取得された水平同期信号に基づいて第一クロック信号を生成するPLL回路81と、アナログ映像信号から取得された復号同期信号に基づいて第二クロック信号を生成するDLL回路82と、PLL用位相比較器811の出力に基づいて第一クロック信号または第二クロック信号の何れかを選択して出力するクロック選択部83を備えている。

(もっと読む)

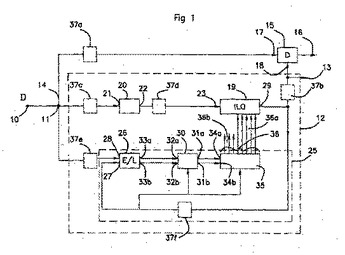

外部制御を必要としないデジタル位相ロックによるクロック抽出装置

本発明は、注入ロック発振器(19)と、デジタル位相検出器(26)を有する位相制御ループ(25)とを備えた、ベースバンドシリアル信号からクロックを抽出する装置に関する。発振器(19)はその周波数の値を制御するデジタル制御入力部(24)を備え、位相制御ループ(25)は、デジタル位相検出器(26)から供給されるデジタル信号の相対値を累算し、発振器(19)用のデジタル形態の制御信号を渡す、カウント回路(30、35)を備える。  (もっと読む)

(もっと読む)

クロックデータリカバリー回路及び通信装置

【課題】LSI化に適し且つ従来のPLLを用いたのと同等の特性を設定できるシリアルデータインターフェースのCDR回路を提供する。

【解決手段】本発明のCDR回路は、所定周波数のクロックの周期T1をN分割したT2時間ずつずらしたN相のクロックを出力する手段、シリアル転送されたデータをT2時間毎にサンプリングする手段、サンプリングしたデータを周期T1毎に第1のNビットパラレルデータに変換する手段、サンプリングしたデータのデータ変化点を示す第2のNビットパラレルデータに変換する手段、及び、第2のNビットパラレルデータを位相情報入力としてシリアルデータのデータ変化点の略中間位置を示す第3のNビットパラレルデータを出力する手段を有し、第3のNビットパラレルデータが示したビット位置と同じ、第1のNビットパラレルデータのビット位置データを復元データとすることを特徴とする。

(もっと読む)

半導体集積回路

【課題】複数のシリアル伝送チャネルで使用するクロックの同期をとる際に、PLL回路から各CDR回路に供給されるクロック配線のレイアウト上の制約を無くし、ジッタの発生の少ない半導体集積回路を提供する。

【解決手段】半導体集積回路は、位相周波数比較回路とチャージポンプとループフィルタと発振回路とを有し、リファレンスクロックに同期した発振出力信号を生成するPLL回路と、発振出力信号とシリアルデータとの位相を調整する複数のCDR回路とを備え、PLL回路はループフィルタから出力された発振回路の発振周波数を制御する制御電圧をディジタルコードに変換し、このディジタルコードをこれら複数のCDR回路に分配する。

(もっと読む)

クロック供給装置

【課題】クロック供給ユニットを複数備え、これらクロック供給ユニットのいずれかを運用系ユニットとし、その他のユニットを待機系ユニットとする冗長構成を有するクロック供給装置において、運用系ユニットを切り替える際に生じる供給クロック信号の位相変動を低減することを目的とする。

【解決手段】自ユニット20が待機系ユニットであるとき、運用系ユニット10から入力される運用系ユニットのDPLL12からのクロック信号を基準として、自ユニット20のDPLL22の出力クロック信号を、運用系ユニット10のDPLL12の出力クロック信号に、所定の位相差を持って同期させるユニット間同期部21、37、39を、クロック供給ユニット10、20に備えて構成する。

(もっと読む)

情報再生処理装置

【課題】イコライザやPLL等の回路をデジタル化し、比較的低い周波数の動作クロックを使用しながら高い位相時間分解能を有するデータ再生、クロック再生回路を提供する。

【解決手段】N本のクロックを生成する多層クロック生成手段8と、2値化手段6と、2値化信号をN本の多層クロックのそれぞれでサンプリングするサンプリング手段10と、N本のサンプリング信号を周期T1毎にNビットのデータとして出力するシリアル−パラレル変換手段11と、波形等価処理を行う等価処理手段5と、前記Nビットの等価データを1ビットシリアルの等価信号に変換するパラレル−シリアル変換手段12と、前記Nビットの等価データからNビットの再生クロックデータを出力するデジタルPLL手段13と、前記Nビットの再生クロックデータを1ビットシリアルの再生クロック信号に変換するパラレル−シリアル変換手段14とから構成される。

(もっと読む)

位相同期ループ回路、位相同期ループ回路のループフィルタゲイン制御方法並びに再生装置

【課題】 ディジタルPLLのループフィルタゲインを自動制御することで、キャプチャ時間の短縮、エラーレートの改善を実現する位相同期ループ回路を提供する。

【解決手段】 ロックモード生成回路29は、イコライザ10からの周波数調整再生信号(e)とビタビ復号器12からのSAM値と補間フィルタ24からのフィルタ出力である同期がとれた再生信号(f)とに基づいて、上記ループフィルタ19の自動調整ゲインKp_auto及びKi_autoを出力する。

(もっと読む)

信号処理装置、信号処理方法

【課題】デジタルPLLのループ遅延の短縮化と、そのデジタルPLLによって位相同期が取られた再生データの高精度化とを両立させる。

【解決手段】ビタビ検出用の位相補間フィルタ9と、PLL8にある位相誤差検出用の位相補間フィルタ81とを設ける。位相オフセット演算器84において位相誤差の積算値である位相オフセット量φに応じて、位相補間フィルタ9および位相補間フィルタ81では、タップ係数が逐次更新されるが、位相補間フィルタ81は、位相補間フィルタ9と比較して、タップ数/ビット幅が小さく設定され、PLL8内のループ遅延時間を短縮する。

(もっと読む)

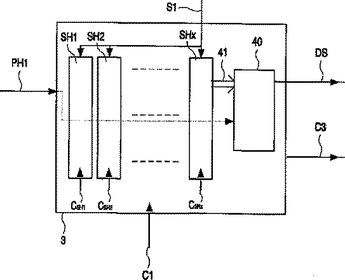

ビット検出装置及び情報再生装置

振幅を有するアナログ信号(AS)を、当該アナログ信号(AS)が導出されるビット列を表すデジタル信号(DS)に変換することができるビット検出装置が開示される。ビット検出装置は、量子化されたアナログ信号とクロック信号C2との間の位相差を検出する位相検出器を有する。位相差は、AD変換器によってサンプリングされる。前記位相差が低周波信号であるので、AD変換器は、比較的遅いレートでサンプリングすることができる。サンプリングされた位相差は、位相信号PH1を出力するデジタルPLLに供給される。位相信号及び量子化されたアナログ信号は、前記デジタル信号(DS)を再現するために用いられる。本発明は、前記ビット判断ユニットが更に、−クロック信号CSH2を用いて前記出力信号S1をサンプリングすることができる少なくとも1つの追加のサンプル及び保持ユニットSH2であって、前記クロック信号CSH2の周波数はクロック信号CSH1の周波数に等しく、前記クロック信号CSH2の位相は、前記クロック信号CSH1の位相とは大幅に異なる、サンプル及び保持ユニットSH2と、−前記のサンプル及び保持ユニットSH1又はSH2のサンプルを出力するための出力ユニットであって、前記位相信号PH1が前記位相差ΔP1は第1の領域にあることを示すときには前記サンプル及び保持ユニットSH1のサンプルが出力され、前記位相信号PH1が前記位相差ΔP1は第2の領域にあることを示すときには前記追加のサンプリング及び保持ユニットSH2のサンプルが出力される、出力ユニットとを有することにより特徴付けられる。これは、位相ジッタがある場合に発生するビットエラーの変更が低減されるという利点を有する。  (もっと読む)

(もっと読む)

デジタル制御型位相合成回路システム

【課題】 ジッタ耐性を強化し、かつロックレンジを拡大するデジタル制御型位相合成回路システムを得る。

【解決手段】 位相の異なる2つのクロックと制御信号が入力され、制御信号による重み付けに基づいて、これらのクロックの中間の位相をもつ出力クロックを合成する位相合成回路と、出力クロックの位相と基準クロックの位相とを比較するバイナリ型位相比較回路と、バイナリ型位相比較回路による比較結果に基づいて第1のカウント値をカウントアップ又はカウントダウンし、第1のカウント値の最上位ビットの値を出力し、第1のカウント値にキャリー又はボローが発生した場合にクロックパルスを出力する第1のアップダウンカウンタと、クロックパルスを動作クロックとし、第1のカウント値の最上位ビットに基づいて第2のカウント値をカウントアップ又はカウントダウンし、第2のカウント値を制御信号として出力する第2のアップダウンカウンタとを有する。

(もっと読む)

無線受信装置

【課題】デジタル放送受信装置における基準クロック信号生成用の電圧制御型水晶発振器を不要にしてコストを下げることができ、送信側から送信される時刻基準に合わせた高い周波数精度のクロック信号を生成し、映像及び音声を適切に復元する。

【解決手段】デジタル放送受信装置において、ビットストリーム解析回路と、システムクロック信号及びビットストリーム解析回路からの基準クロック制御データを受け、基準クロック信号を生成する基準クロックDPLL20を有し、基準クロックDPLL20は、システムクロック信号をn分周するn分周回路21及び(n+1)分周する(n+1)分周回路22と、各分周回路の分周比を設定するデータを格納するレジスタ23と、各分周回路の出力クロック信号の混合比率を設定するデータを格納する混合比率設定レジスタ24と、混合比率設定レジスタ24のデータに応じた混合比率で各分周回路の出力クロック信号を混合して出力する混合回路25を有する。

(もっと読む)

ディジタル位相同期ループ回路

【課題】ディジタル位相同期ループ回路において制御発振部の追従性能を向上させる。

【解決手段】このディジタル位相同期ループ回路において、第2の分周器18は、第1の位相比較器10からの第1の同期制御信号(c),(d)にしたがって所定のマスタ・クロックを1/Nに分周して基準クロック(a)のM倍の周波数を有する出力クロック(g)を生成する。第2の位相比較器54は、基準クロック(a)の位相とフィードバック・クロック(b)の位相とを比較して、それらの位相差に応じた第2の同期制御信号(m),(n)を生成する。そして、レンジカウンタ(分周比制御部)56は、分周器18おける分周比Nを第2の同期制御信号(m),(n)にしたがって可変制御する。

(もっと読む)

タイムスタンプを使用して非同期ネットワークの通信端末同士を同期化させるためのシステムおよび方法

本発明は、正規の光ファイバラインであるかの如く非同期イーサネットMANの使用を可能し、そのクラウド環境の不確定性を排除する。本発明は、2つの端末ノード間での非同期ネットワークにわたるリアルタイム同期データパケットの伝送を同期化する新たな方法を提供する。同期化処理は、端末ノードのTDM装置と非同期ネットワークとの間を接続する中間通信装置内で実施される。各通信装置は、階層2/3/3e/4/4eパルス発生器によって作動されるローカルクロックを備える。ローカルクロック同期化は、非同期ネットワークを介するタイムスタンプパケットの送信に基づく。上記基準に基づき、内部デジタルPLLは、階層2/3/3e/4/4e精度規格にしたがってデータ伝送信号内のジッタ/ワンダを軽減できる。その後、DPLLのデータ結果は処理され、受信端末のローカルクロックにより使用される。  (もっと読む)

(もっと読む)

1 - 20 / 20

[ Back to top ]