国際特許分類[G01R35/00]の内容

物理学 (1,541,580) | 測定;試験 (294,940) | 電気的変量の測定;磁気的変量の測定 (31,836) | このサブクラスの他のグループに包含される装置の試験または較正 (282)

国際特許分類[G01R35/00]の下位に属する分類

国際特許分類[G01R35/00]に分類される特許

61 - 70 / 261

周波数可変直角相ブリッジ

【課題】交流量子ホール効果抵抗(acQHR)を基準として標準キャパシタを校正周波数1.592 kHzで校正可能な周波数可変直角相ブリッジを提供する。

【解決手段】周波数可変直角相ブリッジ回路の分圧比ρ1、ρ2、ρ3、及びρ4を独立に調整して下記式のバランス条件、

【数16】

が満足されるように構成する。

(もっと読む)

ドライバ回路における電圧測定を較正する方法および装置

本発明は、殊に電気機械(2)用のドライバ回路(3)の端子電圧を測定するために電圧測定を較正する方法に関しており、この方法はつぎのステップを有する。すなわち、− 上記のドライバ回路(3)をスイッチオンして、第1の所定の電位が、例えば第1給電電位が端子接続部に印加されるようにし、第1電圧データを得るために第1の所定の電位を印加した状態で原動機端子における電圧(U1,U2)を測定し、ただし第1電圧データは、第1の所定の電位を印加した状態で処理回路(8)によって処理される電圧(U1_adc,U2_adc)を測定することによって得られるものであり、この電圧は、原動機端子に加わる電圧(U1,U2)をマッピングすることにより、殊に線形にマッピングすることによって得られる電圧であり、− ドライバ回路(3)をスイッチオンして、第2の所定の電位が、例えば第2給電電位が端子接続部に加わるようにし、− 第2電圧データを得るために第2の所定の電位を印加した状態で原動機端子における電圧(U1,U2)を測定し、ただし第2電圧データは、第2の所定の電位を印加した状態で上記処理回路によって処理される電圧(U1_adc,U2_adc)を測定することによって得られるものであり、この電圧は、原動機端子に加わる電圧(U1,U2)をマッピングすることにより、殊に線形にマッピングすることによって得られるものであり、第1電圧データおよび第2電圧データによって定められる直線の傾きとして補正係数を求め、実際の端子電圧を得るために、原動機端子において処理回路(8)を介して測定した電圧にこの補正係数を適用する。  (もっと読む)

(もっと読む)

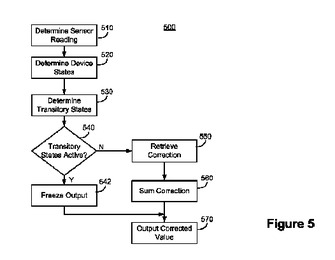

モバイル電子デバイスにおける正確な磁気コンパス

本明細書では、ホストデバイスの変化するソフトウェアモードおよびハードウェアモードに部分的に基づく非定常センサ誤差、特に非定常コンパス誤差の較正および補正のための方法および装置について説明する。各モードおよびモードの組合せによってセンサ中に誘導される非定常誤差は、1つまたは複数のホストデバイスの生産前試験中に判断され得る較正において判断される。較正結果はホストデバイスのソフトウェアおよび/またはハードウェアに組み込まれ得る。通常動作中に、アクティブモードまたはモードの組合せに部分的に基づいてセンサ測定値にセンサ補正が適用され得る。  (もっと読む)

(もっと読む)

電子部品の電気特性測定誤差の補正方法及び電子部品特性測定装置

【課題】測定系の特性が変わっても効率よく相対補正係数を決定することができる電子部品の電気特性測定誤差の補正方法及び電子部品特性測定装置を提供する。

【解決手段】測定対象の電子部品に近い特性を持つ少なくとも1つの補正データ取得試料以外の補正データ取得試料について基準測定治具と第1の測定治具とで電気特性を測定した結果61,62,64,65,66と、測定対象の電子部品に近い特性を持つ補正データ取得試料について第2の測定治具と基準測定治具とで測定した結果73とに基づいて、第2の試験測定治具で測定した結果から基準測定治具で測定した電気特性を算出する数式80の相対補正係数を決定する。電子部品を第2の試験測定治具で測定し、相対補正係数を用いて、基準測定治具で測定した電気特性を算出する。

(もっと読む)

信号取込みシステム及びその校正処理方法

【課題】プローブ時に、被測定デバイスの負荷を減少させる。

【解決手段】信号取込みシステムには、抵抗性中心導体信号ケーブル202に結合されたプローブ・チップ回路206を有する信号取込みプローブ105がある。信号取込みプローブ105の抵抗性中心導体信号ケーブル202は、信号処理装置115中の入力ノード及び入力回路を介して、信号処理装置中の補償システム225に結合される。信号取込みプローブ105及び信号処理装置115は、入力ノード204においては時定数がミスマッチしているが、補償システム225がフィードバック・ループ回路240のある入力増幅回路232及び補償デジタル・フィルタ256を有し、信号取込みシステム115の周波数帯域幅に渡ってフラットを維持するための極−零点対を提供する。

(もっと読む)

信号取込みシステム及びその校正処理方法

【課題】プローブ時に、被測定デバイスの負荷を減少させる。

【解決手段】信号取込みシステムには、抵抗性中心導体信号ケーブル202に結合されたプローブ・チップ回路206を有する信号取込みプローブ105がある。信号取込みプローブ105の抵抗性中心導体信号ケーブル202は、信号処理装置中の入力ノード及び入力回路を介して、信号処理装置中の補償システム232に結合される。信号取込みプローブ105及び信号処理装置は、入力ノード204においては時定数がミスマッチしているが、補償システム232がフィードバック・ループ回路245のある入力増幅回路234及び入力回路に結合されたシャント極−零点対を有し、信号取込みシステムの周波数帯域幅に渡ってフラットを維持するための極−零点対を提供する。

(もっと読む)

信号取込みシステム及びその校正処理方法

【課題】プローブ時に、被測定デバイスの負荷を減少させる。

【解決手段】信号取込みシステムには、抵抗性中心導体信号ケーブルに結合されたプローブ・チップ回路を有する信号取込みプローブがある。信号取込みプローブの抵抗性中心導体信号ケーブルは、信号処理装置中の入力ノード及び入力回路を介して、信号処理装置中の補償システムに結合される。信号取込みプローブ及び信号処理装置は、入力ノードにおいては時定数がミスマッチしているが、補償システムが信号取込みシステムの周波数帯域幅に渡ってフラットを維持するために、極−零点対を提供する。

(もっと読む)

制御システム及びそれに用いる半導体素子

【課題】高精度電流検出手段を1チップのLSIに内蔵でき、しかも、低コストで実現できる制御システム及びそれに用いる半導体素子を提供することにある。

【解決手段】駆動回路24−1,24−4は、同一の半導体チップ1の内部に設けられる。複数の駆動回路24−1,24−4は、それぞれ、負荷に流れる電流を検出するとともに、同一のプロセスにより、半導体チップ1内に設けられた電流検出用シャント抵抗Rs1,Rs4と、電流検出用シャント抵抗と同一のプロセスにより、半導体チップ1内に設けられたダミー抵抗Rdと、半導体チップ1に外付けされるとともに、ダミー抵抗Rdに接続される校正基準2とを備える。また、補正手段10は、ダミー抵抗Rd及び校正基準2を用いて、電流検出用シャント抵抗Rs1,Rs4に流れる電流値を補正する。

(もっと読む)

磁気抵抗効果センサの経年変化補正方法および経年変化補正装置

【課題】経年変化に伴うMRセンサの抵抗値シフトの問題を解消する。

【解決手段】MRセンサが特定の状態下にあるときのセンサ出力を基準として磁界測定時のMRセンサの出力を規格化する。具体的には、磁化コイル5に電流を流して磁界を発生させMRセンサ1,2に印加する。これにより、選択した「特定の状態」の下にMRセンサ1,2を置く。ここでMRセンサ2は、磁化コイル5からの磁界以外を遮断する磁気シールド構造3によって取り囲まれている。磁化コイル5への電流を遮断したのち、外部ソースに由来する未知の磁界が付与されたMRセンサ1の出力電圧と、未知の磁界の影響を受けないMRセンサ2の出力電圧との差分を求め、未知の磁界を推定する。

(もっと読む)

MR素子試験装置およびMR素子試験装置の自己故障診断方法

【課題】 本発明はMR素子試験装置に関し、より詳細には被試験体に磁界印可を行う電磁石ユニットに対する自己故障診断機能を備えると共に、電磁石ユニットの磁極面が広い領域で均一な磁界分布を有するMR素子試験装置に関するものである。

【解決手段】 本発明のMR素子試験装置は、対向する2つの磁極面から交番磁界を発生する電磁石と、一方の磁極面の近傍に配置した第1のホールセンサと、第1のホールセンサと対角の位置にある他方の磁極面の近傍に配置した第2のホールセンサと、交番磁界を発生させる交流電流と交番磁界の印可による第1のホールセンサの出力、および交流電流と第2のホールセンサの出力とを計測し、計測結果に基づいて電磁石と第1と第2のホールセンサとの故障の有無を診断する、よう構成する。

(もっと読む)

61 - 70 / 261

[ Back to top ]