国際特許分類[G06F7/00]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | 取扱うデータの順序または内容を操作してデータを処理するための方法または装置 (915)

国際特許分類[G06F7/00]の下位に属する分類

デジタル値の比較 (26)

個々の記録担体上のデータを分類,選別,組合せ,または別々の記録担体上のデータを比較するための装置

連続的記録担体,例.テープ,ドラム,ディスク,上のデータを分類または組合せる装置 (51)

位取り記数法を用いて計算を行なうための方法または装置,例.2進,3進,10進法を用いるもの (331)

乱数または擬似乱数発生器 (209)

デジタルな非位取り記数法,すなわち.基数を用いない数表現を用いて計算を行うための方法または装置;位取り記数法と非位取り記数法の組合せを用いる計算装置 (35)

1語内の,指定値を有する1以上のビットの位置を選別または符号化すること,例.最上位または最下位の有意な0または1の検出,プライオリティ・エンコーダ (6)

データ内容から独立して定められたルールによるデータの再配置,並べ替え,または選別のための装置 (42)

国際特許分類[G06F7/00]に分類される特許

131 - 140 / 215

リコンフィギュラブル回路及び処理装置

【課題】回路規模の縮小化と処理時間の短縮化等に貢献するリコンフィギュラブル回路を提供する。

【解決手段】それぞれが複数の算術論理演算機能を選択的に実行可能な複数の論理回路2から構成される演算部と、複数の論理回路2の間の接続関係を保持する接続部と、を備えるリコンフィギュラブル回路において、少なくとも1つの論理回路2は、その論理回路2の演算で使用する入力4bを、その論理回路2の演算の次の演算を実行する論理回路2に入力する専用の入力伝播線6を有する入力伝播回路5を備える。さらに、入力伝播回路5は、入力伝播回路5を備える第1の論理回路2で使用するデータを、第1の論理回路2の演算の次の演算を実行する第2の論理回路2に入力する際、第1の論理回路2での演算実行時間の間、データを保持し、第2の論理回路2で演算を実行するときに、第2の論理回路2に入力できるようにするデータ保持機構7を備える。

(もっと読む)

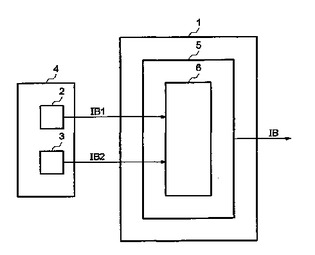

冗長的に送出され、あるシステムのパラメータを表す2進情報の値を判断する装置および方法

本発明は、異なる2つの判定手段(2、3)から冗長的に送出され、あるシステム(4)のパラメータを表す2進情報(IB)の値を判断する装置(1)において、前記2進情報が、前記パラメータが第1の値範囲(範囲0)に含まれるときには第1の値をとり、第2の値範囲(範囲1)に含まれるときには第2の値をとり、前記第1の値範囲(範囲0)および第2の値範囲(範囲1)が、前記判定手段(2、3)からそれぞれ発信される2進情報(IB1、IB2)の値の移行がその中で行われる移行範囲(範囲3)によって分離される装置であって、前記判定手段のうちの一方が動作不良のため値の移行を欠く2進情報(IB1、IB2)を送出したとき、パラメータが前記第1および第2の値範囲に含まれるときに正常に動作する他方の判定手段から送出される前記所定の第1または第2の値を割り当てるように適合された状態マシン(6)を備える判断手段(5)を含むことを特徴とする装置に関する。  (もっと読む)

(もっと読む)

リコンフィギュラブルプロセッサまたは装置

【課題】従来のリコンフィギュラブルプロセッサまたは装置が実現できなかった、入力されるデータの損失が無く、尚且つデータ演算処理性能の劣化が無い論理変更を可能とするリコンフィギュラブルプロセッサまたは装置を実現する。

【解決手段】前記のプロセッサまたは装置は、本願の、入力されるデータのうち、演算に必要なデータだけをリコンフィギュラブルな演算手段に分配する方式と、演算に不必要なデータがプロセッサに入力されているときに、リコンフィギュラブルな演算手段に発生する無演算時間を利用して、リコンフィギュラブルな演算手段の搭載論理を変更する方式によって実現される。

(もっと読む)

パイプライン演算処理装置

【課題】 データ更新周期が異なるデータを同時に処理しなければならない場合に同じ処理を複数回行わなければならず、消費電力を低減することができなかったという課題を解決する。

【解決手段】 2k個のパイプラインステージを有するパイプラインにおいて、クロックとk本の制御信号をクロック/段数制御部で生成し、n番目の制御信号を2n-1(2*j−1)(j=1,2,・・・2k-n)番目のパイプラインステージに入力し、この制御信号で各パイプラインステージ内のレジスタを有効にするか否かを制御するようにした。2k、2k-1、・・・1個のパイプラインステージを有するパイプラインとして用いることができるので、入力データの更新周期に応じて制御信号を変えることにより、消費電力を削減することができる。予め処理するデータ更新周期がわかっている信号発生装置やデータ処理装置に用いると効果が大きい。

(もっと読む)

ベクトル処理用の拡張可能な並列パイプライン浮動小数点数演算ユニット

【課題】ベクトル処理用の拡張可能な並列パイプライン浮動小数点数演算ユニットを提供する。

【解決手段】本発明の一実施形態は、ベクトル処理用の浮動小数点数演算を実行する技術である。入力待ち行列は複数のベクトル入力を捕獲する。スケジューラはベクトル入力をディスパッチする。複数の浮動小数点数演算(FP)パイプラインは、スケジューラがディスパッチしたベクトル入力のスカラー成分に対して演算を行うことにより得られるFP結果を生成する。アービター/アセンブラユニットは、出力部の利用を調停しつつ、FP結果をアセンブルして出力部に書き込む。

(もっと読む)

拡張関数を持つ混合モード浮動小数点パイプライン

本発明の一実施形態は、混合モード浮動小数点(FP)演算および拡張FP関数を行う技法である。シーケンサは入力ベクトルに作用する命令の発行を制御する。混合モードFPパイプラインは、拡張内部形式および一連の乗加算演算を利用して、入力ベクトルの拡張FP関数あるいは整数演算を計算する。混合モードFPパイプラインは前記シーケンサに対するパイプライン状態、およびFP結果を生成する。 (もっと読む)

浮動小数点数のベクトル演算方法

【課題】 浮動小数点数のベクトル積演算に必要な処理が軽減され、固定小数点型DSPによる演算処理が適用できるようにした浮動小数点数のベクトル演算方法を提供すること。

【解決手段】 N次の行ベクトルXとN次の列ベクトルYからなるベクトル積XYを求める浮動小数点数のベクトル演算方法において、入力端子1のバッファに格納するベクトルXの成分である各データx1〜xN の仮数部m1〜mN に対して、その指数部については予め各データx1〜xN で共通の指数eにしておき、ベクトルYの成分である各データy1〜yN の仮数部l1〜lN に対しても、その指数部については予め各データy1〜yN でこれも共通の指数e′にしておいてベクトル積XYを演算するようにしたもの。

予めベクトルの指数部を共通化しておくと演算処理量が軽減される。

(もっと読む)

リコンフィギュラブル予備クラスタを備えるリコンフィギュラブル回路

本明細書ではリコンフィギュラブル予備クラスタを持つリコンフィギュラブル回路が説明されている。

【その他】

国際段階にて出願人の名称変更手続を済ませております。

(もっと読む)

回路および回路接続方法

【課題】閉塞ネットワークを利用した回路において、従来よりも多くのアプリケーションを実装する。

【解決手段】入力されるデジタルデータに対して数値演算または論理演算を実行し、数値演算または論理演算の出力信号を出力する、そのような1以上の演算素子と、前記の演算素子の入力側に接続されるネットワーク出力端子と、前記演算素子の出力信号または前記演算素子の出力信号以外の外部信号が入力されるネットワーク入力端子と、前記入力端子を出力端子に接続するネットワーク部と備え、ネットワーク出力端子のうちの2つのネットワーク出力端子が同時に接続することができないネットワーク入力端子の組に含まれるネットワーク入力端子数として定義される制約強度について、同一の演算素子に入力される複数の出力端子間の制約強度が最小となるように、前記演算素子とネットワーク出力端子とを接続した。

(もっと読む)

情報処理装置

【課題】 リコンフィギュラブルハードウエア5及びプロセッサ4から構成された信号処理部を有する情報処理装置で、これらの機能を様々に変更することを可能とする。

【解決手段】 リコンフィギュラブルハードウエアをコンフィギュレーションするためのプログラムを記憶する第1の記憶手段6、記憶されたプログラムに基づいてリコンフィギュラブルハードウエアをコンフィギュレーションするコンフィギュレーション手段7、プロセッサにより使用されるプログラムを記憶する第2の記憶手段3、コンフィギュレーションが非実行であるときに第1の記憶手段にプログラムを書き込む第1の制御手段1、プロセッサをリセット状態にするリセット手段1、7、プロセッサがリセット状態にされている間に第2の記憶手段にプログラムを書き込む第2の制御手段1を備えた。

(もっと読む)

131 - 140 / 215

[ Back to top ]