国際特許分類[G06F9/30]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | プログラム制御のための装置,例.制御装置 (15,360) | プログラム記憶方式を用いるもの,すなわちプログラムを受取りそして保持するために処理装置の内部記憶装置を用いるもの (15,354) | 機械語命令を実行するための装置,例.命令デコーダ (1,710)

国際特許分類[G06F9/30]の下位に属する分類

算術演算の実行を制御するもの

論理演算の実行を制御するもの (41)

単一ビット演算を制御するもの (4)

ロード,ストアまたはクリアの演算を制御するもの

移動,桁送りまたは回転の演算を制御するもの (20)

演算の拡張または修飾を伴うもの (38)

次位命令のアドレス指定,例.命令カウンタ値の増加,ジャンプ (110)

命令オペランドまたは演算結果のアドレシングまたはアクセシング (184)

命令の同時実行,例.パイプライン,ルック・アヘッド (952)

国際特許分類[G06F9/30]に分類される特許

51 - 60 / 361

VLIW型プロセッサ用コンパイラ、VLIW型プロセッサ用プログラム開発システムおよび方法

【課題】連続して使用しない演算器を低消費電力モードに設定する電力制御を効率的に行えるVLIW型プロセッサ用プログラムを容易に開発できる開発システムの実現。

【解決手段】複数の演算器36AA,36AB,36AC,36BA,36BB,36BCをそれぞれ有する複数のスロット35A,35Bを備え、演算器の少なくとも一部は低消費電力モードに設定可能であるVLIW型プロセッサ用プログラムの開発システムであって、VLIW型プロセッサ用コンパイラ21と、コンパイラが出力したプログラムを実行する時に使用する演算器の使用情報を生成する演算器使用情報生成部38と、使用情報に基づいて電力制御コンパイルオプションを生成して出力する演算器使用情報出力部72と、を備え、コンパイラ21は、各スロットで使用する演算器の変更を指示する電力制御コンパイルオプションが入力されるインターフェースを備える。

(もっと読む)

マイクロプロセッサ

【課題】用途に応じて同一マイクロプロセッサを使い分ける場合に、命令デコード、命令実行などにより規定される最大動作周波数の制約が発生する。

【解決手段】本発明は、例えば、用途に応じて、最大動作周波数を可変にするために、命令または命令セットの一部を無効化させることを特徴とする。一例として、命令を、メモリから読み出してフェッチする命令フェッチ部と、命令フェッチ部でフェッチした命令に対するデコード処理を行う命令デコード部と、デコード後の命令に対する処理を実行する命令実行部とを有して構成されるマイクロプロセッサにおいて、前記命令デコード部が、外部設定値を入力とし、外部設定値によって、一部の命令をデコード対象から除外すること、または低速化させることを特徴とする。

(もっと読む)

効率的プロセッサおよび関連する方法

装置は、プロセッサを含む。プロセッサは、2つのメモリを含む。第1のメモリは、一式の命令を格納する。第2のメモリは、第1のメモリにおける一式の命令より長い別の一式の命令を格納する。第1のメモリおける一式の命令おける命令は、第2のメモリおける一式の命令おける対応する命令に対するポインタとして使用される。一実施形態において、集積回路(IC)は、プロセッサを含み、プロセッサは、第2の一式の命令をアドレス指定する第1の一式の命令を格納する第1のメモリと、第2の一式の命令を格納する第2のメモリとを含み、第2のメモリは、経時的に、命令のスケジューリングを可能にするために、サイクルオフセットを含む。  (もっと読む)

(もっと読む)

演算処理装置、情報処理装置及び制御方法

【課題】専用転送バスを設けずに、キャッシュヒットチェックの結果を容易に読み出すことを課題とする。

【解決手段】演算処理装置10は、キャッシュの状態をチェックするキャッシュヒットチェックを実行するか否かを示すデバッグフラグビット31aを有する。そして、キャッシュヒットチェックを実行する旨が記憶されており、かつ、プリフェッチ命令を受信した場合に、プリフェッチ命令を拡張してキャッシュヒットチェック処理を実行する。そして、演算処理装置10は、キャッシュヒットチェックが実行された場合に、キャッシュヒットチェックの結果をL1ヒット情報レジスタ32に記憶し、ヒット情報レジスタ23、32に記憶されたキャッシュヒットチェックの結果を読み出すように制御する。

(もっと読む)

情報処理装置

【課題】複数の命令語で構成される超長命令を実行する情報処理装置において、同時実行可能な命令数を低コストで増やすことができるようにすること。

【解決手段】メモリからプログラムをフェッチする命令フェッチ部1と、命令デコーダ部2と、組合せ指示フィールドと命令語グループ内の命令の並びに基づいて演算器の組合せを指示する組合せ制御部3と、命令の指示に基づいて演算器へソースオペランドを供給するレジスタファイル部4と、組合せ制御部3の指示に基づいてレジスタファイル部4からのソースオペランド若しくは命令語グループ内の演算器の演算結果を、命令語グループ内の他の演算器のソースオペランドとして供給する入力セレクタ部5及び入力セレクタ部6と、命令の指示に基づく演算を実施し、該演算結果をレジスタファイル部4と、入力セレクタ部5及び入力セレクタ部6へ供給する演算器A〜Fと、を備えて構成されている。

(もっと読む)

単一命令でシフトおよび排他的論理和演算を行う方法および装置

シフトおよびXOR演算を実行する方法および装置が開示される。一実施形態では、装置は、第1の命令を実行する実行リソースを含む。第1の命令に呼応して、実行リソースは、少なくとも1つの値にシフトおよびXORを行う。 (もっと読む)

保証された定常状態期限で中央処理装置電力を制御するためのシステムおよび方法

中央処理装置を動的に制御する方法が、開示される。この方法は、CPUがいつ定常状態に入るかを判定すること、CPUが定常状態に入ると、CPUに関する最適な周波数を計算すること、定常状態CPU利用率を保証すること、および定常状態CPU利用期限を保証することを含むことが可能である。 (もっと読む)

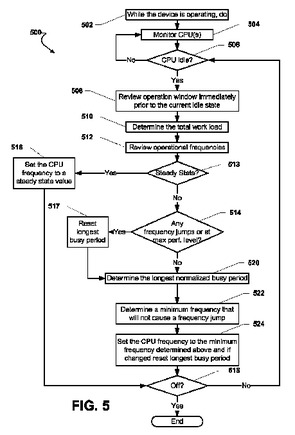

周波数変動を低減させて中央処理装置電力を制御するためのシステムおよび方法

中央処理装置内の電力を動的に制御する方法が開示され、アイドル状態に入ること、アイドル状態の直前のビジーサイクルを点検すること、および前のビジーサイクルに基づいて、次のビジーサイクルに関するCPU周波数を算出することを含むことが可能である。  (もっと読む)

(もっと読む)

3個のソースオペランドを加算する加算命令

【課題】3個のソースオペランドを加算する新たな命令を設ける。

【解決手段】方法は加算命令の受信が含まれうる。加算命令は、第1のソースオペランド、第2のソースオペランド、および第3のソースオペランドを示すことができる。第1、第2、および第3のソースオペランドの和を、加算命令の結果として格納する。この和は、一部分が、加算命令が示すデスティネーションオペランドに格納され、一部分が、複数のフラグに格納されてよい。他の方法、装置、システム、および機械可読媒体上の命令も含む。

(もっと読む)

複数のデータ・エレメントの収集及び分散

【課題】 本発明は、複数のデータ・エレメントの収集及び分散に関する。

【解決手段】 第1の態様によると、効率的なデータ転送処理は、単一の命令が複数のデータ・エレメントに対する第1の記憶域と第2の記憶域との間の転送処理を指定し、プロセッサ装置によりデコードする段階、前記プロセッサ内の演算実行部による実行のために単一の命令を発行する段階、単一の命令の実行中に例外の発生を検出する段階、及び該例外に応答して、該例外を分配する前に、未解決のトラップ又は割り込みを例外ハンドラに分配する段階、により達成されうる。

(もっと読む)

51 - 60 / 361

[ Back to top ]