国際特許分類[G11C19/00]の内容

国際特許分類[G11C19/00]の下位に属する分類

磁気素子を用いるもの (1)

共振回路中の非線型誘導素子を用いるもの

能動素子,例.放電管,半導体素子,と結合した磁気素子を用いるもの (1)

ステージの主素子としてキャパシタを用いるもの

放電管を用いるもの

半導体素子を用いるもの (202)

オプト―エレクトロニクス装置,すなわち電気的または光学的に結合された光放射および光―電気装置を用いるもの

超電導素子を用いるもの

3以上の異なる安定状態を有する記憶素子を用いるもの,例.電圧によるもの,電流によるもの,位相によるもの,周波数によるもの

二次元の,例.水平方向と垂直方向に情報が移動するシフト・レジスター

国際特許分類[G11C19/00]に分類される特許

111 - 120 / 283

表示装置

【課題】単チャンネルシフトレジスタを有する表示装置において、トランジスタの負荷を増大することなく、駆動クロックの振幅を大きくする。

【解決手段】複数の画素を有する表示パネルと、各画素を駆動する駆動回路とを有し、前記駆動回路には、電圧レベルがVHの電圧レベルと、VLの電圧レベルとの間で変化する駆動クロックが入力され、前記駆動回路は、オン状態の時に前記クロックを取り込み、出力端子から出力する表示装置であって、第1電極に前記駆動クロックが入力されるトランジスタと、前記トランジスタの前記第2電極と前記端子との間に接続され、制御電極が前記トランジスタの制御電極に接続される第1保護トランジスタと、第2電極に前記駆動クロックが入力され、制御電極にVDDの電圧が入力される第2保護トランジスタと、前記第2保護トランジスタの第1電極と、前記トランジスタの前記第2電極との間に接続されるダイオード接続の第3保護トランジスタとを有し、VL<VDD<VHを満足する。

(もっと読む)

シフトレジスタ回路

【課題】複数のスタートパルスを必要とするシフトレジスタ及びそれを用いたゲート線駆動回路において、外部から入力しなければならないスタートパルスの数を削減する。

【解決手段】ゲート線駆動回路30は、位相の異なる2つのスタートパルスがその動作に必要なシフトレジスタSR1,SR2,…と、外部から入力される第1スタートパルスSP1を受け、それに遅れて活性化する第2スタートパルスSP2を生成するスタートパルス生成回路32とを備えている。シフトレジスタSR1,SR2,…は、外部から入力された第1スタートパルスSP1と、スタートパルス生成回路32が生成した第2スタートパルスSP2に基づいて動作する。

(もっと読む)

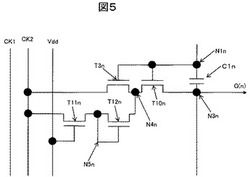

電界効果トランジスタシフトレジスタ

シフトレジスタにおいて、対応する出力ラインR(n)を駆動するために設けられた各段Enは出力ラインを駆動する出力トランジスタT3と同じ技術かつ同じ極性のトランジスタT5を含む。このトランジスタは、寿命の最初に出力トランジスタの閾値電圧と同一であるその閾値電圧が、出力トランジスタと同程度以上速くドリフトするように、出力トランジスタと同様のバイアス条件を課されるやり方で接続される。このトランジスタT5は、プリチャージおよび/または選択フェーズ中に、出力トランジスタT3のゲートg3のプリチャージ電圧V1’をその導通性能特性に調節するために用いられる。本シフトレジスタは集積化アクティブマトリクスフラットスクリーンに適用可能である。  (もっと読む)

(もっと読む)

駆動回路、表示装置、及び電子機器

【課題】シフトレジスタ回路における動作不良を抑制することを課題とする。

【解決手段】複数のフリップフロップ回路からなるシフトレジスタを有し、フリップフロップ回路は、トランジスタ11、トランジスタ12、トランジスタ13、トランジスタ14、及びトランジスタ15を有し、非選択期間において、トランジスタ13またはトランジスタ14がオン状態になることにより、ノードAの電位を設定し、ノードAが浮遊状態になることを抑制する。

(もっと読む)

ブートストラップ回路及びそれを用いたシフトレジスタと表示装置

【課題】制御信号線数の低減及びトランジスタのリーク電流耐性の向上を図るシフトレジスタの提供。

【解決手段】電源端子(VDD)と第1のクロック信号端子(CL1)間に直列に接続され、接続点を出力端子(OUT)とするトランジスタ(Tr7、Tr1)と、電源端子(VDD)と第2のクロック信号端子(CL2)間に直列に接続されたトランジスタ(Tr6、Tr4、Tr3)と、電源端子(VDD)とトランジスタ(Tr1)のゲート間に接続されたトランジスタ(Tr5)と、トランジスタ(Tr1)のゲートにソースが接続されたトランジスタ(Tr2)を備え、トランジスタ(Tr2、Tr6)のゲートは入力端子(IN)に接続され、トランジスタ(Tr4)のゲートには、入力端子(IN)に入力が接続されるインバータ(100)の出力が接続され、トランジスタ(Tr5、Tr7)のゲートはトランジスタ(Tr6、Tr4)の接続点に接続され、トランジスタ(Tr1)のゲートはトランジスタ(Tr5、Tr2)の接続点に接続される。

(もっと読む)

シフトレジスター及びそのゲート駆動器

【課題】改善されたシフトレジスター及びそのゲート駆動装置を提供する。

【解決手段】本発明によるシフトレジスターは、第1ノードにゲートが、一つのクロック信号端にソースが、自段出力端にドレインが、それぞれ接続される第1薄膜トランジスタと、第2ノードにゲートが、自段出力端にソースが、ローレベル信号端にドレインが、それぞれ接続される第2薄膜トランジスタと、第1ノードにゲートが、ローレベル信号端にソースが、第2ノードにドレインが、それぞれ接続される第3薄膜トランジスタと、第2ノードにゲートが、ローレベル信号端にソースが、第1ノードにドレインが、それぞれ接続される第4薄膜トランジスタと、クロック信号端と第2ノードとの間に接続される第1容量と、クロック信号端と自段出力端との間に接続される放電モジュールと、第1ノードとローレベル信号端との間に接続される補償モジュールと、を備える。

(もっと読む)

シフトレジスタ、該シフトレジスタを用いた液晶表示装置、及び液晶装置のスキャンライン駆動方法

【課題】大画面に適合し両方向シフト機能を有するようにする。

【解決手段】本発明のシフトレジスタは、第1選択信号が第1レベルである場合に順方向シフト動作を実行し、第2選択信号が前記第1レベルである場合に逆方向シフト動作を実行する第1ステージと、第1選択信号が第1レベルである場合に順方向シフト動作を実行し、第2選択信号が第1レベルである場合に逆方向シフト動作を実行する複数個の中間端ステージと、第1選択信号が第1レベルである場合に順方向シフト動作を実行し、第2選択信号が第1レベルである場合に逆方向シフト動作を実行する最終ステージと、順方向シフト動作時に最終ステージをリセットさせる第1ダミーステージと、逆方向シフト動作時に第1ステージをリセットさせる第2ダミーステージとを含み、両方向シフト機能を有する。

(もっと読む)

シフトレジスタ回路、表示パネル及び電子機器

【課題】動作の信頼性が高く高速動作にも適したシフトレジスタ回路を提案する。

【解決手段】絶縁基板上に単一チャネルの薄膜トランジスタにより形成されるシフトレジスタ回路の個々のシフト段に以下の構造を採用する。クロック入力端と第1の電源の間に、第1のトランジスタと第2のトランジスタを直列に接続し、その接続中点を出力端とする。第1の電源と第2のトランジスタの制御配線(ノードB)とを第3のトランジスタで接続する。第1の電源と第1のトランジスタの制御配線(ノードA)とを第4のトランジスタで接続する。第3のトランジスタは第1の入力端の電位で制御し、第4のトランジスタは、Bノードの電位で制御する。ノードBの電位は、ノードBと第2の電源の間に接続される第5のトランジスタで制御する。ノードAの電位は、ノードAと第2の電源の間に接続される第6のトランジスタで制御する。

(もっと読む)

シフトレジスタおよびアクティブマトリクス装置

シフトレジスタは、カスケード接続されたステージを含み、各ステージはデータラッチ(44)と出力ステージとを含む。ラッチ(44)は、使用時に、前段または後段のステージからデータ信号を受け取る単一のデータ入力(S)を有する。上記出力ステージは、その出力ステージが上記ラッチによってアクティブとされた時にクロック信号(CK2)をステージ出力(GL)に通すように構成された第1スイッチ(56)を含む。また、上記出力ステージは、その出力ステージが非アクティブである時に低電源電圧(Vss)をステージ出力(GL)に通すように構成された第2スイッチ(58)を含む。  (もっと読む)

(もっと読む)

シフトレジスタおよびそれを用いた表示装置

【課題】シフトレジスタに用いられる薄膜トランジスタのしきい値電圧の変化を少なくし、シフトレジスタおよびそれを用いた表示装置の寿命と信頼性を向上させる。

【解決手段】nチャネルTFT51aの電流路の一端にクロック信号が供給される。クロック信号は、ハイレベルの電圧とローレベルの電圧を交互に繰り返す。クロック端子CKmに印加されるクロック信号がハイレベルの電圧である間に、入力端子INにハイレベルの入力信号が入力すると、nチャネルTFT51aは電流路の一端と他端が導通し、ノードn1にハイレベルの電圧を印加する。同様に、nチャネルTFT61aのゲート電極と電流路の一端にクロック信号が供給される。クロック信号がハイレベルの電圧である間、nチャネルTFT61aは電流路の一端と他端が導通し、ノードn3にハイレベルの電圧を印加する。

(もっと読む)

111 - 120 / 283

[ Back to top ]