国際特許分類[H01L21/00]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847)

国際特許分類[H01L21/00]の下位に属する分類

半導体装置またはその部品の製造または処理 (125,986)

半導体装置以外の固体装置またはその部品の製造または処理であって,グループ31/00〜51/00に分類されている一つの型の装置に特に適していないもの (1)

製造または処理中の試験または測定 (6,126)

製造または処理中の半導体または電気的固体装置の取扱いに特に適用される装置;半導体または電気的固体装置もしくは構成部品の製造または処理中のウエハの取扱いに特に適用される装置 (11,346)

1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275)

国際特許分類[H01L21/00]に分類される特許

91 - 100 / 113

半導体装置の製造システム

【課題】個々のプロセス処理装置のメンテナンス間隔を適切に管理し、各プロセス処理装置の稼働時間を延長させ、各半導体製造プロセスが終了した段階で実施するウエハ検査工程をも削減させ、半導体装置の製造工程期間を短縮させる半導体装置の製造システムを提供する。

【解決手段】半導体基板17を用いたプロセス処理を実行する処理装置14と、処理装置14から装置情報を受信しプロセス処理の推定品質値を算出する自己診断システム11aと、プロセス処理の結果を検査する検査装置19と、検査結果と推定品質値とを比較し、推定品質値を有効判定するときは自己診断システムのパラメータを維持し、推定品質値を無効判定するときは自己診断システムのパラメータを変更するコンピュータ11と、を備える。

(もっと読む)

シャロー・トレンチ・アイソレーションの応力効果および光学的近接効果を相殺することによって半導体デバイスを製造する方法

【課題】半導体デバイス製造工程における形状の欠陥を補償する方法を提供する。

【解決手段】本発明は第1の半導体デバイスの分離構造応力効果を決定する工程、第2の半導体デバイスの光学的近接効果を決定する工程、製造モデル上で分離構造応力効果が光学的近接効果で相殺されるようにモデリング設計パラメータを選択する工程、および選択された設計パラメータを用いて第3の半導体デバイスを構成する工程とを含む半導体デバイスを製造する方法を提供する。

(もっと読む)

半導体装置の信頼性シミュレーション方法及び信頼性シミュレータ

【課題】 高精度のNBTI寿命モデルおよびTDDB寿命モデルを新たに作成し、該モデルを使用することにより、高精度で応用範囲の広いNBTI劣化シミュレーションおよびTDDB故障シミュレーションを実現する。

【解決手段】 半導体装置を構成するMOSトランジスタのNBTI劣化の予測値に基づき半導体装置の信頼性シミュレーションを行う際に、MOSトランジスタに対する累積NBTIストレス量を表すパラメータAgeを、Age=C・∫[(Ih/Area)m ]dt(但し、IhはMOSトランジスタのゲート絶縁膜を流れる正孔電流であり、AreaはMOSトランジスタのゲート面積であり、tはNBTIストレス時間であり、mはモデルパラメータであり、Cは比例定数である)で表されるモデル式を用いて算出する。

(もっと読む)

半導体デバイスのソフトエラー率の検証方法及び半導体デバイスの設計方法

【課題】 半導体デバイスのソフトエラー率を高速・簡単に検証することができる検証方法、及び、その検証方法を用いた半導体デバイスの設計方法を得る。

【解決手段】 半導体デバイスの設計に用いる複数のセルが登録されたセルライブラリに、各セルのソフトエラー率を登録するステップと、被検証対象である半導体デバイスに含まれる各セルの個数をカウントするステップと、各セルについて個数とソフトエラー率との積を求め、この積を全てのセルについて足し合わせて、半導体デバイスのソフトエラー率を検証するステップとを有する。

(もっと読む)

半導体集積回路の回路シミュレーション装置、及び、その回路シミュレーション方法

【課題】 精度の高いシミュレーションを実現することを可能とした半導体集積回路の回路シミュレーション装置、及び、その回路シミュレーション方法を提供する。

【解決手段】 半導体集積回路の回路シミュレーション装置に、初期パラメータ1と、素子の接続情報を有するシミュレーション対象回路ネットリスト2と、デバイスの測定結果であるインラインデータ3又は回路ブロック毎最適化ノウハウ情報4の少なくともいずれか一つと、パラメータ最適化についてのユーザ指示であるユーザ入力条件5とを入力するデータ入力手段6と、入力された情報を基に、シミュレーション直前に、初期パラメータ1に対して補正又は調整を加えて最適化済パラメータ8を作成するSPICEパラメータ最適化処理手段7と、作成された最適化済パラメータ8を用いてシミュレーションを実行する回路シミュレーションエンジン9とを設ける。

(もっと読む)

3次元不純物分布算出方法

【課題】 微細素子等のデバイスシミュレーションのために、3次元不純物分布を精度良く且つ容易に計算できる方法を提供する。

【解決手段】 MOSFETの3次元構造におけるチャネル幅方向断面(A−A’線の断面)及びチャネル長方向断面(B−B’線の断面)のそれぞれの2次元不純物分布を2次元プロセスシミュレーションにより算出する。素子領域と素子分離領域2との界面9a及び9bの延びる方向にチャネル幅方向断面の2次元不純物分布を順次移動させると共にゲート酸化膜3の縁10c及び10dの延びる方向にチャネル長方向断面の2次元不純物分布を順次移動させながら、両方の2次元不純物分布を足し合わせることによって、3次元不純物分布を算出する。

(もっと読む)

歩留まり改善

集積回路は、集積回路を設計するときに用いられる1組の設計要素の中から1つの設計要素を取上げることによって、集積回路を製造するときの歩留まりを改善するよう設計されている。1つの変形設計要素は、その取上げられた設計要素に基づいてその取上げられた設計要素の特徴を修正して生成される。その変形設計要素について歩留まり対面積の比が求められる。その変形設計要素の歩留まり対面積の比がその取上げられた設計要素の歩留まり対面積の比より大きい場合は、その集積回路を設計するときに用いられるその変形設計要素が保持される。  (もっと読む)

(もっと読む)

電子デバイスの製造方法、ヒューズの組合せ探索プログラム及び、電子デバイスの検査装置

【課題】 複数通りの組合せの中から目標値への合わせ込みに適した組合せを簡単に探索できるようにした電子デバイスの製造方法、ヒューズの組合せ探索プログラム及び、電子デバイスの検査装置を提供する。

【解決手段】 ヒューズF1〜F5を所定の組合せで切断し発振回路8の周波数特性を狙い値に合わせ込む際に、32通りの組合せの中から合わせ込みに適した組合せを探索する方法であって、発振回路8を構成する複数個の抵抗素子R1〜R5にそれぞれ対応して形成されたTEG内の抵抗素子R´1〜R´5の抵抗値をそれぞれ測定し、この測定結果に基づいて抵抗素子R1〜R5の抵抗値をそれぞれ推定する。次に、推定した抵抗素子R1〜R5の抵抗値に基づいて、32通りの組合せでヒューズF1〜F5を切断した場合にそれぞれ得られる周波数特性をシミュレーションする。

(もっと読む)

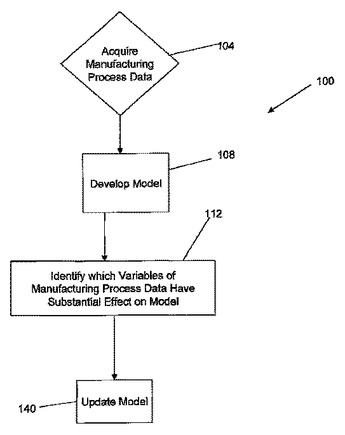

半導体プロセスの多変量制御

製造プロセスの故障条件を検出する方法であって、製造プロセスの複数の出力に対する複数の製造関係変数に基づいて、データを取得し、モデルを展開する。この方法は、更に、前記製造関係変数の中のどの変数が、前記製造プロセスの誤った出力を検出する前記モデルに対して実質的な影響を有するのかを識別するステップを含む。本発明による方法は、また、前記モデルに実質的影響を有すると先に識別された製造関係変数を用いることによって前記モデルを更新し、製造プロセスの誤った出力を検出する前記モデルの能力を強化するステップを含む。  (もっと読む)

(もっと読む)

生産工程の品質予測システムおよびその方法

【課題】生産装置が加工中のプロセスパラメータと、製品の過去数ロットの実際測定値とを基に、将来生産される製品品質を予測する。

【解決手段】本発明は主に推測モデル手段100および予測モデル手段200の二つからなり、その推測方法および予測方法は、実際の生産装置の特性に合わせて選択され、推測モデル手段100にはバーチャル測定を用いることができる。また、本発明は自己探索手段160および自己調整手段180をさらに備え、アルゴリズムにより最適なパラメータおよび関数の組み合わせを選択して、新しい生産装置20の特性および推測/予測精度の要求を満たす。

(もっと読む)

91 - 100 / 113

[ Back to top ]