国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,061 - 5,070 / 6,199

半導体装置の製造方法

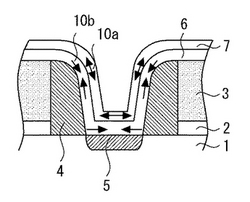

【課題】 ファセット形状のない金属シリサイド層を形成し、ソース・ドレインとシリコン基板との間の接合リークを減少させる。

【解決手段】 シリコン基板1の上にソース・ドレイン5を形成し、その上にシリサイド化用金属膜(Ni膜)6、ストレス膜7を形成する。ストレス膜7としてTiN膜およびCo膜からなる積層膜を形成する。この状態でシリサイド化アニールを行うと、ストレス膜7は引っ張り応力10aを有する。この応力に対応するように、シリサイド化用金属膜6は圧縮応力10bを有する。

このようにしてシリサイド化用金属膜6をシリコン基板1とシリサイド化反応させることにより、反応速度が抑制される。このため、ファセット形状を有しないNiモノシリサイド層(NiSi)を形成することができる。これにより、ソース・ドレイン5とシリコン基板1との間の接合リーク電流を減少させることができる。

(もっと読む)

薄膜トランジスタ基板及びその製造方法

【課題】本発明は、液晶表示装置に用いられる薄膜トランジスタ基板及びその製造方法に関し、ゲート電極や所定の配線の材料に低抵抗金属を用いても、高い信頼性を確保しうる薄膜トランジスタ基板及びその製造方法を提供することを目的とする。

【解決手段】TFT基板は、窒素含有層としてのAlN膜51と、主配線層としてのAl膜50と、MoN膜54とMo膜53とからなる上層配線層とにより構成された積層構造のゲート電極33を有している。ゲート電極33の側面は全体としてなだらかに傾斜するように形成されているので、ゲート絶縁膜32上に良好な膜質のゲート絶縁膜32を形成することができる。

(もっと読む)

有機薄膜トランジスタ及びその製造方法、有機薄膜トランジスタを備えた平板表示装置

【課題】有機薄膜トランジスタ及びその製造方法、有機薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】基板の所定部分を表面処理する段階と、表面処理されていない基板上にソース/ドレイン電極を形成する段階と、基板の表面処理された部分とコンタクトするように半導体層を形成する段階と、基板上にゲート絶縁膜を形成する段階と、ゲート絶縁膜上にゲートを形成する段階とを含む薄膜トランジスタの製造方法である。基板は、CF4ガスまたはC3F8ガスのようなフッ素系ガスを用いてプラズマ表面処理する。これにより、基板のチャンネル層に対応する部分をフッ素系ガスを用いて表面処理することによって、チャンネル層を安定化させて素子の特性を向上させうる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】 グラファイト層の除去工程を行わなくても、密着性の高い配線用電極が形成できるSiC半導体装置およびその製造方法を提供する。

【解決手段】 グラファイト層5が形成される前に、予めNi膜2の上にNiシリサイド膜3を形成する。このようにすれば、Ni膜2をシリサイド化したときに、グラファイト層5がNiシリサイド膜3と科学的に結合されるようにすることができる。これにより、グラファイト層5とNiシリサイド膜3とを高い密着強度で接合することができる。そして、グラファイト層5の表面にではなく、Niシリサイド膜3の上に配線用電極6を形成することができるため、配線用電極6がNiシリサイド膜3から剥離することもない。このため、グラファイト層5の除去工程を行わなくても、配線用電極6の剥がれを防止することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】 CMISFETを有する半導体装置の性能を向上させる。

【解決手段】 CMISFETを構成するnチャネル型MISFET40とpチャネル型MISFET41は、ゲート絶縁膜14,15が酸窒化シリコン膜からなり、ゲート電極23,24が、ゲート絶縁膜14,15上に位置するシリコン膜を含んでいる。ゲート電極23,24とゲート絶縁膜14,15との界面近傍に、1×1013〜5×1014原子/cm2の面密度でHfのような金属元素が導入されている。nチャネル型MISFET40とpチャネル型MISFET41のチャネル領域の不純物濃度は、1.2×1018/cm3以下に制御されている。

(もっと読む)

有機トランジスタ用電極、有機トランジスタ、及び半導体装置、

【課題】有機トランジスタの電極の一部として導電性の材料を用いた場合、その導電性の材料の仕事関数に有機トランジスタの特性が支配されない構成を有する有機トランジスタを提供することを課題とする。さらに、キャリア移動度が良好な有機トランジスタを提供すること、また、耐久性に優れた有機トランジスタを提供することを課題とする。

【解決手段】有機電界効果トランジスタ用の電極、すなわち有機電界効果トランジスタにおけるソース電極及びドレイン電極の少なくとも一方の一部に、有機化合物と無機化合物とを含む複合層を用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】亀裂の無い厚いPSG膜を単層で形成し、低コストで高信頼性の半導体装置およびその製造方法を提供する。

【解決手段】450nm以上の段差T1のある酸化膜5の下地を、リン濃度が2molwt%〜5molwt%で膜厚T1が1.3μm以上の単層のPSG膜7で被覆する。リン濃度を2molwt%〜5molwt%とすることで、下地の段差T1が450nm以上あり、単層のPSG膜の厚さW1が1.3μm以上あった場合でも、高温熱処理によるPSG膜の収縮時に亀裂が発生するのを防止できる。

(もっと読む)

CMOS半導体装置

【課題】CMOS半導体装置において、pチャネルMOSトランジスタの動作速度を向上させる。

【解決手段】第1の素子領域と第2の素子領域とを含む基板と、前記第1の素子領域上に第1のゲート絶縁膜を介して形成されたn型半導体材料よりなる第1のゲート電極と、前記第1の素子領域中、前記第1のゲート電極の両側に形成された一対のn型拡散領域と、前記第2の素子領域上に第2のゲート絶縁膜を介して形成されたp型半導体材料よりなる第2のゲート電極と、前記第2の素子領域中、前記第2のゲート電極の両側に形成された一対のp型拡散領域とよりなるCMOS半導体装置において、前記第2の素子領域は、前記第1の素子領域のホール移動度よりも大きなホール移動度を有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に熱処理を施したとしてもコンタクトプラグの周囲に形成された窒化膜に生じる熱変形を抑え、半導体装置の電気的特性を維持することができる半導体装置の製造方法を提供する。

【解決手段】 工程14では、シリコン基板12上の層間絶縁膜14にコンタクトホール15aを形成する。工程15では、シリコン基板12におけるコンタクトホール15aの下側に不純物31を導入する。工程16では、導入した不純物31を、例えば、800℃の温度の熱処理によって拡散してドレイン電極23の領域を広げる。工程17及び18では、コンタクトホール15aの内面にチタン膜28及び窒化チタン膜29を形成する。工程19では、半導体装置11に、例えば、520℃の温度の熱処理を施して、シリコン基板12におけるバリアメタル26とシリコン基板12との間にシリサイド膜16を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性が高く小型なTFTを作製するために、信頼性の高いゲート電極、ソース配線及びドレイン配線を形成するための半導体装置の作製方法及び半導体装置を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に半導体膜を形成し、前記半導体膜上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極を形成し、前記ゲート電極に高密度プラズマにより窒化することによって前記ゲート電極の表面に窒化膜を形成する半導体装置の作製方法である。

(もっと読む)

5,061 - 5,070 / 6,199

[ Back to top ]