国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,071 - 5,080 / 6,199

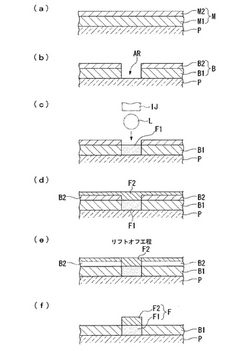

導電膜パターンの形成方法、デバイスの製造方法、電気光学装置、及び電子機器

【課題】 膜パターン上をより緻密なバリアメタル層で覆うことにより、金属元素が拡散することを防止した、導電膜パターンの形成方法、デバイスの製造方法、電気光学装置、及び電子機器を提供する。

【解決手段】 基板P上に、第1の材料M1と第2の材料M2とを積層しバンク膜Mを形成し、バンク膜Mをパターニングして、第1のバンクB1と第2のバンクB2とが積層されてなるバンクBを形成する。そして、バンクBによって区画されたパターン形成領域ARに、機能液Lを配置して、第1のバンクB1の高さ以下の膜厚を有した膜パターンF1を形成する。その後、膜パターンF1、及びバンクBの上面を含む基板Pの全面に、バリアメタル層F2を成膜する。バリアメタル層F2の成膜後、リフトオフ法により、第2のバンクB2とともに第2のバンクB2上のバリアメタル層F2を除去し、導電膜パターンFを形成する。

(もっと読む)

有機薄膜トランジスタ及びその製造方法、これを備えた有機電界発光表示装置

【課題】有機薄膜トランジスタ及びその製造方法、これを備えた平板表示装置を提供する。

【解決手段】基板上に絶縁膜を形成する段階と、バッファ膜をフォトエッチングして互いに一定間隔で離隔された凹部を形成する段階と、バッファ膜上にソース及びドレインのための電極層を形成する段階と、電極層をフォトエッチングして凹部にソース及びドレイン電極を形成する段階と、ソース及びドレイン電極と上記バッファ膜上に半導体層を形成する段階と、半導体層上にゲート絶縁膜を形成する段階と、ゲート絶縁膜上にゲートを形成する段階と、を含む有機薄膜トランジスタの製造方法である。これにより、半導体層のパターン不良を防止してチャネル領域での短絡現象を防止できる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 デバイスを形成する領域における半導体膜の電位を基板電位と同じにするか、別にするかのレイアウトの自由度を増加させることができる半導体装置を得る。

【解決手段】 半導体基板と、半導体基板上に形成された埋め込み絶縁膜と、埋め込み絶縁膜上に形成された半導体膜と、半導体膜の一部の領域を囲うように形成されたトレンチ分離と、トレンチ分離で囲まれた領域内に形成され、半導体膜及び埋め込み絶縁膜を貫通して半導体基板に接続された基板電位コンタクトとを有する。

(もっと読む)

半導体素子の製造方法

【課題】ゲート抵抗およびゲート間の干渉を減らすことが可能なタングステンゲート電極を有する半導体素子の製造方法を提供する。

【解決手段】半導体基板上にゲート酸化膜11とポリシリコン膜12,14と窒化膜を形成し、これらをパターニングしてポリゲートを形成する。前記ポリゲートの側面にスペーサ18を形成する。全表面上に犠牲窒化膜19を形成し、全面に層間絶縁膜20を形成する。前記窒化膜が露出するように、前記層間絶縁膜20と前記ポリゲート上に形成された犠牲窒化膜19を平坦除去する。前記窒化膜を除去すると同時に、前記犠牲窒化膜19の上部を除去する。前記窒化膜の除去により露出した側面に絶縁膜スペーサ22を形成し、前記犠牲窒化膜が除去された部分21に絶縁膜を充填する。前記窒化膜が除去された部分にタングステンゲート23を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極にシリサイドを使用し、ゲート絶縁膜に高誘電率ゲート絶縁膜を使用する半導体装置において、高誘電率ゲート絶縁膜近傍やゲートエッジに高誘電率ゲート絶縁膜/シリコン界面が生じない半導体装置の製造方法を得ること。

【解決手段】基板上にゲート絶縁膜と多結晶シリコン膜の積層体を形成する工程と、積層体の側壁に第1のサイドウォールを形成する工程と、第1のサイドウォールの周囲に第2のサイドウォールを形成する工程と、積層体の下方のチャネル領域を挟んだ領域にソース/ドレイン領域を形成する工程と、第1のサイドウォールを除去して、積層体と第2のサイドウォールとの間に空隙を生成する工程と、多結晶シリコン膜をシリサイド化させるための金属膜を、空隙を満たすように基板上に形成し、該金属膜を多結晶シリコン膜に拡散させて、多結晶シリコン膜全体をシリサイド膜にする工程と、を含む。

(もっと読む)

ロッド型発光素子及びその製造方法

【課題】素子の光出力を向上させることができるロッド型発光素子及びその製造方法を提供することにある。

【解決手段】

第1極性層の上部に光を放出できる物質がロッドを形成し、このロッドそれぞれを包む第2極性層を形成することにより発光面積を増加させ、素子の内部に拘束されず外部に放出させる光量を増やして素子の光出力を向上させられる。

また、本発明は活性層をナノサイズのロッド構造物で形成して光抽出効率を倍加させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】薄い裏面拡散領域に侵入するスパイキングを防止し、高い耐圧良品率を有する半導体装置およびその製造方法を提供する。

【解決手段】逆阻止IGBTのp型コレクタ領域10とコレクタ電極13の間にp型ポリシリコン層11を形成することで、Alのコレクタ電極からp型コレクタ領域へスパイキングが侵入すること防止し、高い耐圧良品率を得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】簡便な方法により、配線の接続信頼性が向上した半導体装置を提供することができ、さらに、トランジスタの閾値電圧を安定させることにより、電気的特性が安定した半導体装置を提供することができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、シリコン基板に凹部を形成する工程と、前記凹部の内壁を含む前記シリコン基板の表面に第1絶縁膜を形成する工程と、前記凹部を埋め込むとともに前記シリコン基板全面にポリシリコン膜を形成する工程と、前記凹部の外部の前記ポリシリコン膜を酸化するとともに、前記凹部の外部における前記第1絶縁膜の直下に位置する前記シリコン基板の表面領域と、前記凹部内の前記ポリシリコン膜の表面領域とを酸化して第2絶縁膜を形成する工程と、前記第2絶縁膜を除去して、前記シリコン基板の表面を露出させるとともに前記ポリシリコン膜を前記凹部内に残し、埋込ポリシリコン層を形成する工程と、を含む。

(もっと読む)

シリコン化合物の形成方法

【課題】 工程数を可及的に低減し得るとともに低温環境で所望の化合物を形成し得るシリコン化合物の形成方法を提供する。

【解決手段】 チャンバ1の内部に配設するとともにSiとの化合物を形成し得る元素を含む材料で形成した被エッチング部材11を、相対的に高温に保持した状態でハロゲンガスのラジカルを作用させることにより前記材料とハロゲンとの化合物である前駆体24のガスを形成する一方、Si界面を露出させて前記チャンバ1内に収納した基板3の温度を相対的に低温に保持することにより前記前駆体24を前記基板3のSi界面に吸着させ、その後Si界面に吸着させた前記前躯体24に前記ハロゲンガスのラジカルを作用させてこの前躯体24を還元することにより前記材料とSiとの化合物を形成する。

(もっと読む)

二重の完全ケイ化ゲートを形成する方法と前記方法によって得られたデバイス

【課題】各トランジスタタイプの金属ゲート電極の仕事関数を、簡単で能率的に設計でき、トランジスタ又は使われたゲート絶縁体のジオメトリ及び/または大きさとは関係なくコントロール可能な二重の金属ゲートCMOSデバイスを製造する複雑でない製造方法を提供する。

【解決手段】 二重の完全ケイ化ゲートデバイスを製造する方法は、異なる厚さを有する半導体ゲート電極をそれぞれが有する少なくとも2つのMOSFETデバイスを提供するステップと、前記半導体ゲート電極の各々の上に一定の厚さの金属層を積層するステップと、熱処理を遂行するステップとを含み、前記半導体ゲート電極を完全にケイ化するように、各々の半導体厚さを選択し、それによって前記少なくとも2つのMOSFETは異なる仕事関数を有する。

(もっと読む)

5,071 - 5,080 / 6,199

[ Back to top ]