国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,171 - 5,180 / 6,199

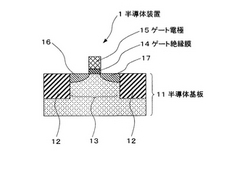

半導体装置およびその製造方法

【課題】ゲート電極の少なくともゲート絶縁膜側をハフニウムと窒素とを含む膜で形成し、そのハフニウムと窒素とを含む膜中の窒素を適性な組成比にすることで、従来から用いられているPoly−Si電極とほぼ同レベルの良好な移動度を得ることを実現する。

【解決手段】半導体基板11上にゲート絶縁膜14を介してゲート電極15を備えた電界効果トランジスタからなる半導体装置1であって、前記ゲート電極15は少なくとも前記ゲート絶縁膜14側がハフニウムと窒素とを含む膜からなり、前記ハフニウムと窒素とを含む膜は少なくとも窒素を含みかつハフニウムと窒素とに対する窒素の組成比が51%以下である。

(もっと読む)

有機薄膜トランジスタおよびその製造方法

【課題】 印刷方法を用いてソース電極及びドレイン電極を形成した微細なゲート長、ソース電極幅、ドレイン電極幅を有する有機薄膜トランジスタを提供する。

【解決手段】 基板、ゲート電極、ゲート絶縁膜、有機半導体膜、ソース電極、ドレイン電極を有する有機薄膜トランジスタにおいて、少なくとも1つ以上の長方形のソース電極108、109およびドレイン電極110、111が間隔を設けて長手方向が平行で、両端部がずれて交互に配列し、前記ソース電極およびドレイン電極の一方の端部は電極連結部102、113を介して電極配線部102、104に接続されており、かつ前記ソース電極およびドレイン電極が設けられている領域はゲート電極103が設けられている領域内に配置されている有機薄膜トランジスタ。

(もっと読む)

ゲート電極積層およびゲート電極積層を用いる方法

【課題】エッチングの容易なポリシリコン−メタル積層で構成されるゲート電極構造を提供する。

【解決手段】少なくとも1層のポリシリコン3と少なくとも1層のポリSi1−xGex材料の層4とを有するゲートコンダクタを備える半導体デバイスの基板上のゲート電極積層構造であり、ポリシリコン3とポリSi1−xGex材料の層4のエッチングにより、終点検出が可能であるため、上記構造を効果的にエッチングすることができる。

(もっと読む)

成膜方法、前処理方法および成膜システム

【課題】 混載デバイスに対しても、前処理によって接合部位の自然酸化膜を確実に除去し、抵抗上昇を生じさせない成膜方法を提供する。

【解決手段】 被処理体に露出したSi含有部表面に金属含有膜を成膜する成膜方法は、Si含有部分の表面を、高周波を用いたプラズマにより物理的に処理する物理的表面処理工程と、プラズマによる処理が施されたSi含有部分の表面を反応性ガスにより化学的に処理する化学的表面処理工程と、化学的表面処理が施されたSi含有部分上に金属含有膜を成膜する成膜工程と、を具備する。

(もっと読む)

金属表面の粗面化処理方法

【課題】チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを溶液に浸漬させて、短時間に腐食量が少なく、あらゆる複雑な形状のチタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを表面粗さ2〜20μmに、歪みなく、粗面化する処理方法を提供することにある。

【解決手段】 チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレスを、弗化水素の濃度0.5〜60重量%の弗酸に増粘剤を加え、粘度1000〜1560000mPa・sにした溶液(液温が0〜60℃)中に浸漬することによって、チタン、チタン合金、アルミニウム、アルミニウム合金およびステンレス表面を粗面化する処理方法を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 半絶縁性GaAs基板を用いたMMICなどの半導体装置において、回路素子と金属電極の間のブレイクダウンを回避する。

【解決手段】 半絶縁性GaAs基板1の裏面に形成された裏面金属電極膜7aが、半絶縁性GaAs基板1とオーミック接合し、バイアホール6の側面に形成された側面金属電極膜7bが、半絶縁性GaAs基板1との界面でオーミック接合した構造とする。

このような構造とすることにより、裏面金属電極膜7a(または側面金属電極膜7b)がエピタキシャル抵抗部3より高電位となるような電界を印加する場合、裏面金属電極膜7a(または側面金属電極膜7b)側から半絶縁性GaAs基板1へホール注入されるのを防止することができる。これにより、エピタキシャル抵抗部3と裏面金属電極膜7a(または側面金属電極膜7b)の間がブレイクダウンするのを回避し、リーク電流が増加するのを防ぐことができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 サリサイドプロセスにおけるシリサイド細線化を防ぎ、設計により近い理想的なシリサイド寸法が確保できるポリサイドゲート電極を有する半導体装置及びその製造方法を提供する。

【解決手段】 基板11上にシリコン酸化膜等のゲート絶縁膜13、ポリシリコン層14を順次形成する。このポリシリコン層14を選択的に除去してポリシリコンパターン141を形成し、側壁として絶縁膜16を形成する。その後、ポリシリコンパターン141の上部を所定厚さT1だけ除去する。これにより、絶縁膜16の上部をポリシリコンパターン141の上面よりも高くする。所定厚さT1は、破線に示すように、ポリシリコンパターン141上に形成しようとするシリサイド層19の側部が絶縁膜16の上部で保護されるような形態となるように設定される。

(もっと読む)

MRAMデバイスの磁気エレクトロニクス素子を覆う導電層への接触方法

誘電領域を覆う記憶素子層を形成する工程を含む磁気エレクトロニクス素子を覆う導電層への接触方法。第1導電層(26)が記憶素子層(18)を覆うように成長する。第1誘電層(28)が第1導電層(26)を覆うように成長し、第1マスキング層(28)を形成するためにパターン化およびエッチング処理される。第1マスキング層(28)を用いて第1導電層(26)がエッチング処理される。第2誘電層(36)が第1マスキング層(28)及び誘電領域を覆うように成長する。第1マスキング層(28)を露出させるために第2誘電層(36)の一部が除去される。第1マスキング層(28)が第2誘電層(36)に比べて早い速度でエッチング処理されるように、第2誘電層(36)及び第1マスキング層(28)が化学エッチング処理される。このエッチング処理により第1導電層(26)が露出する。  (もっと読む)

(もっと読む)

めっき方法及び電子デバイス

【課題】 本発明の目的は、簡単なプロセスで信頼性の向上が図れる、めっき方法を提供することにある。

【解決手段】 めっき方法は、(a)基板10の所定領域に粗化領域24を形成すること、(b)少なくとも粗化領域24の上方に界面活性剤層28を形成すること、(c)粗化領域24の上方であって、界面活性剤層28の上方に触媒層34を形成すること、(d)触媒層34の上方に金属層36を析出させること、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート電極の高さが低くなっても、ゲート電極とソース・ドレイン領域間の短絡の防止を図ることができるように改良された半導体装置の製造方法を提供することを主要な目的とする。

【解決手段】 半導体基板1の上に、ゲート絶縁膜3を介在させて、その上面に第1の絶縁層5が形成されたゲート電極10を形成する。ゲート電極10の側壁および第1の絶縁層5の上面を被覆するように、半導体基板1の上に第2の絶縁層7を形成する。第2の絶縁層7をエッチングバックし、ゲート電極10の側壁にサイドウォールスペーサ11を形成するとともに、素子領域の表面を露出させる。第1の絶縁層5をゲート電極10の上面から除去する。ゲート電極10の上面およびソース・ドレイン領域1bの表面を被覆するように、半導体基板1の表面に高融点金属膜8を形成し、その後アニールし、ゲート電極10の上面およびソース・ドレイン領域1bの表面をシリサイド化し、シリサイド化層9を形成する。

(もっと読む)

5,171 - 5,180 / 6,199

[ Back to top ]