国際特許分類[H01L21/28]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571)

国際特許分類[H01L21/28]の下位に属する分類

電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/28]に分類される特許

5,191 - 5,200 / 6,199

半導体装置の製造方法

【課題】 庇状の断面形状を有するように開口された2層レジスト構造を化合物半導体表面に作成し、導電層を形成する方法において、従来よりも微細加工精度を向上させる方法を提供すること。

【解決手段】 本方法は、半導体表面に下位のレジスト層210を形成する工程と、下位のレジスト層に水溶性樹脂層212を形成する工程と、下位のレジスト層上及び水溶性樹脂層の間に有機不溶性の架橋層211が形成されるように、熱処理を行う熱処理工程と、感光剤を含むレジストを塗布し、架橋層に上位のレジスト層214を形成する工程と、上位及び下位のレジスト層に、露光光線を照射する工程と、上位のレジスト層及び架橋層の一部を現像液で除去し、上位開口を形成する工程と、下位のレジスト層の一部を現像液で除去し、上位開口より広い下位開口を形成する工程と、上位及び下位開口を通じて化合物半導体表面に導電層302を設ける工程とを有する方法である。

(もっと読む)

多層ゲート構造を備える半導体素子及びそれの製造方法

【課題】半導体基板と半導体基板上に形成されたドープされた導電膜を含む半導体素子を提供する。

【解決手段】拡散バリヤ膜がドープされた導電膜上に形成される。拡散バリヤ膜は、非晶質半導体物質を含む。オーミックコンタクト膜が拡散バリヤ膜上に形成される。金属バリヤ膜がオーミックコンタクト膜上に形成される。金属膜が金属バリヤ膜上に形成される。これにより、界面抵抗を所望の範囲内に維持できながら、オーミックコンタクト膜下部の導電体にドープされた不純物が外部に拡散することを効果的に防止できて、多層構造を採用した半導体素子の反転キャパシタンス特性などを向上させることができる。

(もっと読む)

埋込配線の形成方法

【課題】 埋込配線の形成方法に関し、比誘電率の増加をもたらすことなくエッチング残渣を除去するとともに、金属の浸食をもたらすことなく配線露出表面の清浄化を行う。

【解決手段】 下層の配線1を露出させるための開口を伴う配線溝孔エッチング後に、プラズマ励起により配線上の残渣5を剥離処理したのち、大気中に晒すことなく、気体状態の有機系ガス6により配線の露出部表面の清浄化処理を行う。

(もっと読む)

基板の表面処理方法、配線形成方法、配線形成装置及び配線基板

【課題】手短で、高速であり、経済的に微細回路配線を形成することができる基板の表面処理方法、配線形成方法、配線形成装置及び配線基板が提示される。

【解決手段】本発明による基板の配線形成方法は、アルカリ金属化合物を含む表面処理液を吐出方式にてベースフィルム上の配線パターンに応じて選択的に吐出させる基板の表面処理段階、表面処理された配線に応じて金属ナノ粒子を含む導電性インクを吐出させる導電性インクの吐出段階、及び導電性インクが吐出されたベースフィルムを還元性雰囲気中で焼成させる焼成段階を含むことができる。

(もっと読む)

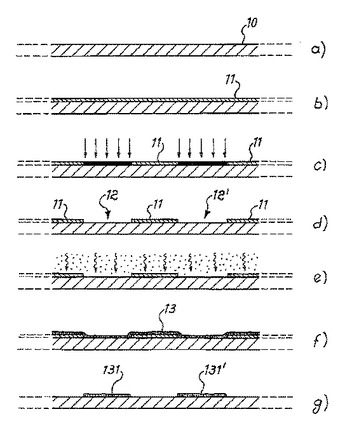

小型ゲッタ蒸着層の形成方法及びそうして得られたゲッタ蒸着層

支持体(10)上に感光性高分子材料の層(11)の形成、高分子層の一部に化学的な変性を引き起こすために高分子層の選択的露光、高分子層の上記のようにして露光された部分又は上記のようにして露光されなかった部分の1方のみを溶媒で除き、そうして高分子層内の空洞(12、12’・・・)の形成、上記空洞の底部および残りの高分子上に陰極析出によりゲッタ材料の薄い層(13)の形成、そして支持体表面の上に少なくとも1つのゲッタ材料蒸着層(131、131’、・・・、20)を残して、第1溶媒で除かれなかった高分子部分を第2溶媒により除く、各工程を含む小型ゲッタ蒸着層の形成方法が記載される。同様に、本発明はこの方法によって得られた小型ゲッタ蒸着層に関する。  (もっと読む)

(もっと読む)

薄膜トランジスタの製造方法

【課題】 蒸着リフトオフという高価な工程を使用せずに、ゲート電極、ソース電極およびドレイン電極の位置合わせ精度を向上させ、ゲート電極に対するソース電極およびドレイン電極の重なりを小さい薄膜トランジスタ製造方法の提供。

【解決手段】本発明の薄膜トランジスタの製造方法は、透明絶縁基板上にゲート電極を形成する工程と、前記透明絶縁基板と前記ゲート電極を覆うようにゲート絶縁膜を形成する工程と、半導体層を形成する工程と、レジストを塗布する工程と、裏露光によって前記ゲート電極に自己整合したレジストパターンを形成する工程と、ソース電極とドレイン電極を形成する工程と、レジストを除去する工程とを少なくとも有する薄膜トランジスタの製造方法であって、前記ソース電極とドレイン電極を形成する工程が、金属ナノ粒子を含む液体を塗布する工程を含む。

(もっと読む)

半導体装置及びその作製方法

【課題】LDD領域を有する微細TFTを、工程数の少ないプロセスで作製し、各回路に応じた構造のTFTを作り分けることを課題とする。また、LDD領域を有する微細TFTであってもオン電流を確保することを課題とする。

【解決手段】ゲート電極を2層とし、下層のゲート電極のゲート長を上層のゲート電極のゲート長よりも長くし、ハットシェイプ型のゲート電極を形成する。この際に、レジストの後退幅を利用して上層のゲート電極のみをエッチングし、ハットシェイプ型のゲート電極を形成する。また、配線と半導体膜のコンタクト部をシリサイド化し、コンタクト抵抗を下げる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程数を低減し、素子特性のばらつきの少ない半導体装置の製造方

法を提供する。

【解決手段】多結晶シリコン層を構成要素として備え、この多結晶シリコン層が

P型多結晶シリコン層5とN型多結晶シリコン層6とを有する半導体装置の製造

方法であって、P型多結晶シリコン層5を形成する工程と、P型多結晶シリコン

層5と一部分が重なるようにN型となる不純物を導入してN型多結晶シリコン層

6を形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を大幅に増加させることなく、P型MOSFETとN型MOSFETとで異なる仕事関数を有する金属ゲート電極を形成する。

【解決手段】N型MOSトランジスタとP型MOSトランジスタとが形成された半導体装置であって、N型MOSトランジスタのゲート電極107nは、ゲート絶縁膜104に接するタングステン膜105nを具備し、P型MOSトランジスタのゲート電極107pは、ゲート絶縁膜104に接するタングステン膜105pを具備し、タングステン膜105nに含有される炭素の濃度が、タングステン膜105pに含有される炭素の濃度よりも低いことを特徴とする。

(もっと読む)

半導体素子の製造方法

【課題】高信頼性の半導体素子を得るために高融点金属、高融点金属からなる合金、高融点金属の珪化物、Ti,Ta,W,Ti−W合金の窒化物からなる膜をコンタクトバリアー層またはゲート電極などに用い、半導体素子のリーク電流を抑える。

【解決手段】ソース−ドレイン領域の接合深さが0.1〜0.3μmである半導体素子のコンタクトバリアー又はゲート電極層がCo珪化物から成る導電体を有する半導体素子の製造方法であり、この導電体のAl含有量が原子数で2×1016個/cm3以下、Co以外の重金属元素の含有量が2×1017個/cm3以下およびアルカリ金属の含有量が1×1016個/cm3以下である半導体素子用高純度導電性膜をスパッタリング法により形成することを特徴とする半導体素子の製造方法である。

(もっと読む)

5,191 - 5,200 / 6,199

[ Back to top ]