国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

81 - 90 / 487

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

電界効果型有機トランジスタ

【課題】ゲート絶縁層に含まれる高誘電体粒子がゲート電極側に偏在していない場合に比べ、低電圧でも駆動する電界効果型有機トランジスタを提供する。

【解決手段】基板と、ゲート電極と、ゲート絶縁層と、チャネル層と、ソース電極と、ドレイン電極と、を有し、前記チャネル層は有機半導体層であり、前記ゲート絶縁層は高誘電体粒子及び絶縁性樹脂を含み、前記高誘電体粒子がゲート電極側に偏在している電界効果型有機トランジスタ。

(もっと読む)

半導体素子

【課題】選択的酸化工程を含む金属ゲートパターンを有する半導体素子を提供する。

【解決手段】半導体素子は、半導体基板、半導体基板上に形成されたポリシリコン層、ポリシリコン層上に形成されたバリヤ金属層、及びバリヤ金属層上に形成されたタングステン層を含み、側壁を有する金属ゲートパターンと、金属ゲートパターンの側壁上に形成されたシリコンオキサイド層と、金属ゲートパターンの側壁のシリコンオキサイド層上に形成されたシリコンナイトライド層と、を含む半導体素子であって、金属ゲートパターンは、90nm未満のゲート長を有し、シリコンオキサイド層は、ポリシリコン層の側壁に接触し、シリコンオキサイド層は、第1部分及び第2部分を含むが、第1部分は、ポリシリコン層の側壁の直接上に位置し、第2部分は、タングステン層の側壁上に位置し、第1部分は、第2部分よりさらに厚いことを特徴とする。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能向上を図ることが可能な薄膜トランジスタを提供する。

【解決手段】有機TFTは、ゲート電極2および有機半導体層6と、それらの間に位置すると共に有機半導体層6に隣接するゲート絶縁層3とを備えている。このゲート絶縁層3は、スチレンおよびその誘導体のうちの少なくとも一方である第1単量体(α−メチルスチレンなど)と、炭素間二重結合および架橋性反応基を有する第2単量体(メタクリル酸グリシジルなど)とが共重合および架橋された材料を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

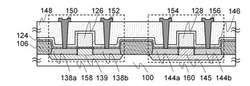

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、ゲート幅方向に断続的に深さが変化する複数のトレンチ162、各複数のトレンチ162の側壁および底面に形成されたゲート絶縁膜120、ゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112およびゲート長方向の他方の側に形成されたドレイン領域113を有するトランジスタを含む。ここで、トレンチ162の側壁の基板102の表面から底面に向かう途中の位置から底面までの下部分におけるゲート絶縁膜120の膜厚が、当該側壁の途中の位置から表面までの上部分におけるゲート絶縁膜120の膜厚よりも厚く、かつ底面におけるゲート絶縁膜120の膜厚以上である。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

有機誘電体を有する有機電界効果トランジスタ

【課題】有機トランジスタの大電流および高速スイッチングを達成するために、ゲート絶縁体材料とその製造方法を提供する。

【解決手段】基板1上に、溶液から有機半導体層3を堆積させる工程、および溶液から低誘電率絶縁材料の層を堆積させて、その低誘電率絶縁材料が有機半導体層3と接触するようにゲート絶縁体2の少なくとも一部を形成する工程を含む有機トランジスタを形成する。低誘電率絶縁材料の比誘電率が1.1から3.0未満までである。

(もっと読む)

化合物半導体素子及びその製造方法

【課題】金合金電極と層間絶縁膜との密着性を向上させる。

【解決手段】化合物半導体素子は、ゲート半導体層10と、カソード半導体層12と、カソード半導体層12上に形成されたAu合金カソード電極14と、ゲート半導体層10上に形成されたAu合金ゲート電極16と、層間絶縁膜18と、カソード電極14及びゲート電極16上のAl配線20と、保護膜22を備える。カソード電極14及びゲート電極16と層間絶縁膜18との界面に、酸化アニール処理により形成され、下地層の構成元素を主成分とする酸化膜15,17を備える。

(もっと読む)

81 - 90 / 487

[ Back to top ]